Place R2807 close to Rapu

Bypass for CPU

3

D

ETM interface: In order to quarantee relaible tracing, traces should be as short as possible and have steady impedance,

2710205

SleepClk: Shield SleepClk trace from every direction in order to avoid crosstalk injected to it.

If Gazoov2.0 is used then it is recommended to use T-filter (47R, 33pF, 47ohm) in Gazoo end

DISPC_PCLK Shield PClk trace from every direction in order to avoid crosstalk problems

shield signals in order to prevent crosstalk

100n

B

MMC Clk: Shield MMC Clk trace from every direction in order to avoid crosstalk problems

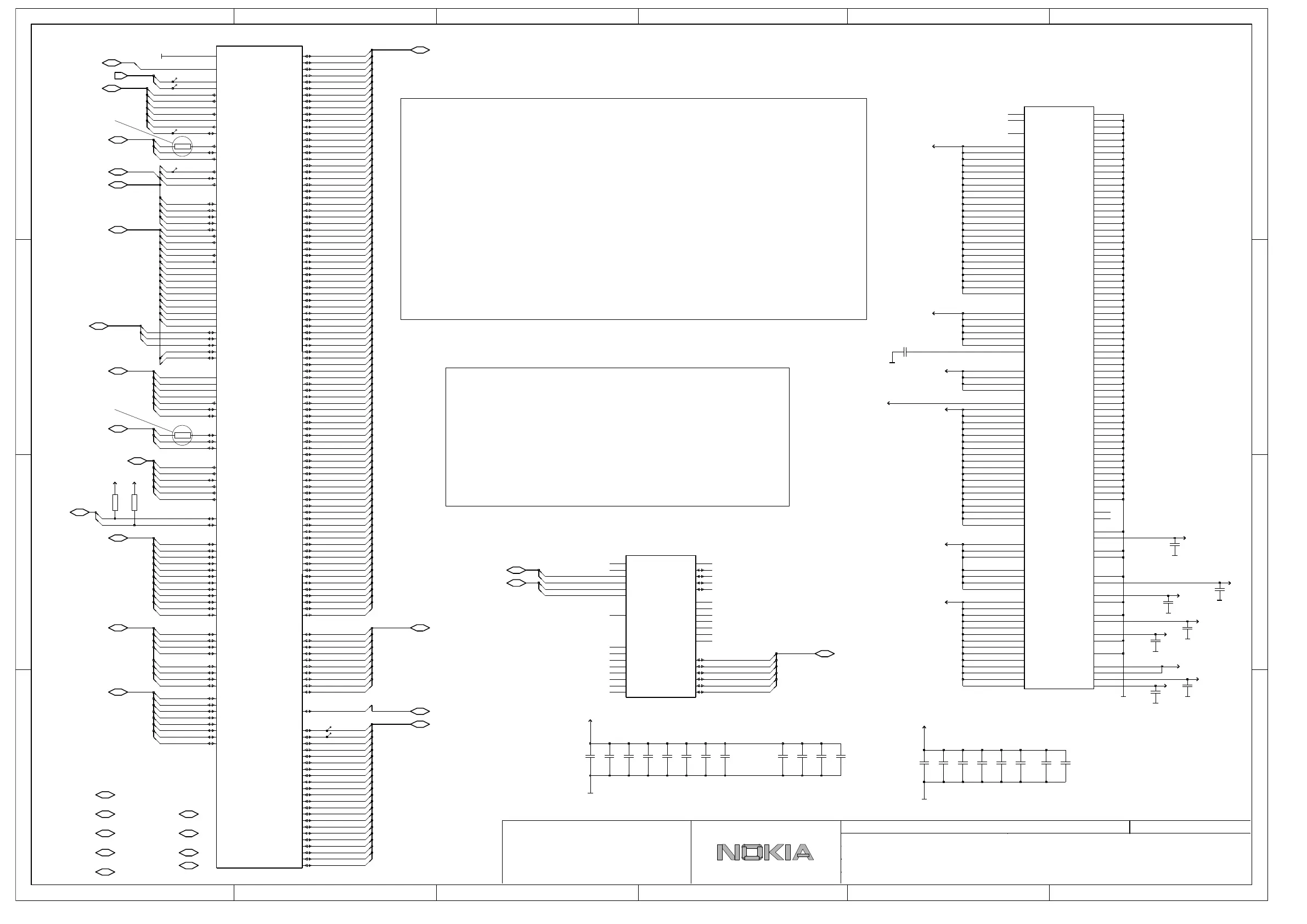

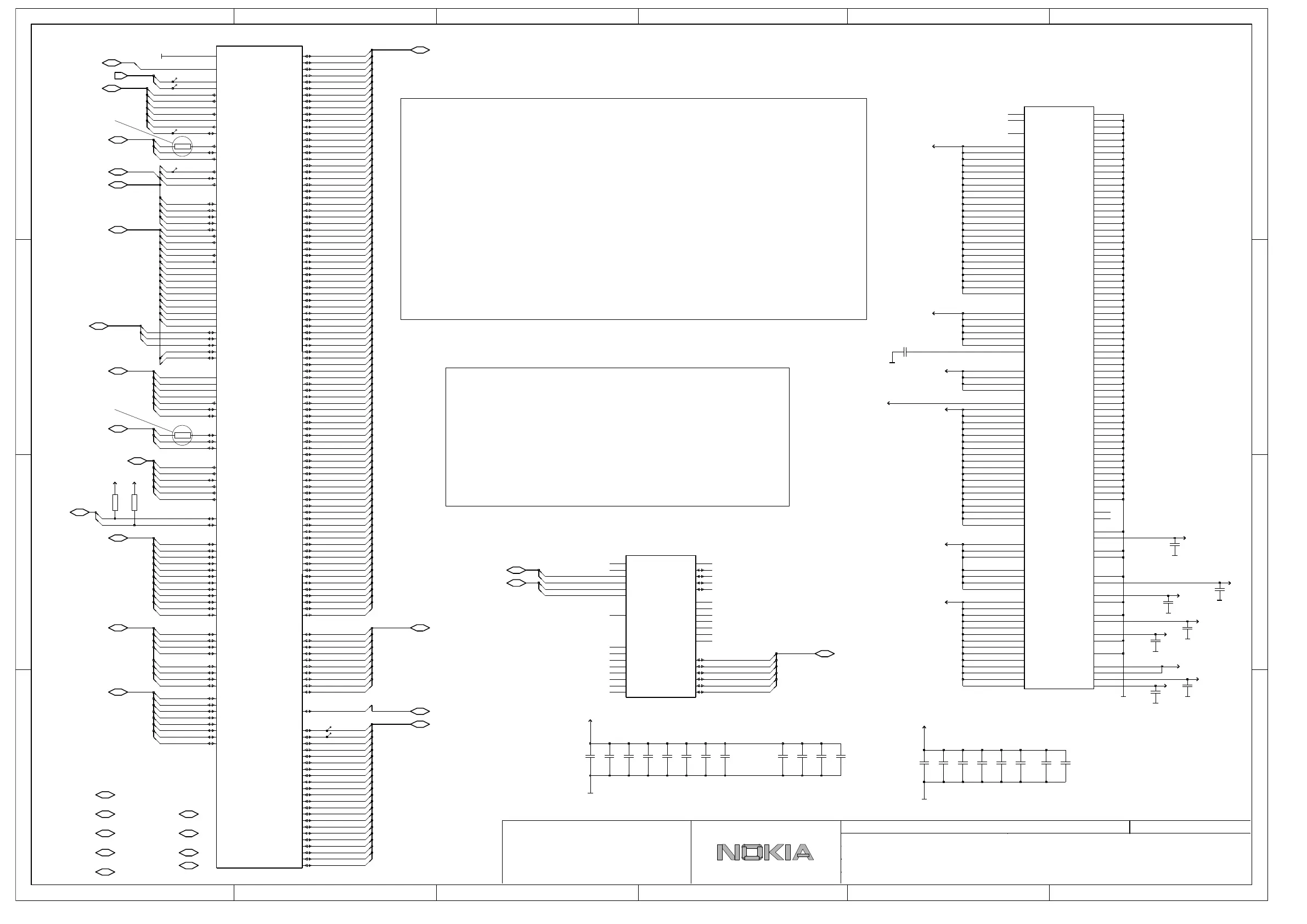

RAPUYAMA1.11 POP

PULL UP’S ONLY FOR

resistors in the beginning of both traces (Values have to be defined case by case with simulations)

If SysClk192 is shared or even used only for one user,

C

INSTRUCTIONS FOR PRODUCT DESIGNS:

SOME GENIOS AND DEDICATED CLOCKS HAS VERY HIGH SLEW RATES WHICH CAN CAUSE SIGNAL INTEGRITY PROBLEMS

SIGNAL INTEGRITY SIMULATIONS AND MEASUREMENTS SHOULD BE DONE TO FOLLOWING SIGNALS:

SYSCLK192

CBUSCLK

AUDIOCLK

SIMCLK’

GENIO72 = DIGIMICCLK

GENIO74 = WLAN_SPI_CLK

INSTRUCTIONS FOR LAYOUT:

it is recommended to use termination in order to avoid signal integrity problems

31 2 6

SysClk192: Shield SysClk192 trace from every direction in order to avoid crosstalk problems

2

HISSI interface: Differential interface, termination resistors (if those are not integrated to display itself)l

100n

5

1

maintain symmetry in routing and match trace lengths between signals and also pairs

6

D

C

B

A

GENIO82 = BT_PCM_CLK

GENIO86&87 = CAMCLK’S

IF PROBLEMS IS SEEN TERMINATION RESISTORS MUST BE ADDED. TERMINATION VALUES CAN VARY FROM 10ohm TO 100ohm

4

2710205 is a master code for 100n x 2 capacitors

4

preferable routing layers are 4 and 5 with minimum trace width in order to achieve 100ohm differential impedance

2710205

RAPU 1.01 AND 1.1

before dividing lines to different components.

5

ULPI interface: It is recommended to place ULPI transceiver as close to RAPU as possible,

Bypass for CPU

Place R2806 close to Rapu

C2809

2 /2 100n

RAPU1.1 Cap

preferable routing layers are 4 and 5 with minimum trace width in order to achieve 100ohm differential impedance

maintain symmetry in routing

A

CCP interfaces: Differential interface, termination resistors as close to RAPU as possible without any stubs,

so that the length of the traces is minimized

If AudioClk is shared from RAPU to both Gazoo and DigiMic then it is recommended to put termination

as close to Display as possible without any stubs,

AudioClk: Shield AudioClk trace from every direction in order to avoid crosstalk injected to it.

C2809

2X100n

1 /2 100n

2X100n

C2813

2X100n

2 /2 100n

15

VCORE

C2830

GND

7

86

9

0

0

7

2u2

VIO

J2804

1

59

41

60

Name

RAPU YAMA POP 1.11

This document is property of Nokia Corporation

THIS DRAWING CONTAINS PROPRIETARY AND CONFIDENTIAL INFORMATION.

UNAUTHORIZED REPRODUCTION OF THIS DRAWING IS NOT PERMITTED.

2

80

GND

12

THIS DRAWING IS PROTECTED BY COPYRIGHT AS AN UNPUBLISHED WORK.

Copyright (C) Nokia Corporation. All rights reserved.

Appr

10

16

34

VRFC

J2816

5

2 /2 100n

C2814

49

10

27

2X100n

2 /2 100n

15

2X100n

12

2

0

GND

3

5

C2811

2X100n

C2822

VRFC

18

12

C2822

2X100n

1 /2 100n /2 100n2

1

0

3

2

VRFC

VIO

68

82

1

9

8

17

J2801

0

53

54

2

22

0

16

8

1

2

52

14

50

7

GND

56R

R2807

R2806

33R

9

2

VIO

2

VIO

16

2

3

4

17

4

VIO

5

7

6

14

61

14

1

21

7

0

14

1

8

47

4

2

20

5

4

16

4

35

6

13

69

3

GND

VCORE

Y4

DISPC_VSYNC

GenIO23

Y5

GenIO22

Y6

DISPC_DATA_LCD7

Y7

Y8

DISPC_DATA_LCD14

DISPC_DATA_LCD0

Y9

33

3

CBusClk

Y15

ETMDa7

Y16

Y17

ETMDa5

ETMCtrl

Y18

GenIO69

Y19

GenIO75

Y20

Y21

GenIO13

GenIO25

Y3

W21

GenIO46

W22

GenIO5

W3

DISPC_DATA_LCD13

DISPC_DATA_LCD16

W4

GenIO3

Y10

GenIO0

Y11

Y13

CCPStrbP1

Y14

CCPStrbN1

U8

DISPC_DATA_LCD10

DISPC_DATA_LCD15

U9

V20

GenIO39

V21

GenIO37

GenIO74

V22

V3

DISPC_DATA_LCD17

V4

DISPC_DATA_LCD11

GenIO11

W20

I2C2SCL

U16

U17

GenIO1

GenIO65

U20U21

EarDataR

GenIO71

U22

U3

DISPC_DATA_LCD5

U4

GenIO8

U7

DISPC_DATA_LCD4

T4

GenIO7

T7

GenIO17

GenIO2

U10

GenIO86

U11

U12

GenIO43

CCPStrbN0

U13

CCPStrbP0

U14

I2C2SDA

U15

R7

GenIO18

T13

GenIO87

GenIO31

T17

EarDataL

T20

PMARP

T21

MicData

T22

T23

GenIO12

T3

GenIO26

GenIO33

R17

GenIO9

R2

GenIO47

R20

PMARN

R21

R22

GenIO48

EMInt1

R23

R3

GenIO14

GenIO20

R4

P17

GenIO76

P21

SleepX

AudioClk0

P22

GenIO35

P23

GenIO10

P3

P4

RFBusClk

P7

GenIO82

GenIO16

R1

N17

GenIO38

N20

PURX

GenIO73

N22

GenIO40

N23

RFBusEn1X

N3

RFBusDa

N4

N7

GenIO79

N9

GenIO50

M2

DRXIN

SIMIOCtrl1

M20

SIMIODa1

M21

ULPIData2

M22

DRXIP

M3

M4

GenIO84

M7

GenIO85

N1

GenIO81

SIMClk1

L20

L21

ULPIData4

L22

GenIO60

L23

GenIO6

VREFP

L3

L4

VREFN

L7

GenIO83

M17

GenIO45

GenIO41

K17

ULPIClock

K20

K21

ULPIDir

K23

GenIO57

RXIP

K3

K4

RXQP

K7

DRXQP

L17

GenIO58

J17

GenIO55

J2

RXIN

ULPIData1

J20

ULPIData0

J21

J22

GenIO34

TXQN

J3

RXQN

J4

DRXQN

J7

GenIO78

G7

RX2

G9

GenIO42

H12

GenIO62

H17

H20

ULPIData3

ULPINxt

H21

H3

TXQP

IREF

H4

G15

GenIO36

G17

GenIO56

RFClkN

G2

ULPIStp

G20

G21

GenIO61

G23

GenIO52

G3

RFClkP

TXIN

G4

E4

HissiData0N

ULPIData6

F20

ULPIData5

F21

F4

TXIP

GenIO51

G11

G12

TxCClk

G13

GenIO29

G14

GenIO64

D3

HissiClkP

D4

HissiData0P

HissiData1P

D5

EMU1

D6

SleepClk

D7

E20

ULPIData7

SMPSClk

E21

E22

GenIO59

ExtSysClkReq

D10

D11

GenIO49

D13

GenIO32

TMAct

D14

GenIO27

D15

D16

GenIO28

D19

GenIO53

D20

GenIO54

C14

TxCDa

C2

HissiClkN

HissiData2N

C3

HissiData2P

C4

HissiData1N

C5

C6

EMU0

TXA

C7

C8

RXDa0

GenIO63

B14

RXDATAClk

B2

GenIO67

B21

SysClk384

B6

GenIO68

B9

C1

TXP

C11

GenIO80

GenIO30

C13

AC10

GenIO72

AC16

SysClk192

AC17

ETMDa6

AC18

ETMClk

AC3

DISPC_ACBIAS

AC9

GenIO21

JTDI

B1

B13

GenIO4

AB18

ETMDa1

AB22

GenIO77

AB3

DISPC_DATA_LCD1

DISPC_DATA_LCD6

AB4

DISPC_DATA_LCD9

AB6

AB7

DISPC_DATA_LCD3

AB9

INT0

JTMS

AC1

AA7

DISPC_PCLK

AA8

GenIO15

AA9

DISPC_DATA_LCD2

AB1

JTDO

CCPDaP1

AB14

CCPDaN1

AB15

ETMDa4

AB16

CBusEn1X

AB17

AA17

ETMDa2

ETMDa3

AA18

ETMDa0

AA19

GenIO70

AA21

DISPC_DATA_LCD12

AA3

AA4

GenIO19

AA5

DISPC_HSYNC

DISPC_DATA_LCD8

AA6

A20

RX1

TXReset

A3

TxCDaCtrl

A8

GenIO24

AA10

AA11

GenIO44

CCPDaP0

AA12

CCPDaN0

AA13

AA16

CBusDa

RAPUYAMA_V1.11_PR_RITSA_BGA401

D2800

JTRSTn

A1

GenIO66

A19

A2

JTClk

56

5

4

51

J2805

J2815

39

38

0

5

4

37

GND

75

0

VIO

1

32

0

1

0

C2808

2X100n

1 /2 100n

62

2

VIO

6

15

0

72

3

6

4

J2800

78

6

13

VCORE

24

9

2

2X100n

1 /2 100n

6

79

7

3k3

C2814

T8

VDDSTACK

T9

VDD5

VCCQ_POP2

U1

VSS

U2

VSS

U23

V23

VDDS3

Y12

VSS

VDD_POP12

Y23

R2805

VDD

VDDSRAMOUT

R8

R9

VDD5

T1

VDDS_1_4

T10

VDDRAM

VSS

T11

T12

VDDSTACK

VSS

T14

VDD

T15

T16

VSS

T2

VDDS1

P2

VSS

P20

VSS

VDD5

P8

VSS

P9

VSS

R10

R11

VDD

VDD

R12

VDD

R13

R14

VDD

VDD

R15

R16

VDD3

M16

M8

VDDSTACK

VDD5

M9

N15

VDD3

VSS

N16

VDDS_1_1

N2

VDDS8

N21

N8

VDD5

P1

VCCQ_POP1

VSS

P15

VSS

P16

K22

VDDSTACK

K8

K9

VSS

L1

VCC_POP3

L15

VSS

L16

VDD3

VSS

L2

VDD5

L8

VSS

L9

M1

VSSASUB

VDD3

M15

VSS

J13

J14

VSS

J15

VDD3

J16

VDD3

VDD4

J8

VDDSTACK

J9

VDD_POP11

K1

K15

VSS

K16

VSS

VSS

K2

VSS

H16

VSS

H2

VSS

H22

H23

VDD_POP10

H7

VDDARX

H8

VSS

VDDA18V1

H9

J1

VDDATX

J10

VDD2

VDDSTACK

J11

VDD2

J12

F3

VSS

G1

VDDS9

G10

G16

VSS

VSS

G8

H1

VDD_POP13

VSS

H10

H11

VSS

VDDRAM

H13

VDD3

H14

VDD3

H15

VSS

VDDS9

D9

E1

VDD_POP9

VSSAPLLStack

E2

VDDS12

E23

VDDAPLLStack

E3

E5

VSSARX

F1

VDDA_ACS

VSSA_ACS

F2

VSS

F22

F23

VDD_POP8

VSSATX

C22

C23

VDD_POP7

VSS

C9

VDDS_1_3

D1

VDDA18V2

D12

D17

VSS

D18

VDDS5

D21

VSS

D22

VSENSE

D23

VDDS12

VDDS9

D8

B5

B7

VSS

VSS

B8

VSS

C10

C12

VDDS10

VSS

C15

VSS

C16

VSS

C17

VDDS5

C18

C19

VSS

C21

VSS

VSS

VCC_POP2

AC8

B10

VSS

VSS

B12

VSS

B15

VSS

B18

VDDS6

B19

VSS

B22

IFORCE

B23

B3

VDDA

VSS

B4

VSSA

VSS

VSS

AB5

VSS

AB8

AC11

VPP_POP

AC12

VSSRX2

AC13

VCC_POP1

AC15

VDDS7

AC4

VSS

AC5

VCCQ_POP4

AC6

VDDS2

AC7

VDDS2

A7

A9

VDDS_1_2

VCCQ_POP3

AA1

VSSRX1

AA14

AA15

VDDS7

VSS

AA2

VSS

AA20

VSS

AA22

VDD_POP12

AA23

VSS

AB10

VSS

AB13

AB2

VSS

A13

VDD_POP5

A15

A16

VDDS6

A17

VDDS6

A18

VDD_POP6

A21

VDDS6

VPP2

A22

A23

VPP1

A4

VDD_POP1

A5

VDDS4

VDD_POP2

70

6

0

0

D2800

RAPUYAMA_V1.11_PR_RITSA_BGA401

VDD_POP3

A10

A12

VDD_POP4

VCORE

2X100n

C2820

1 /2 100n

25

4

VIO

1

1

5

6

57

29

76

40

58

4

77

8

36

44

74

W2

W23

SDRAD13

Y1

CE1MMX

FlsCS0X

Y2

SDRAD14

Y22

/2 100n2

C2806

2X100n

C20

D2

SDRLDQS

G22

NC

J23

SDRCKE2

SDRXCS2

M23

V1

FlsWEX

FlsOEX

V2

FlsADVX

W1

FlsClk

AC20

MMCDa0

AC21AC22

NC

NC

AC23

B11

SDRCLKX

B16

NC

SDRLDQS2

B17

B20

SDRUDQS2

NC

AB12

MMCDa1

AB19

AB20

MMCClk

AB21

MMCCmd

AB23

NC

SDRAM_TEMP_SENSE

AC14

AC19

MMCDa2

AC2

NC

MMCDa3

RAPUYAMA_V1.11_PR_RITSA_BGA401

D2800

SDRCLK

A11

A14

NC

SDRUDQS

A6

FlsRstX

AB11

FlsWaitX

55

3

VIO

28

7

2X100n

2 /2 100n

C2808

63

1 /2 100n

C2810

2X100n

2 /2 100n 1 /2 100n

2X100n

C2810

11

2

8

45

46

2X100n

C2813

1

GND

9

17

13

11

87

13

19

30

5

4

0

1

73

0

2X100n

C2821

VIO

26

5

2X100n

2 /2 100n

84

83

/2 100n1

GND

15

3

C2819

66

67

0

/2 100n1

2X100n

C2819

C2800

100n

/2 100n2

C2803

2X100n

5

31

4

20

/2 100n1

2X100n

C2803

81

0

6

3

/2 100n1

2X100n

C2806

64

GND

10

3k3 R2804

1 /2 100n

1

2

1

19

10

1

65

3

6

21

2X100n

C2811

100n

C2802

C2821

2X100n

2 /2 100n

8

10

C2801

100n

11

85

4

GND

VIO

GND

6

71

GND

1

23

5

7

VIO

48

43

42

18

7

11

2

16

/2 100n2

C2820

2X100n

"Note"

"Note"

"Note"

"Note"

"Note!"

"Note"

"Note"

"Note!"

SDRAM_CTRL(17:0)

SDRAM_AD(15:0)

MEMCONT(9:0)

"Note!"

"Note"

"Note"

"Note"

"Note"

"Note"

"Note"

"Note"

"Note""Note"

I2C2(1:0)

DIG_AUDIO(20:0)

"Note!"

INT_SIM(5:0)

JTAG(6:0)

PUSL(15:0)

"Note!"

CBUS(3:0)

RFCTRL(11:0)

RFCONV(20:0)

TXC(2:0)

TXP

"Note!"

INT_MMC(13:0)

SDRAM_CTRL(17:0)

I2C0(1:0)

EMINT(3:0)

VISSI(27:0)

ETM(20:0)

GENIO(99:0)

"Note"

"Note"

"Note"

SDRAM_AD(15:0)

SDRAM_DA(31:0)

EXTADDA(31:0)

SDRAM_CTRL(17:0)

SDRAM_BA(1:0)

MEMCONT(9:0)

INT_MMC(13:0)

RFCLK(1:0)

HISSI(8:0)

"Note!"

"Note"

"Note"

"Note"

"Note"

"Note"

"Note"

"Note"

CCP(30:0)

"Note"

"Note"

"Note"

"Note"

"Note"

"Note"

"Note"

"Note!"

USB(20:0)

"Note"

"Note"

"Note"

"Note"

Loading...

Loading...