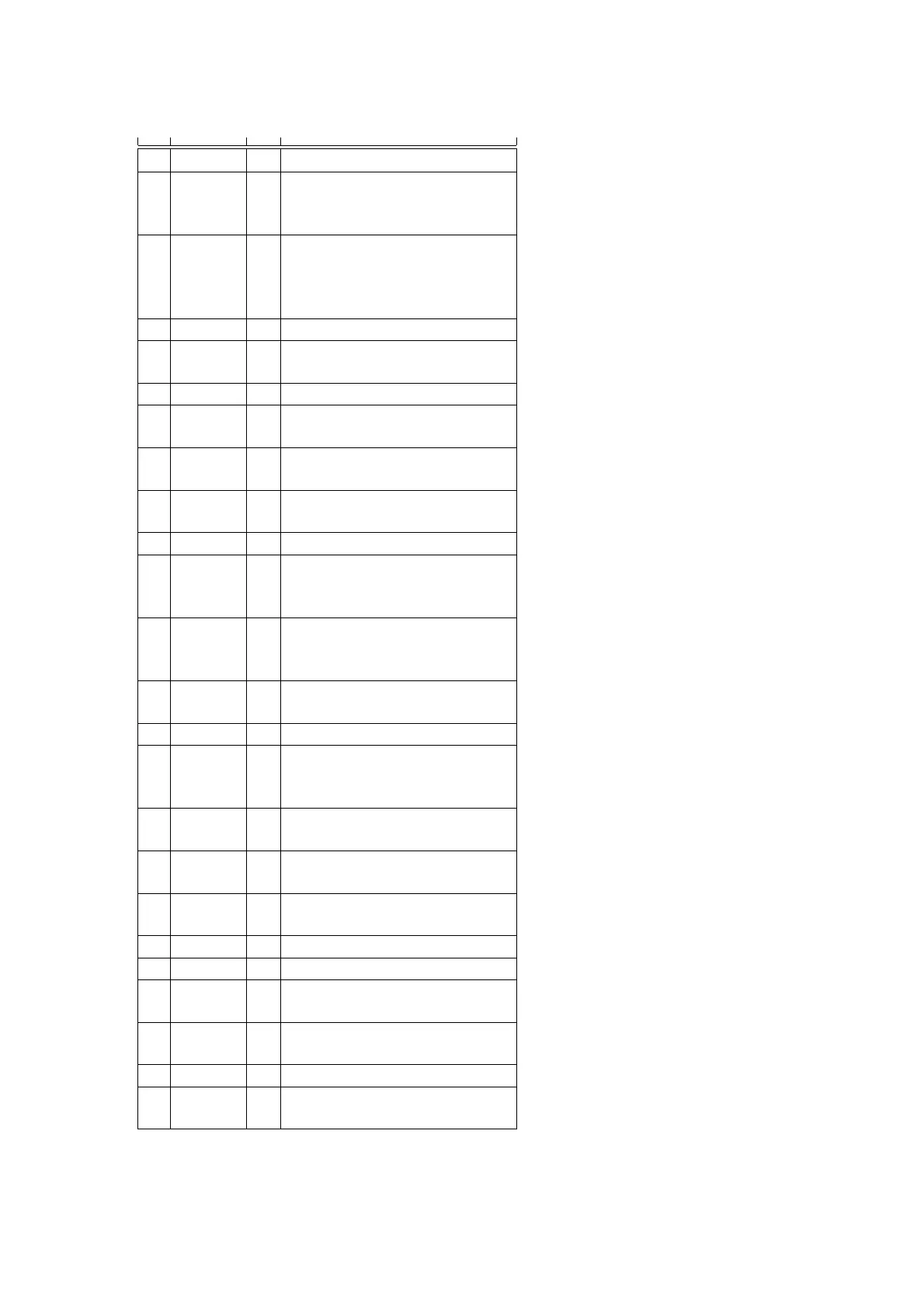

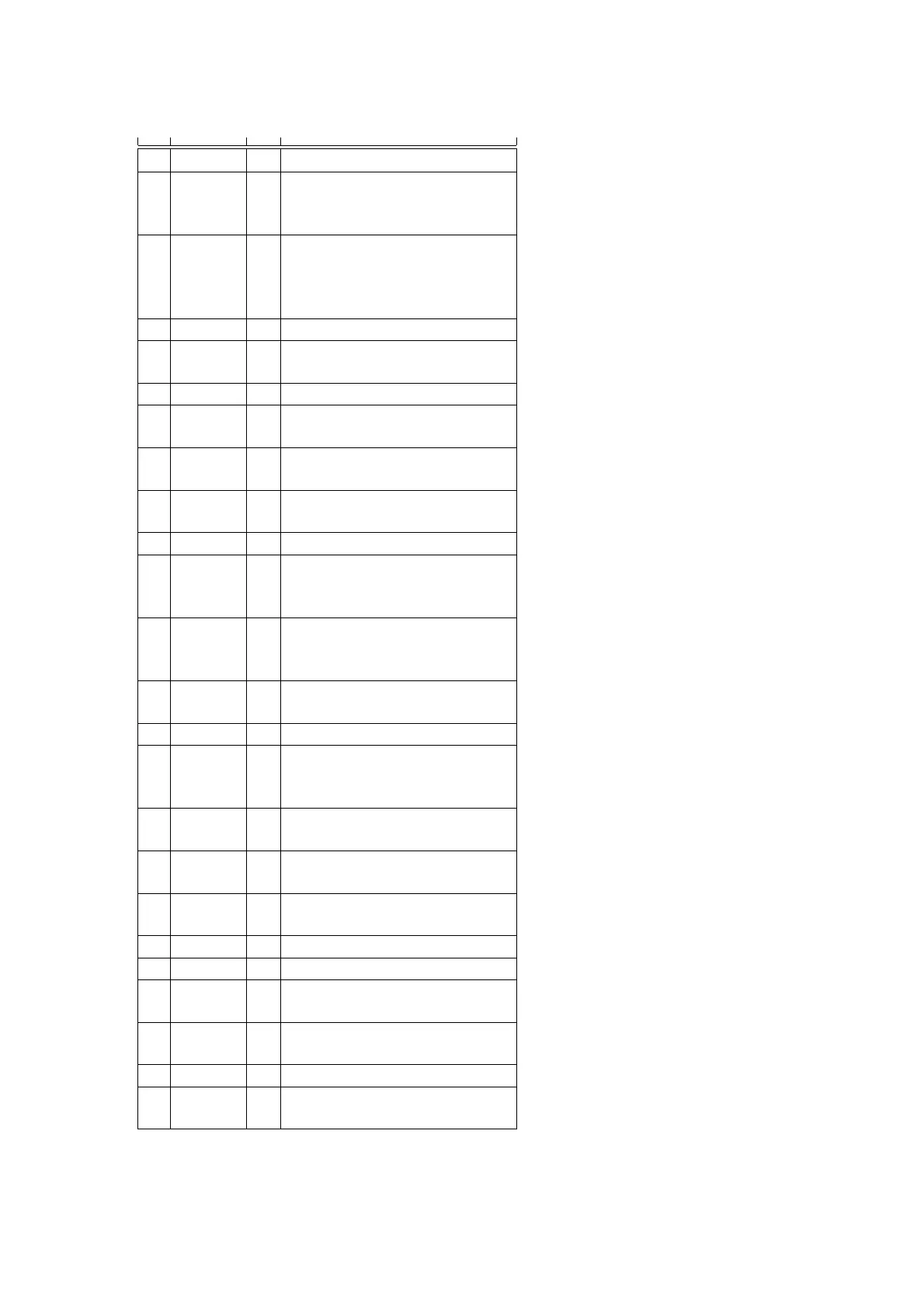

No. Mark I/O Function

53 PCK - PLL extraction clock output

(fPCK = 4.321 MHz during

normal playback)

54 VCOF2 I/O VCO Loop filter for 33.8688

MHz conversation terminal for

16.9344 MHz crystal mode,

must use other circuit

55 SUBC O Sub-code serial data output

56 SBCK I Clock input for sub-code serial

data

57 VSS I GND

58 X1 IN I Crystal oscillating circuit input

(f = 16.9344MHz)

59 X2 OUT O Crystal oscillating circuit input

(f = 16.9344 MHz)

60 VDD I Power supply input (for

oscillating circuit)

61 BYTCK - Byte clock output

62 /CLDCK - Sub-code frame clock signal

output (fCLDCK = 7.35 kHz

during normal playback)

63 FCLK - Crystal frame clock signal

output (fCLK = 7.35 kHz,

double = 14.7 kHz)

64 IPFLAG - Interpolation flag output (“H” :

Interpolation)

65 FLAG - Flag output

66 CLVS - Spindle servo phase

synchronizing signal output

("H" : CLV, "L" : rough servo)

67 CRC - Sub-code CRC checked output

(“H’ :OK, “L” :NG)

68 DEMPH - De-emphassis ON signal

output (“H” :ON)

69 RESY - Frame re-synchronizing signal

output

70 IOSEL I Mode Switching Terminal

71 /TEST I Test input

72 AVDD1 I Power supply input (for analog

circuit)

73 OUTL O Left channel audio signal

output

74 AVSS1 I GND

75 OUTR O Right channel audio signal

output

37

Loading...

Loading...