Circuit Descriptions

EN 37TPL16.1E LA 7.

2016-Sep-23

back to

div.table

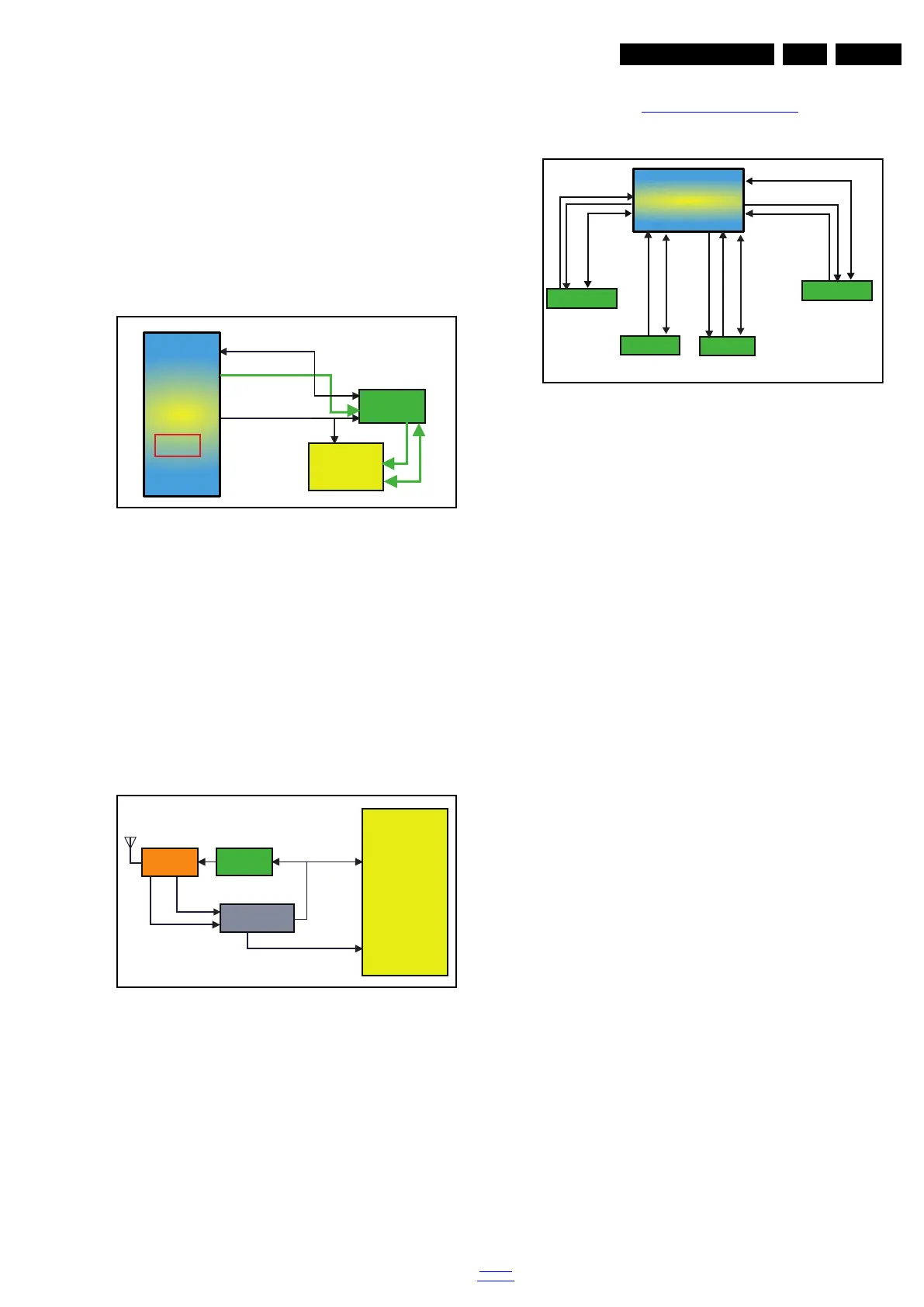

7.4.2 DTV T2 reception

The Front-End for DVT part consist of the following key

components:

• TUNER EUROPE SUT-RE231ZN

• SCALER MT5596LGIJ HSBGA-757

• DEMODULATOR CXD2837ER-T4 VQFN 48 for T and S

models

Below find a block diagram of the front-end application for DTV

part.

Figure 7-7 Front-End DVB-T2 DTV block diagram

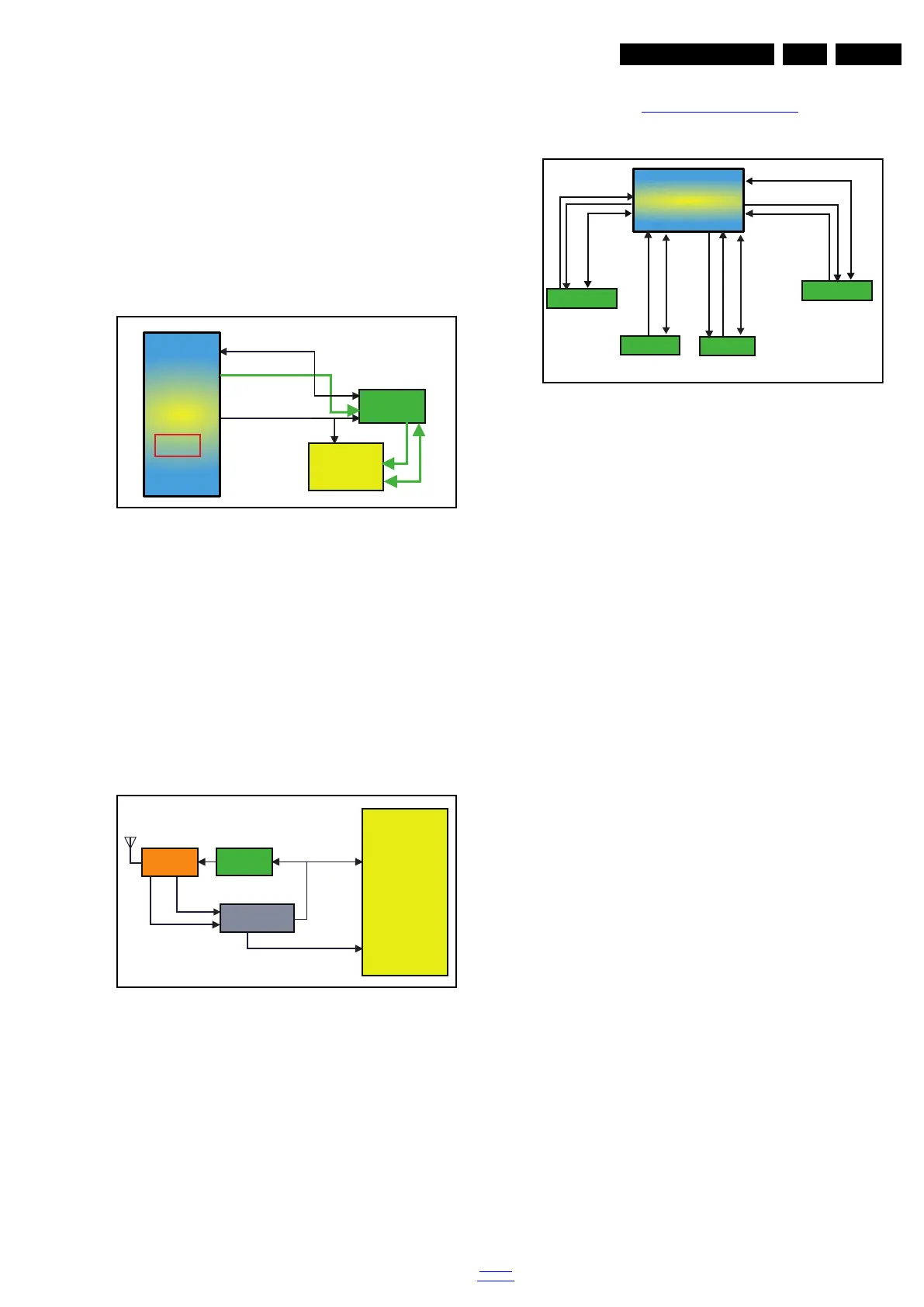

7.4.3 Front-End DTV-S2 reception

The Front-End for ISTB part consist of the following key

components:

• TUNER EUROPE SUT-RE231ZN

• SCALER MT5596LGIJ HSBGA-757

• DEMODULATOR CXD2837ER-T4 VQFN 48

Below find a block diagram of the front-end application for DTV

part.

Figure 7-8 Front-End DVB-S2 DTV block diagram

7.5 HDMI

Refer to figure 7-9 HDMI input configuration for the application.

Figure 7-9 HDMI input configuration

The following HDMI connector can be used:

• HDMI 1: HDMI input ( TV digital interface support

HDMI1.4/HDCP1.3) with digital audio/PC DVI input/ARC

• HDMI 2: HDMI input ( TV digital interface support HDCP)

with digital audio/PC DVI input/ARC

• HDMI 3: HDMI input ( TV digital interface support

HDMI1.4/HDCP1.3) with digital audio/PC DVI input/ARC

• HDMI 4: HDMI input ( TV digital interface support

HDMI1.4/HDCP1.3) with digital audio/PC DVI input/ARC

• +5V detection mechanism

• Stable clock detection mechanism

•HPD control

• Sync detection

• TMDS output control

• CEC control

• ARC control

•MHL control

7.6 Video and Audio Processing -

MT559

6LGIJ

HSBGA-757

The MT5596LGIJ HSBGA-757 is the main audio and video

processor (or System-on-Chip) for this platform. It has the

following features:

• worldwide multi-standard analo g TV demodulator

• ATSC /DVB-T /DVB-C/DTMB demodulators

• Ture 120HZ Full HD MJC

• Power CPU core

• 3D graphic support OpenGL ES 1.1/2.0

• A muti-standard video decoder

• A transport de-multiplexer

• One HDMI 2.0 receiver with 3D support

• MHL2.0& Standby charging

• 2D/3D converter

• Rich format audio codec

• Local dimming (LED backlight)

• Ethernet MAC+PHY

•TCON

• Panel overdrive control

• Four-link LVDS, mini-LVDS,V-by-one, EPI

The MT5596L family provides consumers with aUHD 60HZ

direct drive.

The MT5596L family consists of a DTV front-end demodulator,

a backend decoder and a TV controller and offers high

integration for advanced applications. It integrates a transport

de-multiplexer, a high definition video decoder, an audio

decoder, a four-link LVDS transmitter, a mini-LVDS transmitter,

a V-by-one transmitter, an EPI transmitter, and an

NTSC/PAL/SECAM TV decoder with 3D

combfilter(NTSC/PAL).

IF

IF-AGC

TS DATA

RF_AGC

MT5596L

DECODER

CXD2837ER

IF_AGC

SUT-RE231ZN

I

2

C

I

2

C

I

2

C

20110_204.eps

TS DATA

IP/IN/OP/ON

Tuner I2C

Tuner I2C

System I2C

MT5596L

LNB power

S2 Demond

CXD2837ER

S2 tuner

S2 function

20110_205.eps

20110_206.eps

MT5596L

HDMI2

HDMI1

HDMI4

CN502

CN504

CN501

RX

RX

TX

TX

TX

RX

I

2

C

I

2

C

I

2

C

HDMI3

CN503

RX

I

2

C

Loading...

Loading...