Rev. J 08/16

31

TOP252-262

www.power.com

Quick Design Checklist

In order to reduce the no-load input power of TOPSwitch-HX

designs, the V-pin (or M-pin for P Package) operates at very

low current. This requires careful layout considerations when

designing the PCB to avoid noise coupling. Traces and

components connected to the V-pin should not be adjacent to

any traces carrying switching currents. These include the drain,

clamp network, bias winding return or power traces from other

converters. If the line sensing features are used, then the sense

resistors must be placed within 10 mm of the V-pin to minimize

the V pin node area. The DC bus should then be routed to the

line sense resistors. Note that external capacitance must not

be connected to the V-pin as this may cause misoperation of

the V pin related functions.

As with any power supply design, all TOPSwitch-HX designs

should be verified on the bench to make sure that components

specifications are not exceeded under worst-case conditions.

The following minimum set of tests is strongly recommended:

1. Maximum drain voltage – Verify that peak V

DS

does not

exceed 675 V at highest input voltage and maximum

overload output power. Maximum overload output power

occurs when the output is overloaded to a level just before

the power supply goes into auto-restart (loss of regulation).

2. Maximum drain current – At maximum ambient temperature,

maximum input voltage and maximum output load, verify

drain current waveforms at start-up for any signs of trans-

former saturation and excessive leading edge current spikes.

TOPSwitch-HX has a leading edge blanking time of 220 ns

to prevent premature termination of the ON-cycle. Verify that

the leading edge current spike is below the allowed current

limit envelope (see Figure 53) for the drain current waveform

at the end of the 220 ns blanking period.

3. Thermal check – At maximum output power, both minimum

and maximum voltage and ambient temperature; verify that

temperature specifications are not exceeded for

TOPSwitch-HX, transformer, output diodes and output

capacitors. Enough thermal margin should be allowed for

the part-to-part variation of the R

DS(ON)

of TOPSwitch-HX, as

specified in the data sheet. The margin required can either

be calculated from the values in the parameter table or it can

be accounted for by connecting an external resistance in

series with the DRAIN pin and attached to the same heat

sink, having a resistance value that is equal to the difference

between the measured R

DS(ON)

of the device under test and

the worst case maximum specification.

Design Tools

Up-to-date information on design tools can be found at the

Power Integrations website: www.power.com

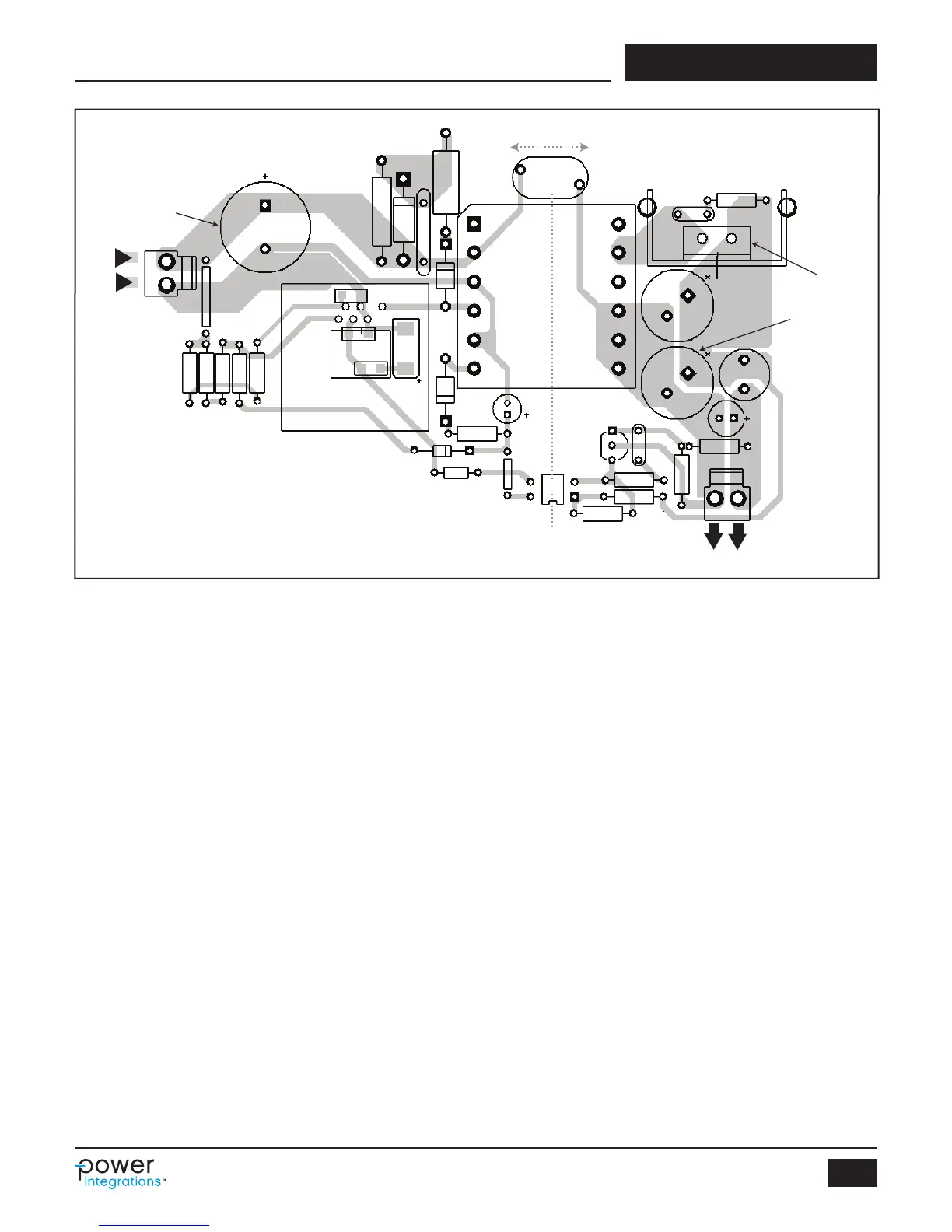

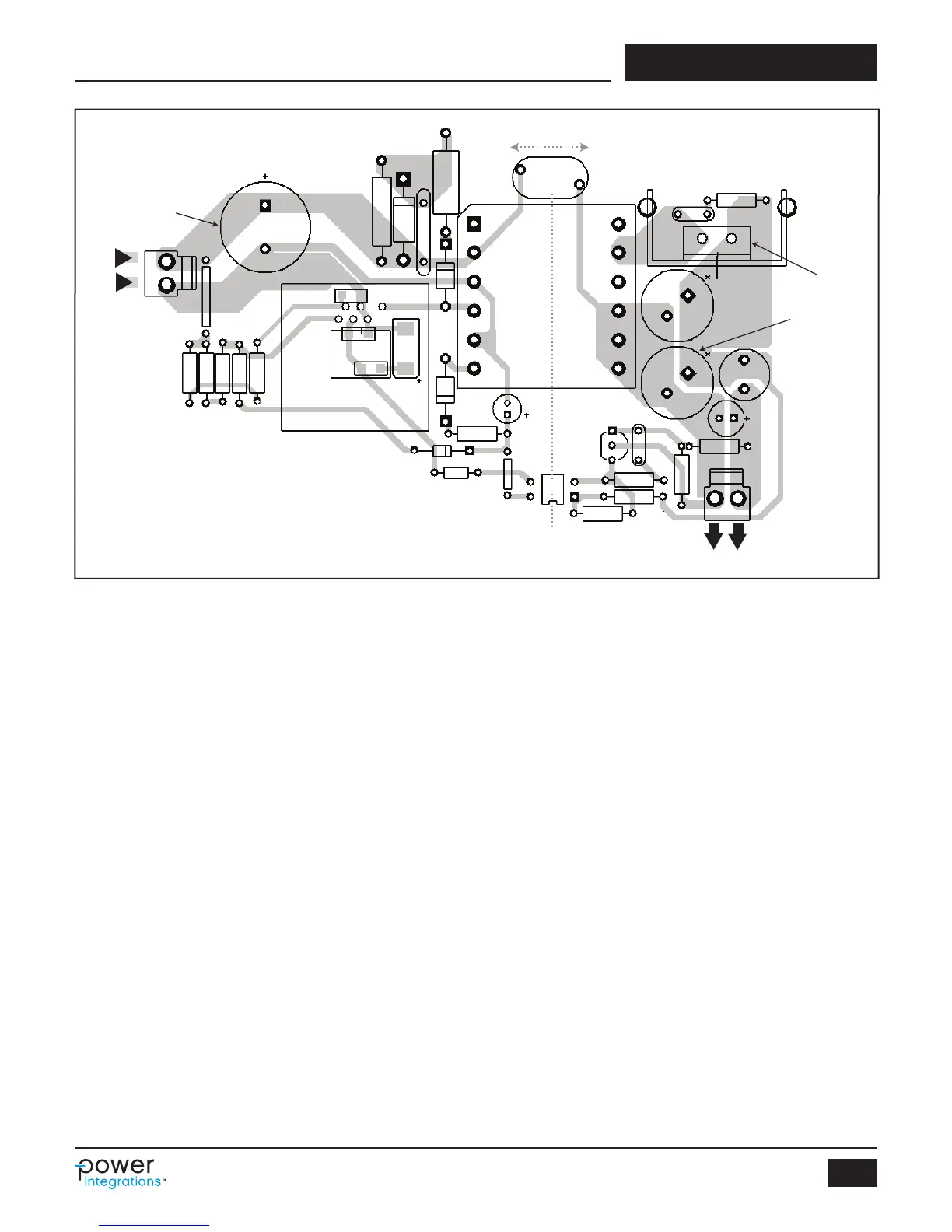

Figure 50c. Layout Considerations for TOPSwitch-HX Using L Package and Operating at 132 kHz.

+-

DC

Out

+

-

HV

PI-5216-091508

Y1-

Capacitor

C7

Isolation Barrier

Output

Rectier

J1

R11

R3

R4

R5

R14

JP1

C4

R6

D5

C6

R7

VR1

R22

C8

R8

U1

C9

D6

C10

R10

VR2

R9

JP2

R15

R13

R17

U4

C21

R21

D8

C16

R12

HS2

HS1

C17

J2

R20

C19

L3

C18

T1

Output Filter

Capacitor

Input Filter

Capacitor

Note: Components U1, R8, C8, C9 and R22

are under heat sink HS1.

Transformer

X

F D

Y

S

C

U2

Loading...

Loading...