IBusy)

-BSY

(Select)

-SEL

(Control/Data)

-C/D

(Input/Output)

I/O

IReQuest)

-REG

HANDSHAKE

IAcknowledge)

-ACK

Note:

(At

tent

i onl

-ATN

-AST

and

-ATN

are

IMessagel

-MSG

shown

de-asserted

Ihigh)

IResetl

-RST

(Data

bitl

DB

(7-0.

PI

Note'

BUS

SET

DELAY

Maxl_

tiM

for

an

SCSI

device

to

Issert

BSY

and

ita

SCSI

10

bit

on

the

detl

bita

Ifter

't

detecta

Bua

Free

Phase

BUS

fREE

DELAY

Mini.,.

tlae

that

an

SCSI

device

ahall

weit

fro.

Its

detection

of

Bus

Free

Phase

until

Its

assertion

of

BSY.

BUS

ClEAR

DELAY

Maxi.,.

tlae

for

an

SCSI

d.vlce

to

atop

driving

all

bus

signals

after

Bus

Free

Phase

Is

detectea

or

SEL

recl.ved

fro.

an SCSI

a.vice

during

arbitration.

S

SETTLE

...

0_EL_A_Y_,-J../2

deskew

delays

___

~---

Target

asserts

BSY

II

'----Bus

Settle

Deley

I I

-BSY

I

I~----~---+-r--------------------~----------~----------~~---------+----~--------~------~~--------

+-~

I

r--systells

with

1_

1

_.

no

arbitratiorn~~+-

______________________

~

________

-T

_____________

~~~r-

________

~

____

~~--------+-------~----------~~~----~--------SEL

I"

sUrt

here

(

I I

J--t--------r-------

-C/O

r--+----~-------

-

1/0

r+---t--------f--.,.---

-REG

)---t-----~-------

-ACK

ATN

,-4-------;-------MSG

---+-----+------------;-;-+-----r-----~--_;_+----------------------r_--------~----------~~~~~~~~~~~------~~~----~--------~--r_----~-------RST

--~,------V-~~~--~--~V71n~1~t.~.t~o~r7.1D~,7T.~rO=.~t7.1D~---r----'r.-

~,r_----

__

~~;_--;_----------~~~~~~~~~~~~~~--~~~~.r_--~,------~~r-~~r-~--~----

-4r------DB(7-0.PI

/)

I I I

First

\ \ I :

/ I

Initiator

tries

I

II

Initiator

has

!Jus:

1st

LAST

:

data

first

data

Status

byte'

Message \ :

Bus

is

\

/

BUS

FREE

I

to

get

ous I

nd

I

ts

T g t

read

I . t . h

I)

\

byte)1

I

released

\,

/

PHASE

I I I a

se

ec

ar

e I

COMMAND COMMAND

I I

WCl

e

perlp

era

Target

)

DB

(7) -Most

SIgnIfIcant

bit

//

/ : I I

BYTE BYTE

I

peripheral

I

Target

'requests'

data

'requests'

I

ITarget

'reQuests,1

I ,

-HIghest

prIorIty

lD

for

arOltratlon//

I I

Target

'reqUests'

I I

transfer

w,th

,nitlato

r

initiator

to

I I

initiator

to

take

l

II

\

(,

/ I I I I

take

status

I I

~essage

I I )

Note:

DB

(P)

- Data

parity

loddl

Par1ty

Is

not

valid

du~ing

arbitration.

//

I I

command

from I I I I I I I

SEL

and r : I :

init,

atDr

.:

:

I:

: I I

BSY

are

~

----j

r

STATUS

PHASE

~

MESSAGE

r-

BUS

----...J

both

false

~

ARBITRATION

~

c==

SELECTION

=-==:J.

r-.

CO~MAND

PHASE

---,----1 I

CATA

PHASE

I

r:=

--<!==

PHASE

~

r--

FREE

---I

for

at

least

J---

PHASE

PHASE

----'

I I

I--

(Ending

Statu.)

==1

t--

---;

t--

-.---J

one

Bus

~

---j

\ \ I I I I

t--

--j

r--

PHASE

I

Settle

r-

Implementation

of I

During

this

phase

the

\

.--

The

Target

asserts

I I

DATA

IN

PHASE:

Read

PerIpheral.

I

f--

Target

I

~Target

I

f--Target

,

Delay I

this

phasee

is

a I 110

signal

is

\ I

CIO

and

deasserts

110 I I I

requests

that

a I I

requests

I I

deasserts

BSY

"

I

system

option

I

deasserted

'to

\ I and

MSG

for

all

of

the

f--

Data

is

to

be

sent

from

Target

to

I I

status

byte

be I I ..

essage

I I

to

indicate

t~at\

I I

distinguish

this

Phase

) I

handshakes

of

this

phase

I

Initiator

I

sent

to

the

I I

byte

isl

to

be I I

the

bus

Is

I

,---

At

least

one Bus I

~~~:e

the

Reselection

: I I : I

Initiator

I I

sent

from I I

available

for

I

I

~~~:

~~~~y

on~u~u~O

:

NON-ARBITRATING

I

~

The

transfer

is

from

f--

Target

asserts

110.

deasserts

C/O and I :

Target

asserts

II

:

i~~~~;t~~,

::

~~~~:quent

II

:

Set

Delay

aftee

Bus

I

SYSTEMS:

In

systems

I I

init,ator

to

Target

I

MSG

during

the

REG/ACK

handshake of I I

C/O

and I/O I I I I

I

~~:~

~:~:~t:~s

The

I

with

the

Arbitration

I I I

th.s

phase.

I r

=~~

~~~~~:rts

I

t-Terget

asserts

I r

Initiator

releasef

I

Initiator

asserts

BSY

I

~:~:m~~~ed

atler

:

L,

pH~~OCSEDHUA~~..

l--

HANDSHAKE

PROCEDURE

: I

th

h d h k :

~~g'

~~~in~nd

: I

all

bus

S~gnals

I

:

~~~i~;sI~w~liC~~

the:

detecting

the

Bus

free

1

M

.'

MC

I

I:

Of\h~~

~h:S:.

I

the

REG/ACK

I I

~~;~~no!la~s

I

I

data

bus I

Phase

the

Initiator

I

~

~~~T~~;ein~~~:~~~

L

The

Target

first

drives

data

17-0P)

I I I

haneshake

(5) I I

~~~~~e~SY

:

L-

The

Initiator

waits

I

~~!t~u:

~~~!~U~e~:y.

I

drives

data

(7-0.P)

to

:

~~a!~e~~ed~:!~:~

~::~:sp7~!t:

~~ble

: I Only one

byte

I

of

this

phase.

I

continuously

I

I

an

Arbitration

Delay I Then

it

asserts

the

data

;~~~~

~~s;~:~tv~~~es.

I skew

delay

then

asserts

REO

Data I I of

status

is

~The

message I

false

for

a

BUS

I

I

then

examines

the

I

~~~i~~~\~~;~a~~~

10

bit

deskew

delay

plus

a I

t7-0.PIshall

remain

valid

until

ACK

I I

transferred.

I

byte

could

I

Settle

Delay I

I

data

bus.

If

•

higher

I

th

T

t'

10

b'

t

cable

skew

delay

and I

is

t~ue

at

the

Target,

I I I

indicate

I I

I

priority

SCSI

device

I

:~~er

~wo

a~~:ke!

,.

asserts

ACK.

The l I

ISh

d h k£ I

COMMAND

I

Th

f

11

I

:

~~t~l~u!s(~~~ei~\~:e:

delays

the

InitIator

~~:~;a~~~a

c(~~~~~~e~n~~1

_

The

Initiator

shall

read

data

(7-0.pl

:-

p~~ce~~r:

a I

COHPLETE

1001.

:-

Ph:seo~i~7i~;

:

I

highestl

the

initiator

I

asserts

SEl.

I

after

REG

Is

true

then

.sserts

ACK

I under Data in I I an

A~bltration

r

lOesleesaSaersbsitsrya.

tliOtnnaond

I

REO

is

false.

I I phase I Phase

If

I

I

ARBlTRATI0N

SYSTEMS:

L

~hen

ACK

becomes

true

at

the

Target

I L See handshake :

imile~ented,

or

:

higher

priority

SCSI

I

!~a~~s;:~~e:~~~e~rbitration

When

ACK

is

true

at

:

the

Target

",ay chaoge

cr

release

datal

I

procedure

Se

ec

Ion ,

dev~~e

~Dtbi~

is

true

the

initiator

that

won

the

Target

the

Target

I

i7-0.PI

and

deassert

R~:;

I under Data

in

Phase

~~en

~he

\~lt

~~tor

arbitration

has

both

~~:~s

d;::S~~~:

~~~o.

PI

I

phase

w,ns

arbitration

and

BSY

and

SEL

asserted

I---

After

REG

Is

falSE

t~E

I"itiator

I

asserts

SEl. ane

changes

the

data

I

deasserts

ACK.

After

A:';

is

false

bus

after

two

Bus

Woen

REQ

becomes I

Target

atay

conLnue

thE

transfer

by

r---

Bus

deYlees haVing

I

lost

arbitratIon

shall

I

re

lease

SSy

ana

I

the,"

own

SCSI

I

device

10

bit

.,thln

I

:f~~~

;:;t~:c~~!:Y

I

true

I

r---

The

Init,.to

r

that

I

wins

arbltratlon

I

waits

at

l'eas'::. l Bus

I

I

I

Clear

Delay

plus

a 8us

Settle

Qelay

after

assertlng

Sel

before

changing

any

s,gnals

on

the

bus.

~~;I~u~e~:y:~e~he

false

at

the

Initiator

I

driving

dot.

(7"O.PI

aod

asserting

asserted

with

both

the

the

Initiator

may

I

REO

initiator

ID

bit

and

the

Change

or

release

data

I

desired

Target·s

lD

b,t.

(7-0,pi

and

deassert

ACK

I

Two

deskew

delays

J--

DAlA

OUl

PHASE

'-lte

Peclpheral.

later

BSY

is

released

I

t-

IN

ALL

SYSTEMS:

THE

I

Target

Oeterm,nes

that

I

it

is

selected

WOen

I

SEL

and

Its

SCSI

:

device

ID

bit

arc

true

I and

BSY

and

I/O

are

I

false

for

at

least

a Bus

I

Settle

[lelay.

The

I TdrOI t

thfn

c:~crts

I

f."\

loltt'lln

a

~c~l_tion

I Abc-l T

,mr.

I

t '

..

:

dl'~k.LW

dflaV5

I

at

tl.. r

the

i.,it

later

I

d('tf(t~

t:::V trw.:

It

I

rE:lcdt"·p

....

~~~

2'ld

rf'ay

cljanQ( de:::-

tJ,.,:.

~

~gnal~

..

2-13

The

Ta"get

cont

inues

req,Je~

t

ing

command

bytes.

lne

nurebe!'"

of

bytes

depends

on

the

corr:-:-and

group

code

I

dct<eted

from

the

first

I

cc"~a"d

byte

rro

,eved.

I!

I

I

I

~-

Data

15

to

be

H"~

I

Target.

I

L

Target

O<'f>S("t, , D.I/O. and

MSG

I

dur

lng

th('

~l~

li

'':'

..

~

tlc"'ldsnake

of

tn1s

I phasE.

~cfcr

tc

ttlC

llandooa,e

t

procedure

of

tl"',(

Ccm:nand

Phase.

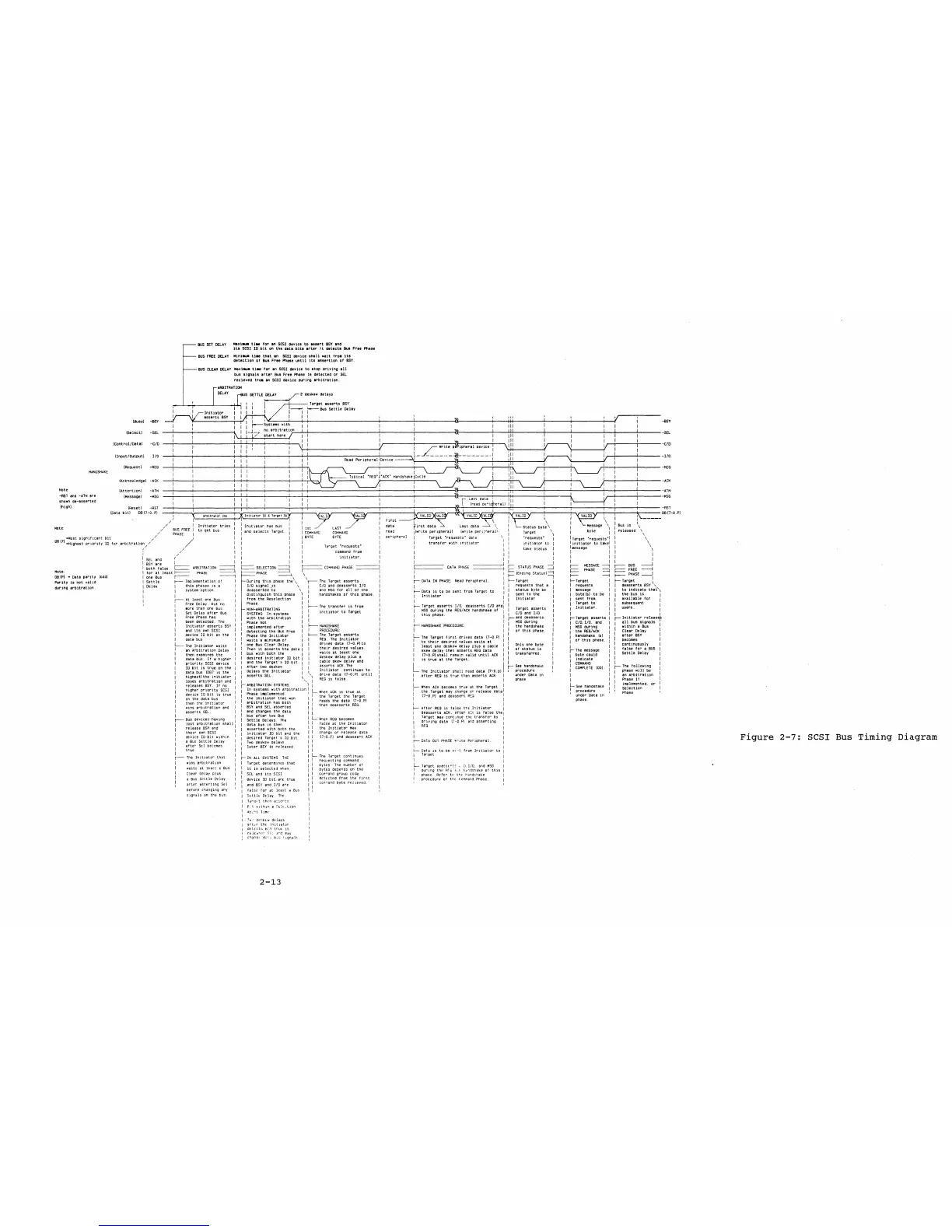

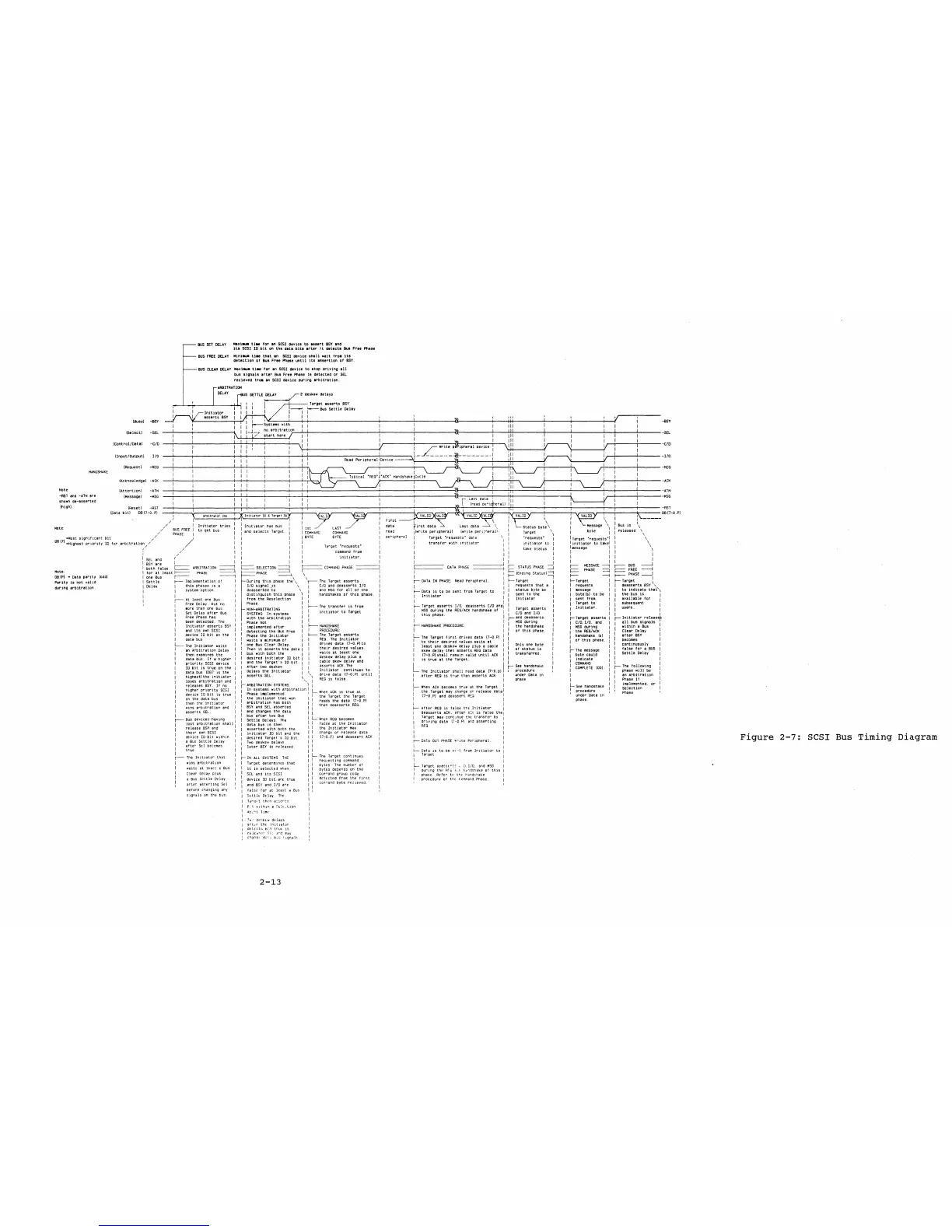

Figure

2-7:

SCSI

Bus

Timing

Diagram

Loading...

Loading...