4P THEORY OF OPERATION

5.1

CPU THEORY OF OPERATION

5.1.1

Introduction

Contained

in

the following paragraphs

is

a description of the

component parts of the Model4P CPU.

It

is

divided into the log-

ical

operational

functions

of

the

computer.

All

components

are

located

on

the Main CPU board inside the case housing. Refer

to

Section 3 for disassembly/assembly procedures.

5.1.2 Reset Circuit

(pin 9 of U126).

If

FAST

is

a logic low, the 20.2752 MHz

is

di-

vided by 10 which generates a 2.2752 MHz signal

If

FAST

is

a

logic high, the 20.2752 MHz

is

divided by 5 which generates a

4.05504 MHz signal. The CPU clock (PCLK)

is

fed through

an

active

pull-up

circuit

which

generates a

ful15-volt

swing

with

fast

rise and fall times required by the Z80A. U126. the 16R6A

PAL.

generates

all

symmetrical

output

signals

and

also

does

not

al-

low the PCLK output to short cycle or generate a low or high

pulse

under

110

nanoseconds

which

the

ZaOA

also

requires.

Refer

to

System Timing Fig. 5-2.

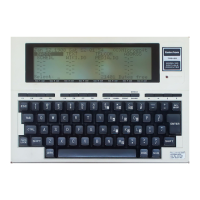

5.1.4.1 Video Timing

'This

is the state to be wriften to latch U89. Signal

is

inverted

before being input to U127.

MOOSEL and

8064'

signals are used to select the desired

video mode.

8064'

controls which reference clock

is

used by

U127 and MOOSEL controls the single or double character

width mode. Refer to the following chart for selecting each

video

mode.

The PLL (NE564)

is

adjusted to oscillate at 12.672 MHz by the

luning capacitor C231. This 12.672 MHz clock

is

then divided

by

10 through U149 to generate a second 1.2672 MHz signal

whioh is fed to a second input of U148. The two 1.2672 MHz

signals

are

compared

internally

to

the

PLL

where

it

corrects

the

12.672 MHz output so

it

is

synchronized with the 20.2752 MHz

clock.

Video Mode

64 x 16

32 x 16

80

x24

40

x 24

MOOSEL

o

1

o

1

8064'

o

o

1

1

The video timing is controlled by a 1

OL8

PAL

(U127) and a four-

bit synchronous counter U128 (74LS161). These two ICs gen-

erate all the necessary timing signals for the four video modes:

64

x

16,

32 x 16,

80

x 24, and 40 x 24.

Two

reference clock sig-

nals

are

required

for

the

four

video modes. One reference

clock, the 10.1376 MHz signal (10M),

is

generated

by

U126 and

is

used by the

64

x 16 and

32

x 16 modes. The second refer-

ence clock

is

a 12.672 MHz (12M) signal which

is

generated by

a Phase Locked Loop (PLL) circuit and

is

used

by

the 80 x

24

and 40 x

24

modes. The PLL circuit consists of U147 (74LS93),

U148 (NE564 PLL), and U149 (74LS90). The original 20.2752

MHz clock

is

divided by

16

through U147 which generates a

1.2672 MHz signal. The output of U147 is reduced

in

amplitude

by

the voltage divider network R27 and R28 and the output

is

coupled

to

the reference input of U148 by C227.

The central processing unit (CPU) of the Model 4P microcom-

puter

is

a Z80A microprocessor. The Z80A is capaqle of run-

ning in either 2 MHz

or

4 MHz mode. The CPU controls all

functions

of

the

microcomputer

through

use

of

its

address

lines

(AO-A

15), data lines

(00-07),

and control lines

(lMl,

/IOREQ,

/RO,

/WR, /MREQ, and /RFSH). The address lines

(AO-A

15)

are

buffered to other ICs through two 74LS244s (U68 and U26)

which are enabled all the time with their enables pulled to GNO.

The control lines are buffered to other ICs through a 74F04

(U86). The data lines

(00-07)

are buffered through a bi-direc-

tionaI 74LS245 (U71) which

is

enabled by BUSEW and the di-

rection

is

controlled by BUSOIW.

5.1.3 CPU

The

main

timing

reference

of

the

microcomputer,

with

the

ex-

ception of the FOC circuit, comes from a 20.2752 MHz Crystal

Oscillator (Y1). This reference

is

divided and used for gener-

ating all necessary timing for the CPU, video circuit, and

RS-

232-C circuit. The output of the crystal oscillator

is

filtered by a

ferrifte bead (FB5), 470 ohm resistor (R46), and a

68

pf

ca-

pacitor (C242). After being filtered,

it

is

fed into U126, a 16R6A

PAL

(Programmable Array Logic), where

it

is divided by 2 to

generate a 10.1376 MHz signal (10M) for the

64

X

16

video dis-

play. U126 divides the 20.2752 MHz

by

4 to generate a 5.0688

MHz signal (RS232CLK) for the baud rate generator

in

the RS-

232-C circuit. The

CPU

clock

is

also generated by U126 which

can

be

either 2 or 4 MHz depending

on

the state of

FAST

input

The Model 4P reset circuit provides the neccessary reset

pulses

to

all

circuits

during

power

up

and

reset

operations.

R25

and C218 provide a time constant which holds the input of

U121

low during power-up. This allows power to be stable to

all

cir-

cuits before the

RESEr

and RESETsignals are applied. When

C218 charges to a logic high, the output of

U121

triggers the

input of a retriggerable one-shot mullivibrator

(Ul).

Ul

outputs

a pulse with

an

approximate width of

70

microsecs. When the

reset switch is pressed on the front panel, this discharges C218

and

holds the input of

U121

low until the switch is released.

On

release of the switch, C218 again charges up, triggering

U121

and

U1

to

reset

the

microcomputer.

5.1.4 System Timing

23

Loading...

Loading...