RL78 Family VDE Certified IEC60730/60335 Self Test Library

R01AN0749EG0201 Rev.2.01 Page 47 of 50

Mar 04, 2014

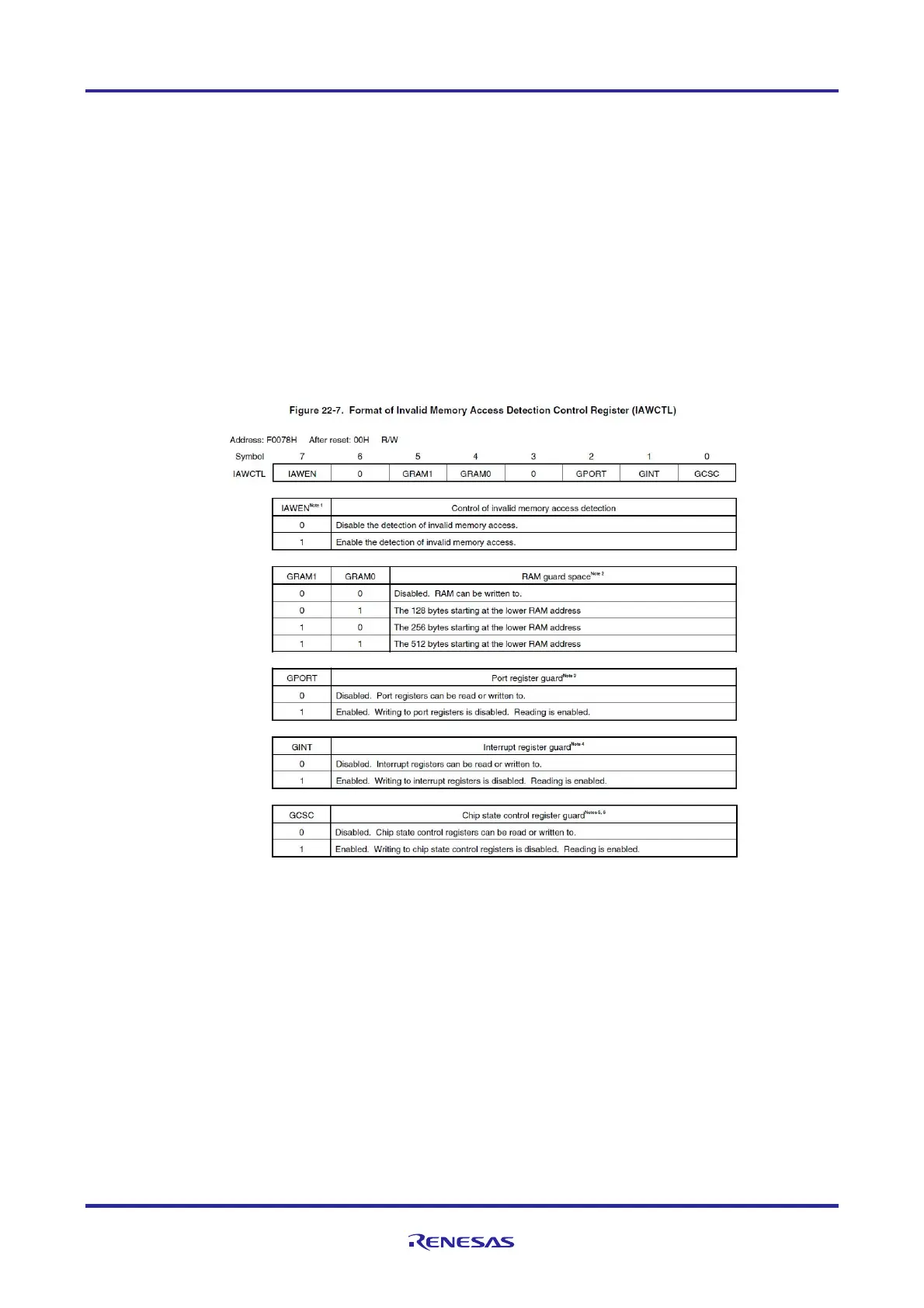

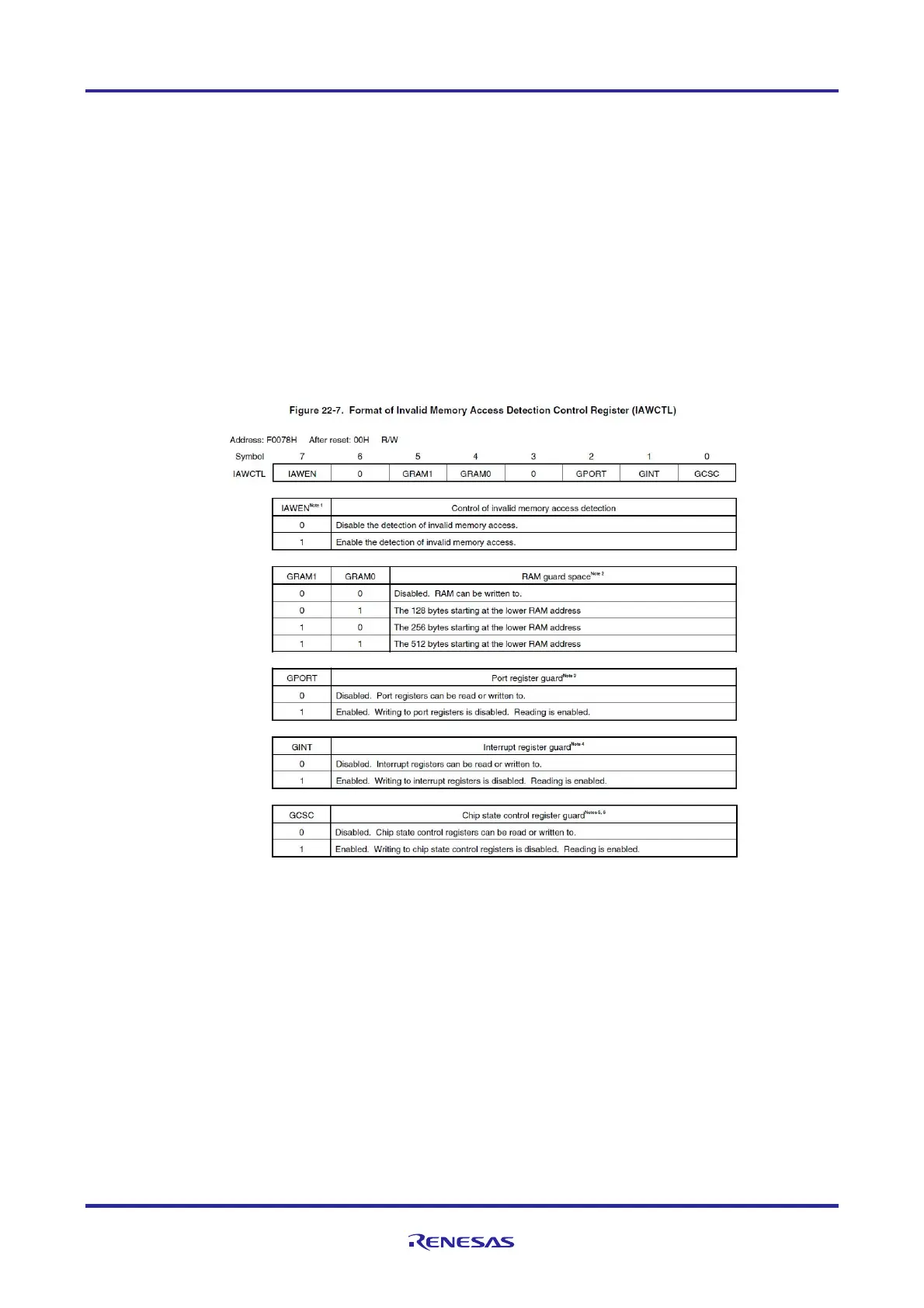

6.1.6 Control Register Protection

This is a write protection feature that prohibits a write to the control registers. No error is generated if a write

occurs to this area, but the write operation does not change the state of the registers involved. The protection

can be turned off, if a change is required for the SFR registers or for safety reasons the SFR settings are

refreshed by the application.

The following control registers can be protected with this function

CMC, CSC, OSTS, CKC, PERx, OSMC, LVIM, LVIS, and RPECTL

The interrupt SFR registers can be guarded by the “GCSC” bit as shown in figure 26 below

Figure 26 Invalid Memory Access Protection

Loading...

Loading...