- 8 -

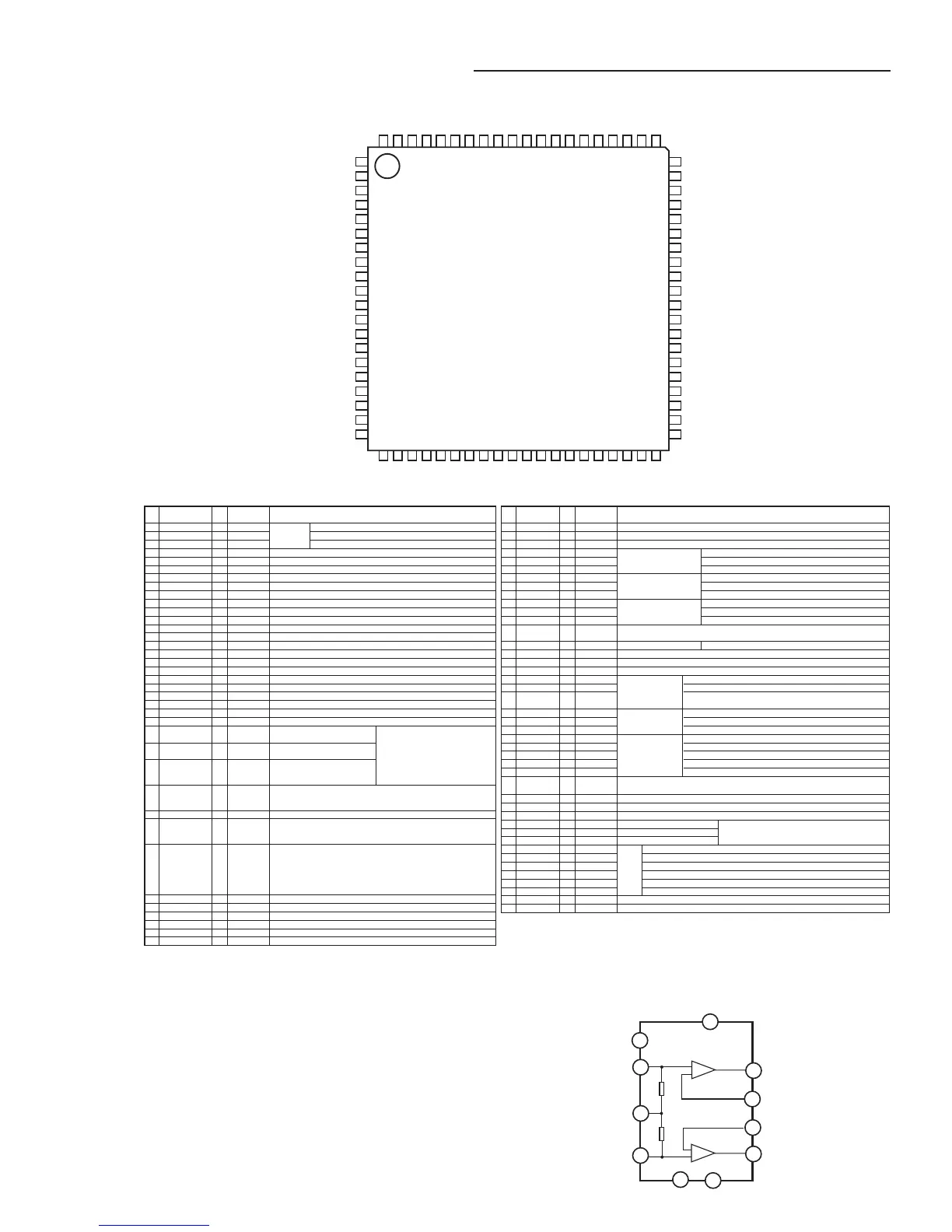

IC101 LC78646E-UHK-E (CMOS LSI for CD Player)

IC BLOCK DIAGRAM & DESCRIPTION

Pin

No.

Pin

No.

Pin Name

I/O

Reset

state

Reset

state

Function description

1SLCO O -

Slice level

control

Control output.

2SLCIST AI - SLCO output current adjustment resistor connection pin.

3EFMIN I - RF signal input pin.

4RF AO - RF monitor pin.

5RFVDD - - RF power supply pin.

6RFVSS - - RF ground pin. Must be connected to 0V.

7 FIN1 AI - A+C signal input pin.

8 FIN2 AI - B+D signal input pin.

9TIN1 AI - E signal input pin.

10 TIN2 AI F signal input pin.

11 VREF AO RFVDD/2 VREF voltage output pin.

12 REFI AI - Reference voltage seting pin.

13 FE AO ZHI FE signal monitor pin.

14 TEC AO - TE signal LPF capacitor connection pin.

15 TE AO ZHI TE signal monitor pin.

16 RFMON AO ZHI RF internal signal monitor pin.

17 JITTC A - Jitter detection capasitor connection pin.

18 ADAVDD - - Servo A/D, D/A supply pin.

19 ADAVSS - - Servo A/D, D/A ground pin. Must be connected to 0V.

20 TDO AO ADAVDD/2 Tracking control output pin. D/A output.

21 FDO AO ADAVDD/2 Focus control output pin. D/A output.

22 SPDO AO ADAVDD/2 Spindle control output pin. D/A output.

23 SPDO AO ADAVDD/2 Thread control output pin. D/A output.

24 GPDAC AO ADAVDD/2 Servo D/A general-purpose output pin.

25 CONT4 I/O Input mode

General-purpose

input / output pin 4.

Controlled by commands

from the microprocessor.

Any of these that are unused

must be either set up as input

pin ports and connected to 0V,

or set up as output pin ports

and left open.

26 CONT5 I/O Input mode

General-purpose

input / output pin 5.

27 SBCK/CONT6 I/O Input mode

General-purpose

input / output pin 6,

or subcode read clock input pin.

28 SBCK/FG I -

Subcode read clock input pin / FG signal input pin /

external emphasis setting pin.

Set to command pin function. Must be connected to 0V.

29 DEFECT O L Defect pin.

30 V / *P O H

Rough servo / phase control automatic switching monitor

output pin.

"H" for rough servo and "L" for phase servo.

31 FSEQ O L

Synchronization signal detection output pin.

Outputs a high level when the synchronization signal

detected

from the EFM signal and the internally generated

synchronization

signal agree.

32 MONI 1 O L Internalsignal monitor pin 1.

33 MONI 2 O L Internalsignal monitor pin 2.

34 MONI 3 O L Internalsignal monitor pin 3.

35 MONI 4 O L Internalsignal monitor pin 4.

36 MONI 5 O L Internalsignal monitor pin 5.

37 (3.3V)VSS - -

Digital ground pin. Must be connected to 0V.

Pin Name

I/O Function description

38 VDD - - Digital power supply pin.

39 DOUT O L Digital OUT output pin.

40 TEST I L Test input pin. Must be connected to 0V.

41 LVDD - -

L channel D/A converter

L channel power supply pin.

42 LCHO AO LVDD/2 L channel output pin.

43 LVSS - - L channel ground pin. Must be connected to 0V.

44 RVSS - -

R channel D/A converter

R channel ground pin. Must be connected to 0V.

45 RCHO AO LVDD/2 R channel output pin.

46 RVDD - - R channel power supply pin.

47 XVDD - -

Crystal oscillator

Crystal oscillator power supply pin.

48 XOUT O Oscillator Connections for a 33.8688MHz or 16.9344MHz

49 XIN I Oscillator crystal oscillator pin.

50 FSX/16MIN I/O Input mode

7.35kHz synchronization signal output pin.

DF, DAC external clock input pin.

51 XVSS - - Crystal oscillator Crystal oscillator ground pin. Must be connected to 0V.

52 C2F O H C2 flag output pin.

53 EFLG O L C1, C2 error correction monitor pin.

54 16MOUT O CLK output 16.9344MHz output pin.

55 ASLRCK I

Antishock mode

L/R clock input pin. (Must be connected to 0V when unused)

56 ASDACK I Bit clock input pin. (Must be connected to 0V when unused)

57 ASDFIN I

L/R channel data input pin.

(Must be connected to 0V when unused)

58 LRSY O L

Digital data output

L/R clock output pin.

59 DATACK O L Bit clock output pin.

60 DATA O L L/R channel data output pin.

61 CE I -

Micro

-processor

interface

Chip enable signal input pin.

62 CL I - Data transfer clock input pin.

63 DI I - Data input pin.

64 DO O (H) Data output pin. (Nch open drain output)

65 *WRQ O H Interruption signal output pin.

66 *RES I -

Reset input pin.

This pin must be set low briefly after power is first applied.

67 DRF O L Focus ON detect pin.

68 VDD5V - - Microprocessor interface power supply pin.

69 VSS - - Digital ground pin. Must be connected to 0V.

70 CONT3 I/O Input mode General-purpose output pin 3. Controlled by commands from the microprocessor.

71 CONT2 I/O Input mode General-purpose output pin 2. Must be set as an input pin and connected to 0V

72 CONT1 I/O Input mode General-purpose output pin 1. or set as an output pin and left open when unused.

73 PDO1 O

PLL

Phase comparison output pin 1 to control built-in VCO.

74 PDO2 O Input mode Phase comparison output pin 2 to control built-in VCO.

75 VVSS - - Built-in VCO GND pin. Must always be connected to 0V.

76 PCKIST AI - Resistor connection pin to set current for PD01 and 02 outputs.

77 VVDD - - Built-in VCO power supply pin.

78 FR AI - Resistor connection pin to set the frequency range of built-in VCO.

79 LDS AI - Laser power detection signal input pin.

80 LDD AO - Laser power detection signal output pin.

Note) The same potential must be supplied to all power supply pins, i. e. , RFVDD, VVDD, ADAVDD, VDD, LVDD,

RVDD AND XVDD. Pins operated from the microprocessor interface power supply (VDD5V) pin :

CE(61 pin), CL(62pin), DI(63 pin), DO(64 pin), *WRQ(65 pin), RES(66 pin), DRF(67 pin), CONT1(72 pin),

CONT2(71 pin), CONT3(70 pin)

1 60

2

59

3

58

4

57

5

56

6

55

7

54

8

53

9

52

10

51

11

50

12

49

13

48

14

47

15

46

16

45

17

44

18

43

19

42

20

41

21 80

22

79

23

78

24

77

25

76

26

75

27

74

28

73

29

72

30

71

31

70

32

69

33

68

34

67

35

66

36

65

37

64

38

63

39

62

40 61

FIN1

FIN2

TIN1

TIN2

REFI

DEFECT

ADAVDD

ADAVSS

JITTC

SLCO

EFMIN

SLCIST

PDO1

PDO2

FR

PCKIST

VVDD

VVSS

SBCK/FG

XIN

XOUT

16MOUT

XVDD

XVSS

*RES

*WRQ

CL

CE

DI

DO

VDD5V

CONT1

CONT2

CONT3

CONT4

CONT5

SBCK/CONT6

TEST

LVDD

LVSS

LCHO

RCHO

RVDD

RVSS

FE

TE

TEC

RF

RFVDD

RFVSS

RFMON

VREF

LDD

LDS

FDO

TDO

SLDO

SPDO

GPDAC

DRF

FSEQ

V / *P

VDD

(3.3V)VSS

VSS

MONI 1

MONI 2

MONI 3

MONI 4

MONI 5

FSX/16MIN

C2F

EFLG

DOUT

LRSY

DATACK

DATA

ASLRCK

ASDACK

ASDFIN

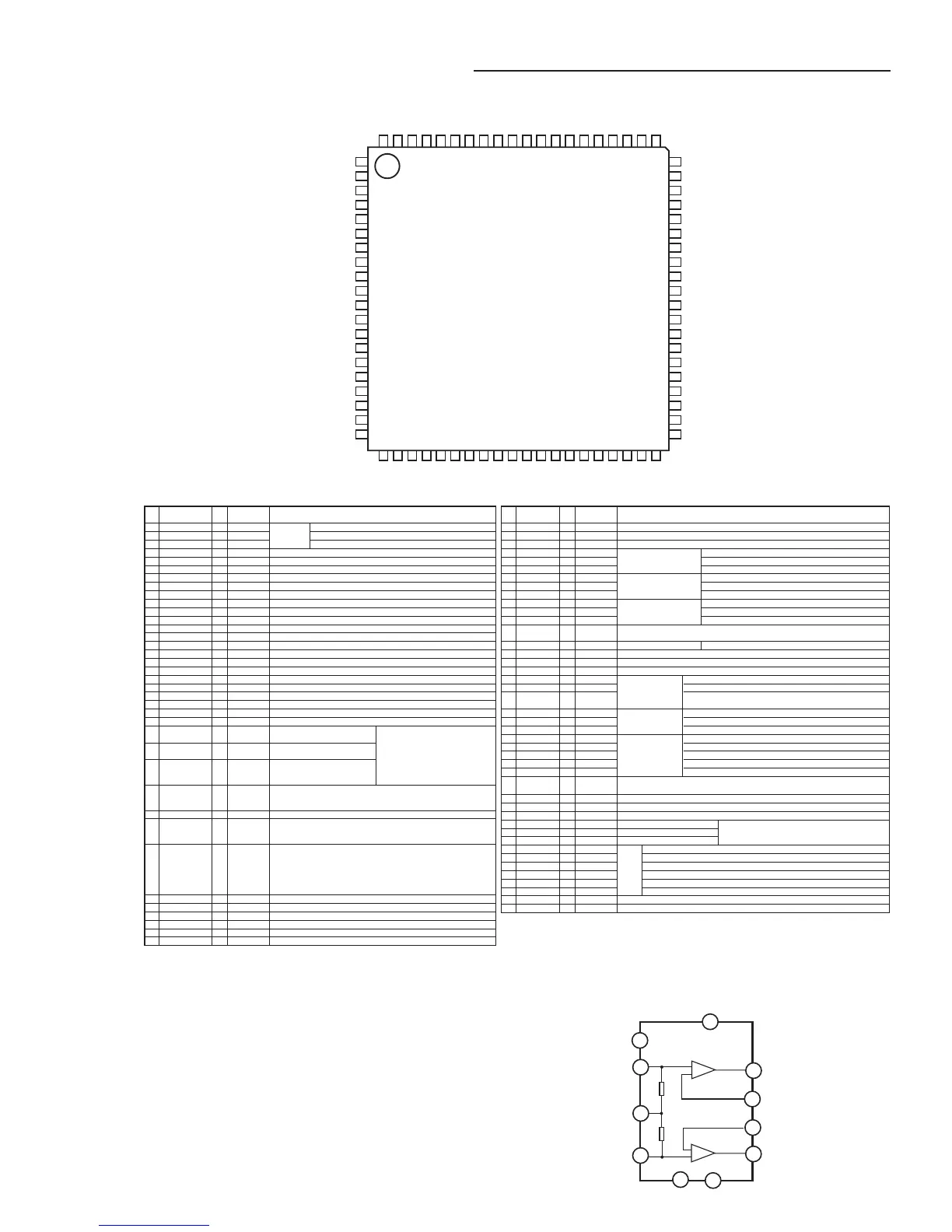

IC442 TDA7269 (Stereo Amplifier)

MUTE

IN-L

GND

IN-R

VSS

OUT-L

IN-L

OUT-R

5

7

9

11

4

8

3

1

6

10

2

+

+

-

-

IN-R

IN-R

IN-R

Loading...

Loading...