12

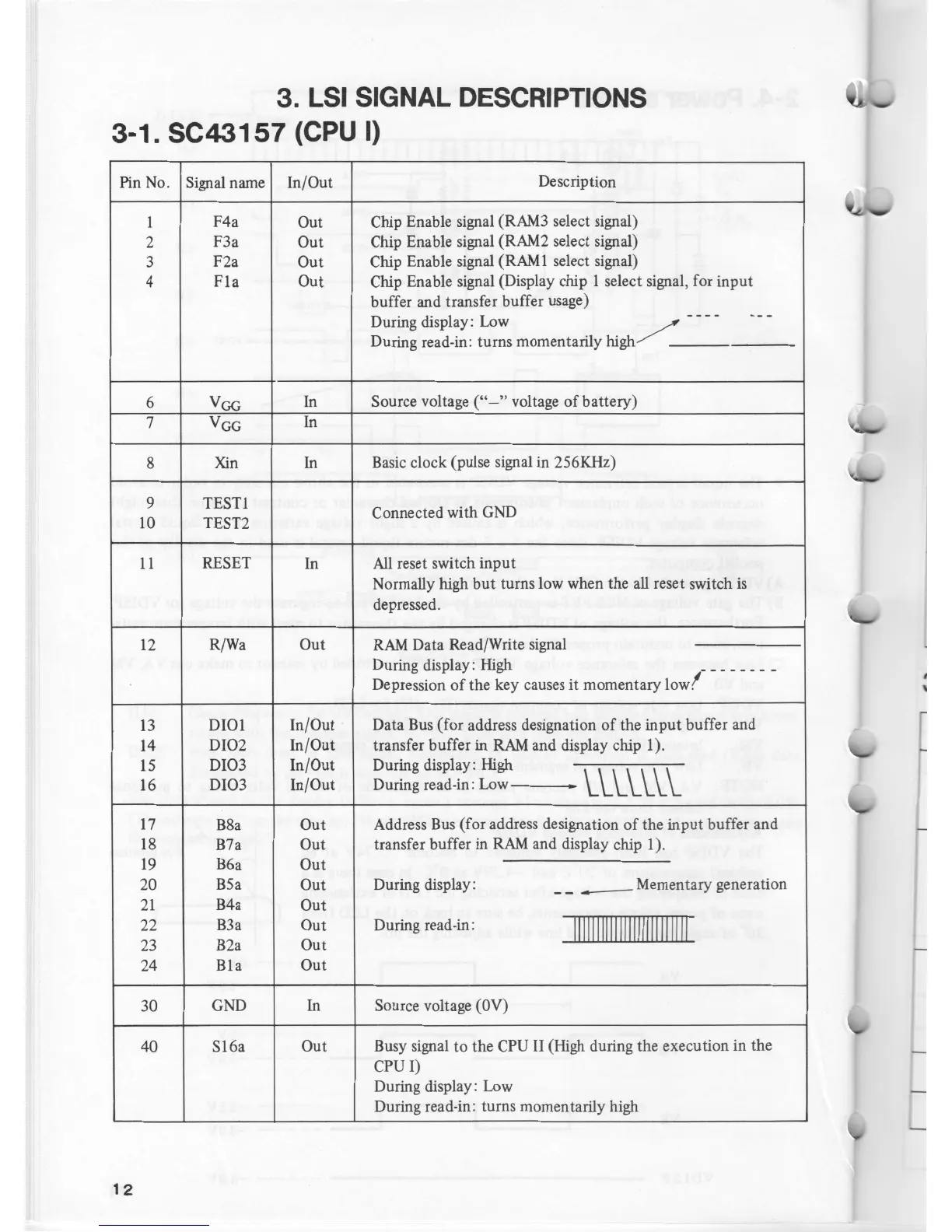

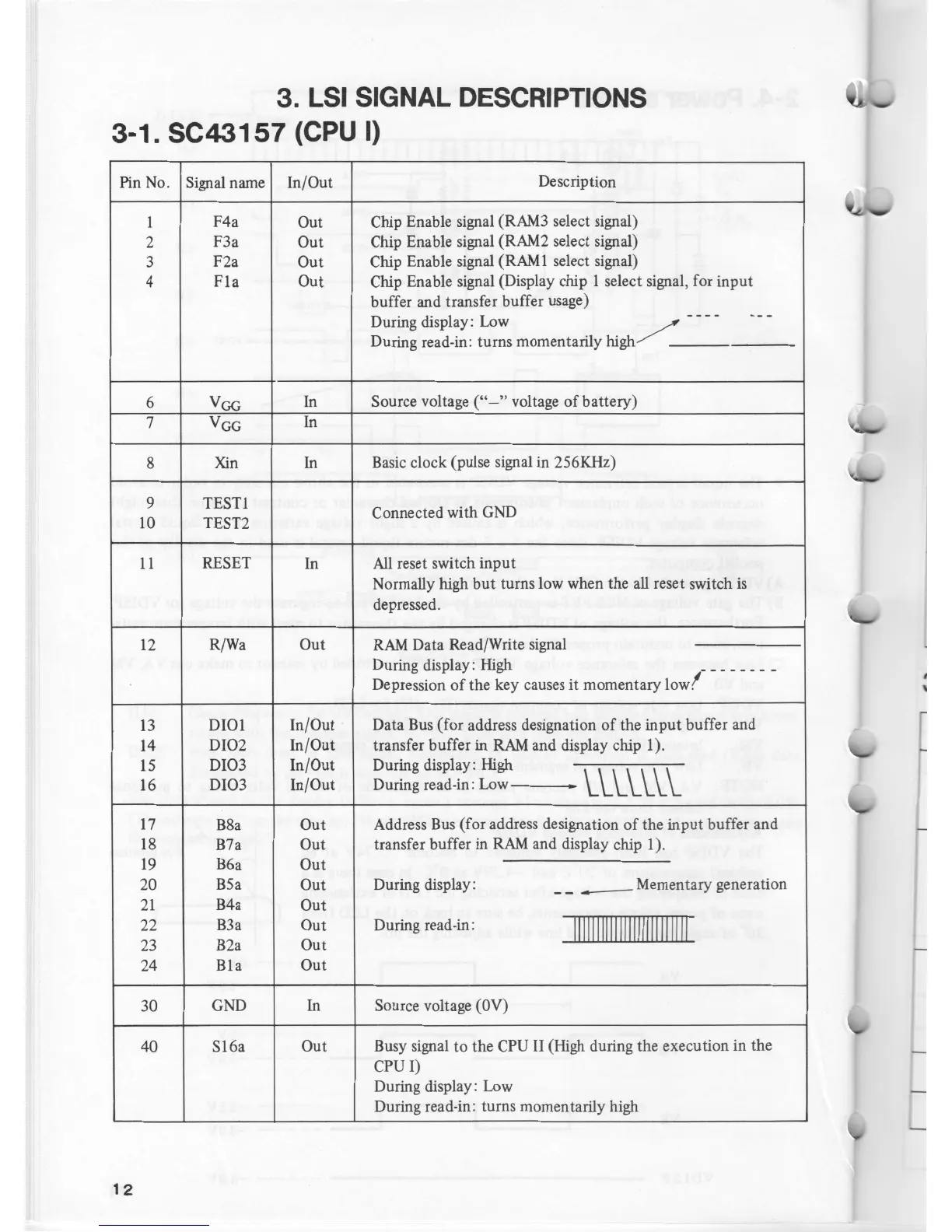

Pin No.

Signal name In/Out

Description

1

F4a Out

Chip Enable signal (RAM3 select signal)

2

F3a Out

Chip Enable signal (RAM2 select signal)

3

F2a Out

Chip Enable signal (RAM

1

select signal)

4

Fla

Out

Chip Enable signal (Display chip

1

select signal, for input

buffer and transfer buffer usage)

During

display

:

Low

/

- -

-

-

-

- -

During read-in: turns momentarily high

6

VGG

In

Source

voltage("

-

"

voltage of battery)

7

VGG

In

8

Xin

In

Basic clock (pulse signal in 256KHz)

9

TE

S

Tl

Connected with GND

10

TEST2

11

RESET In All reset switch input

Normally high but turns low when the all reset switch

is

depressed.

12

R/Wa

Out

RAM Data Read/Write signal

During display

:

High

________

Depression of the key causes it momentary

low!

13

DIO

l

In/O

u

t

Data Bus (for address designation of the input buffer and

14

DI02

In/O

u

t

transfer buffer in RAM and display chip

1

).

15

DI03

In/Out

During display: High

\_

\_

\_

\_

\_

\_

\_

16

DI03

In/O

u

t

During

read-in

:

Low

17

B8a

O

u

t

Address Bus (for address designation

of

the input buffer and

18

B7a

Out transfer buffer in RAM and display chip

1

)

.

19

B6a

Out

20

BS

a

Out

During

display

:

___

Memen

t

ary generation

21

B

4a Out

22

B3a

Out During read-in

:

lllllllllll

l

lllllllll

l

ll

l

23

B2a Out

24

Bla

Out

30

GND

In

Source voltage

(OV)

40 S16a

Out

Busy signal to the CPU II (High during the execution in the

CPU

I)

During display: Low

During read-in

:

turns momentarily high

3. LSI SIGNAL DESCRIPTIONS

3-1. SC43157 (CPU

I)

Loading...

Loading...