LC-42XL2E/S/RU, LC-46XL2E/S/RU, LC-46X20E/S/RU, LC-52XL2E/S/RU, LC-52X20E/S/RU

5 – 19

T1 AVSSLLPLL — 1.2V Line Lock PLL GND.

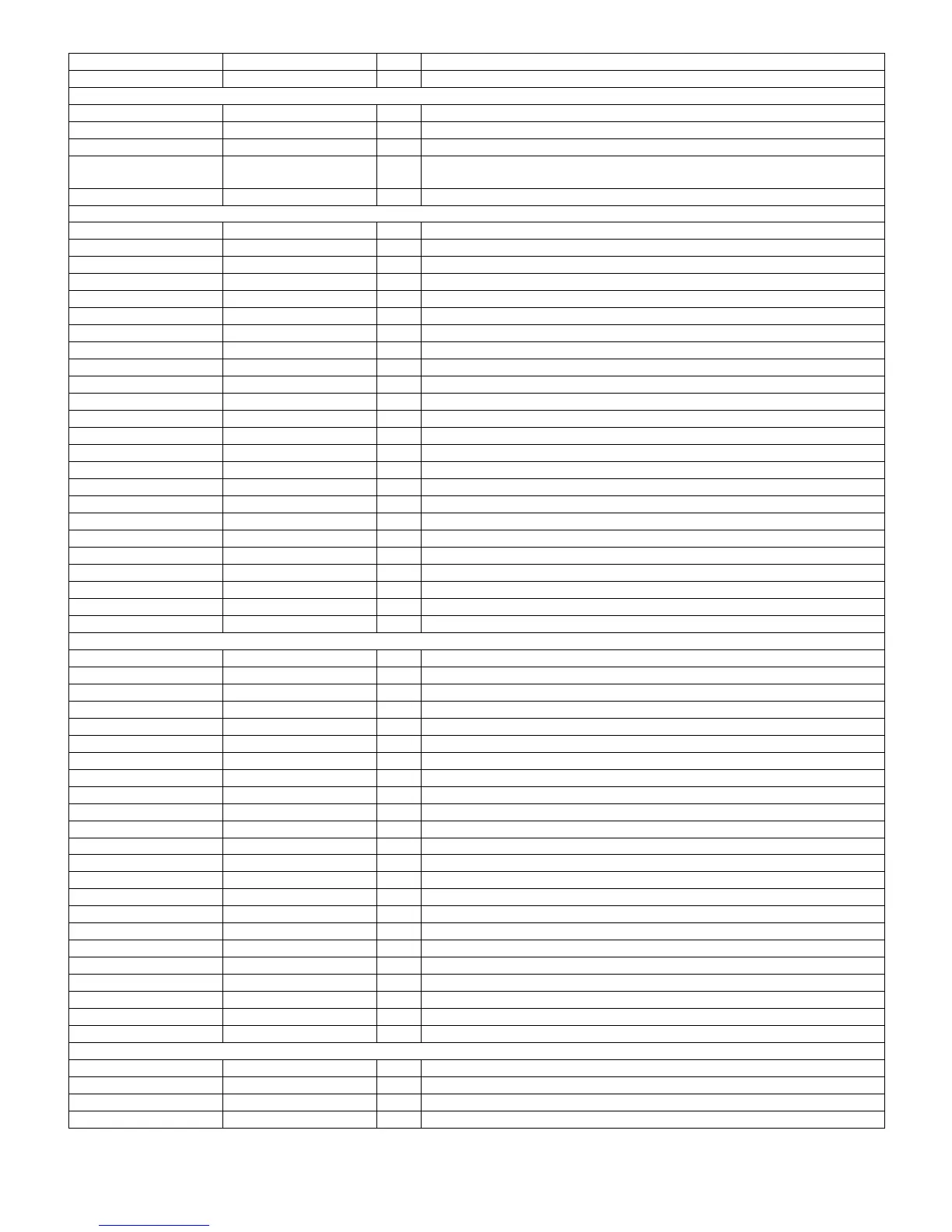

Miscellaneous Ball Assignments.

F18 RESET I System reset forces the chip to a known state. Active High.

G18 INTN I/O Interrupt signal (active low).

G17 PWM0 I/O PWM I/O. (Not connected)

F16 V5SF I 5V reference voltage (must be connected to 5V even in standby mode, when CPU

I/O is 5V)

F17 TESTMODE I Reserved (Connected to ground).

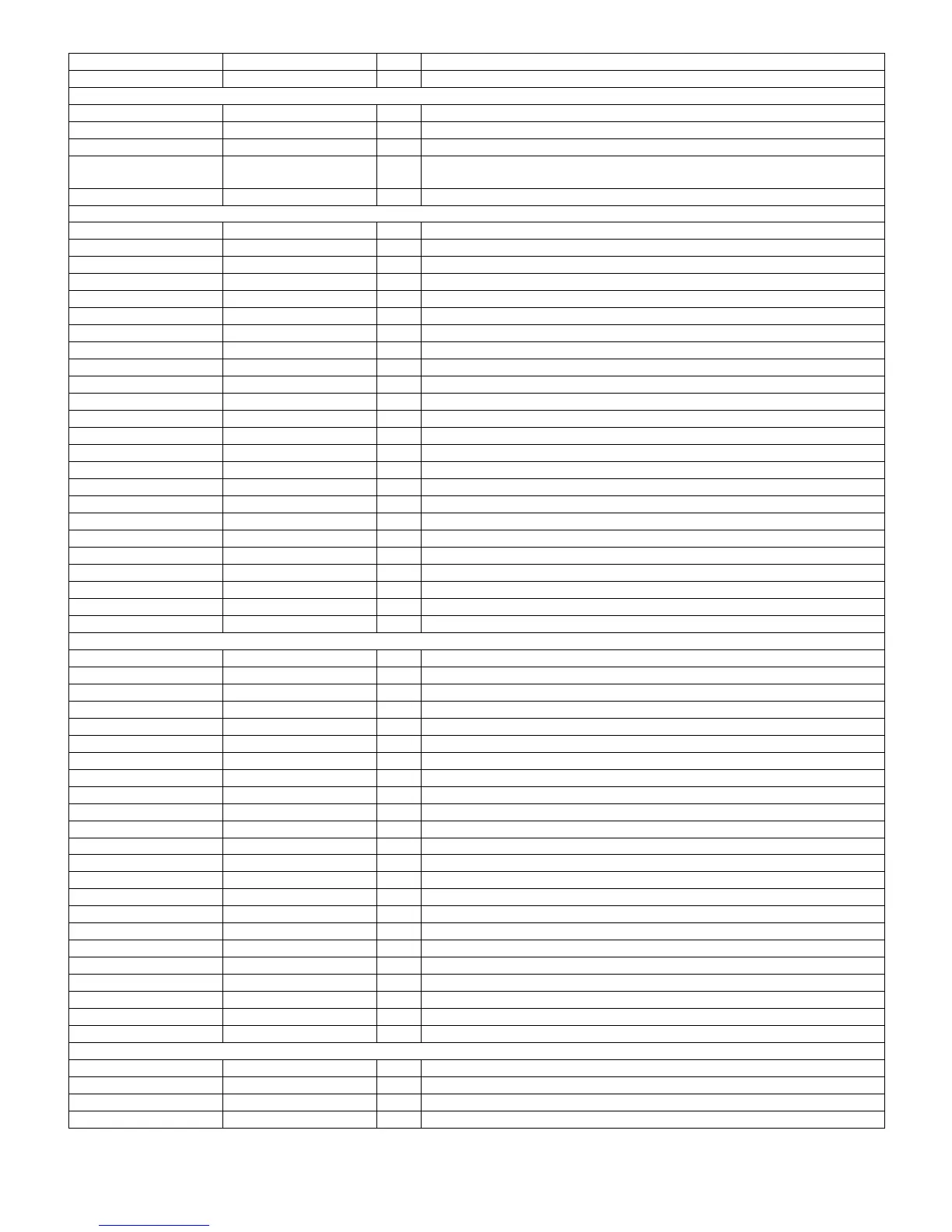

LVDS Output Ball Assignments.

A14 TA1P O LVDS 1st Channel Differential positive data out.

B14 TA1M O LVDS 1st Channel Differential negative data out.

A15 TB1P O LVDS 1st Channel Differential positive data out.

B15 TB1M O LVDS 1st Channel Differential negative data out.

A16 TC1P O LVDS 1st Channel Differential positive data out.

B16 TC1M O LVDS 1st Channel Differential negative data out.

A18 TD1P O LVDS 1st Channel Differential positive data out.

B18 TD1M O LVDS 1st Channel Differential negative data out.

A19 TE1P O LVDS 1st Channel Differential positive data out.

B19 TE1M O LVDS 1st Channel Differential negative data out.

B17 TCLK1M O LVDS 1st Channel Differential positive CLK out.

A17 TCLK1P O LVDS 1st Channel Differential negative CLK out.

F19 TCLK2M O LVDS 2st Channel Differential positive CLK out.

E20 TCLK2P O LVDS 2st Channel Differential negative CLK out.

H19 TE2P O LVDS 2st Channel Differential positive data out.

G20 TE2M O LVDS 2st Channel Differential negative data out.

G19 TD2P O LVDS 2st Channel Differential positive data out.

F20 TD2M O LVDS 2st Channel Differential negative data out.

E19 TC2P O LVDS 2st Channel Differential positive data out.

D20 TC2M O LVDS 2st Channel Differential negative data out.

B20 TB2P O LVDS 2st Channel Differential positive data out.

A20 TB2M O LVDS 2st Channel Differential negative data out.

D19 TA2P O LVDS 2st Channel Differential positive data out.

C20 TA2M O LVDS 2st Channel Differential negative data out.

HDMI Interface Ball Assignments.

L4 PVCC — TMDS PLL supply voltage.

M5 ANTSTO O Test pin. (Not connected)

M4, N4, N5, P4 AVCC — TMDS analog supply voltage.

L2 RXC- I TMDS differential CLK-.

L1 RXC+ I TMDS differential CLK+.

L3, M3, N3, P3, R1 TMDS_GND — TMDS GND.

M2 RX0- I HDMI Differential input pair 0-

M1 RX0+ I HDMI Differential input pair 0+

N2 RX1- I HDMI Differential input pair 1-

N1 RX1+ I HDMI Differential input pair 1+

P2 RX2- I HDMI Differential input pair 2-

P1 RX2+ I HDMI Differential input pair 2+

R5 REGVCC — ACR PLL Regulator supply voltage.

P5 DGND — ACR PLL GND.

T10 PWR5V I TMDS port Transmitter Detect (5V tolerant).

T11 DSCL I/O DDC I2C clock for DDC (5V tolerant).

U11 DSDA I/O DDC I2C data for DDC (5V tolerant).

U12 WS O I2S Word select output.

V11 SCDT O Indicates Active video at HDMI input port.

V12 SD0 O I2S serial data output.

W11 AUDIOCLK I Audio master clock input reference.

W12 SPDIF O S/PDIF audio output.

Y11 SCK O I2S serial clock output.

Pin Assignments for Reference Voltage.

V5 VREFN1 — ADC1 voltage reference-.

W5 VREFP1 — ADC1 voltage reference+.

V7 VREFN2 — ADC2 voltage reference-.

W7 VREFP2 — ADC2 voltage reference+.

Pin No. Pin Name I/O Pin Function

Loading...

Loading...