12

All and more about Sharp PC

-1

500 at http:/lwww.PC-1500.info

@ BRO

Bu

s

re

quest s

igna

l.

@ BAK

Bu

s.

request ackow

led

ge

signa

l.

When BRQ go

es

high, the CPU

is

sues a h

ig

h

le

ve

l of

signal

on

BAK

in

response

10

i

t.

The CPU keeps addre

ss

bus

(ADO

~

i\D

15),

data

bu

s

(DO

~

D7)

.

MEO

, MEL R/ W, and OD h

igh

impedance when

BAK

is

in

hi

gh

leve

l.

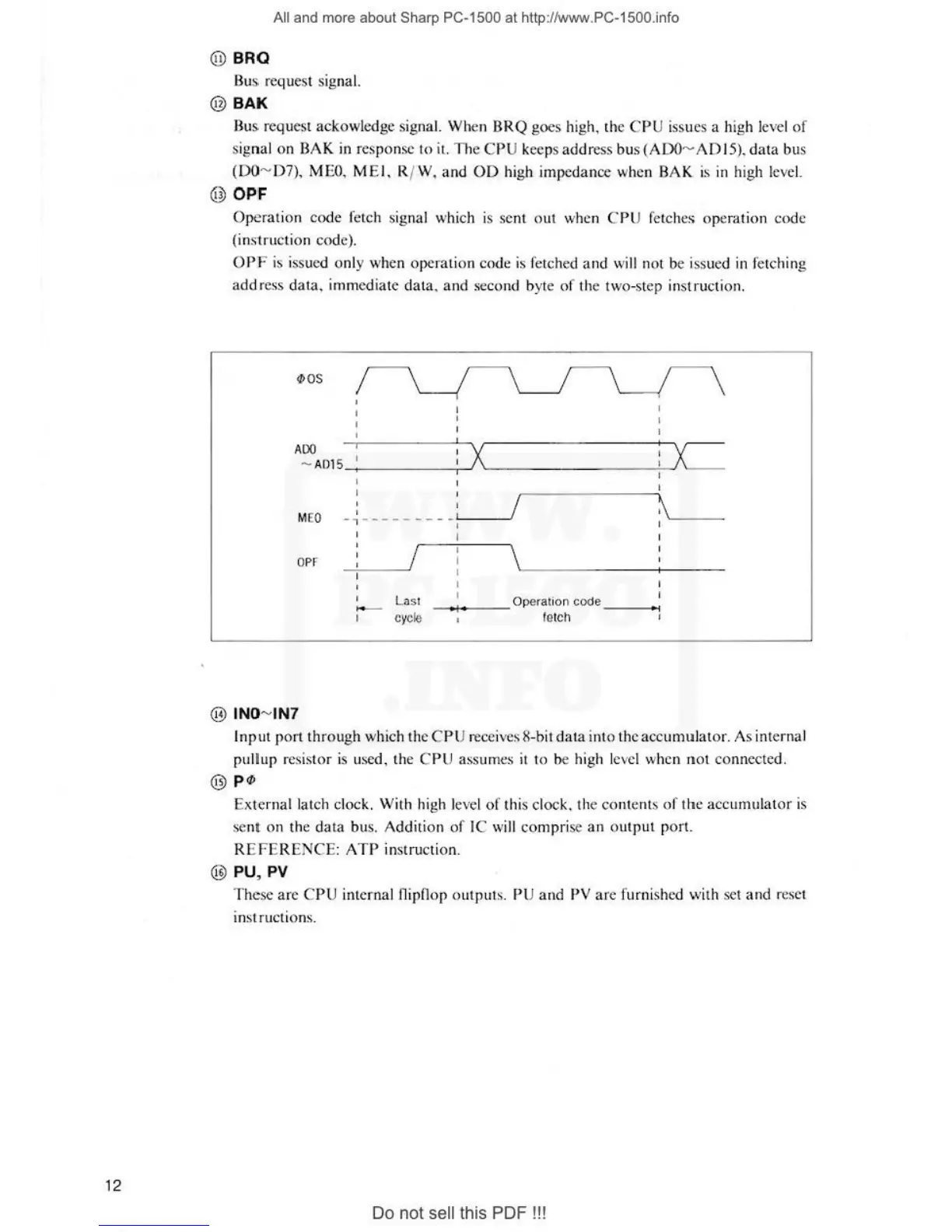

@ OPF

Op

er

ation

code

fetch signal w

hi

ch is sent out

whe

n CPU fetches oper

at

i

on

co

de

(instructi

on

code).

OPF

is

issued only when operation code

is

fetched and

will

not be i

ss

ued in

fe

tching

address data. immediate data. and second byte of the two-step inst ruct

ion

.

<l>OS

ADO

-

AD15

M

EO

OPF

@

INO

~

IN7

'

'

-, -

..

-----

--

,

I I

~-

--~

-

I

La

st

cy

cle

__,

_

__

Operati

on

code

__

__,

fetch

Input port through which the CPU receives 8-hit data into the accumulato

r.

As

internal

pu

ll

up

re

sistor is used. the CPU assumes

it

to be

high

l

evel

wh

en

not connec

te

d.

@>

p

qj

External latch clock. With h

ig

h l

eve

l of this clock. the contents

of

the accumulator is

sent

on

the data bu

s.

Addition

of

IC

wi

ll

compri

se

an output port.

R

EFE

RENCE: ATP instruc

ti

on.

@ PU,

PV

These arc CPU internal flipflop outputs.

PU

and

PY

ar

e

fu

rnished with set and

rese

t

inst

ructions.

Do

not

sell this PDF !!!

Loading...

Loading...