Cyclic program execution

3.4 Response time for cyclic and time-driven program execution

Cycle and response times

44 Function Manual, 10/2018, A5E03461504-AD

Update time of the backplane bus for ET 200SP CPUs

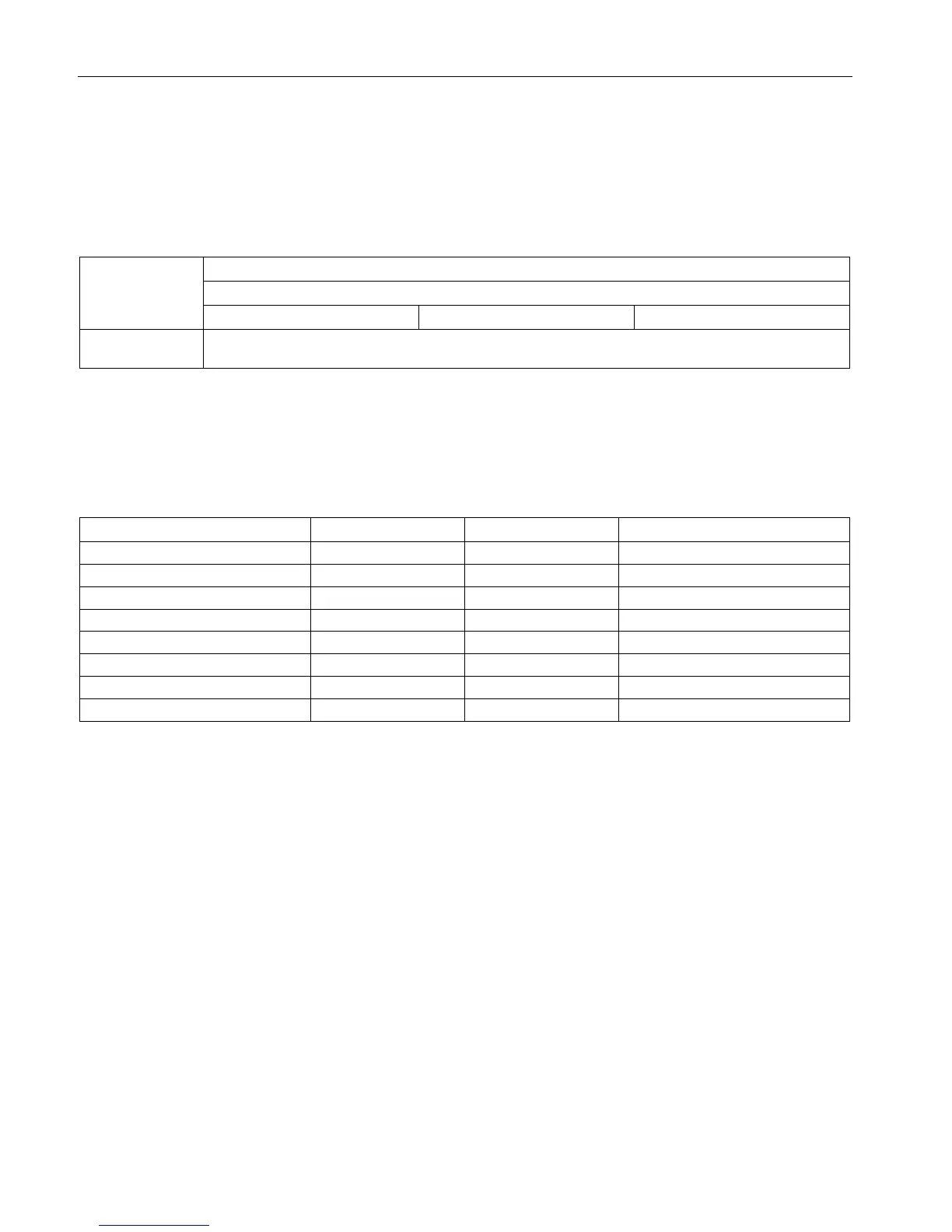

The following table shows the central (typical) update times of the backplane bus for the

ET 200SP CPUs.

Table 3- 6 Update time of the ET 200SP CPUs

250 μs to 1 ms, depending on number and type of central I/O modules

1

The duration of the update time depends on the number of the I/O modules and their type (ST, HF, HS). The update

time is set at 1 ms for a max. central I/O configuration with standard I/O modules. You can reduce the update time down

to 250 μs, for example, by using HF I/O modules and by reducing the number of modules.

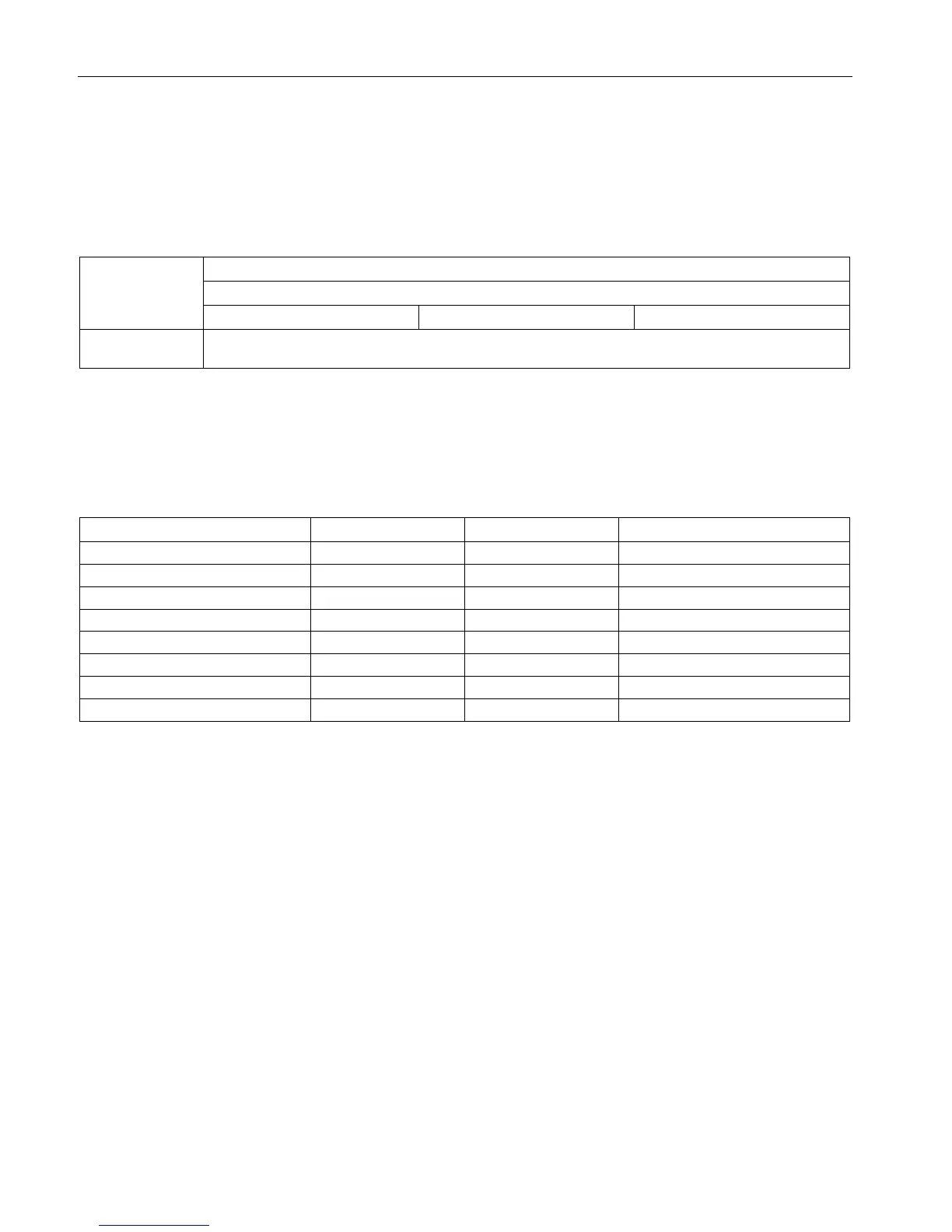

The table below is an orientation guide. It shows the approximate relationship between the

number of ET 200SP I/O modules and the bus cycle that is used. As an example, 8 bytes of

I/O data per I/O module are assumed in the table.

Number of ET 200SP I/O modules

For I/O modules with more than 32 bytes of I/O data, the bus cycle is calculated with an I/O

module of 32 bytes. In this case the I/O module requires multiple bus cycles to update its I/O

data.

Loading...

Loading...