7

D-SJ301

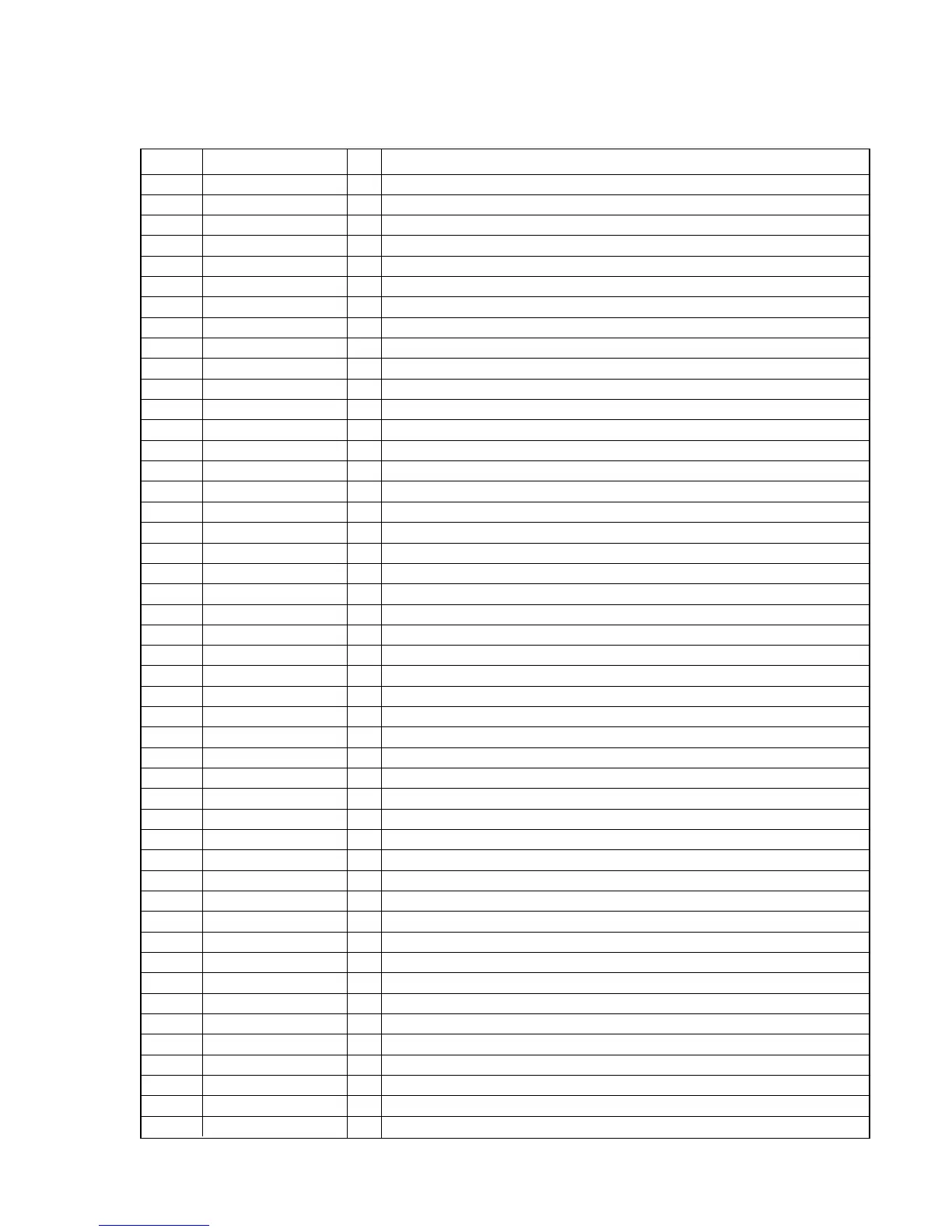

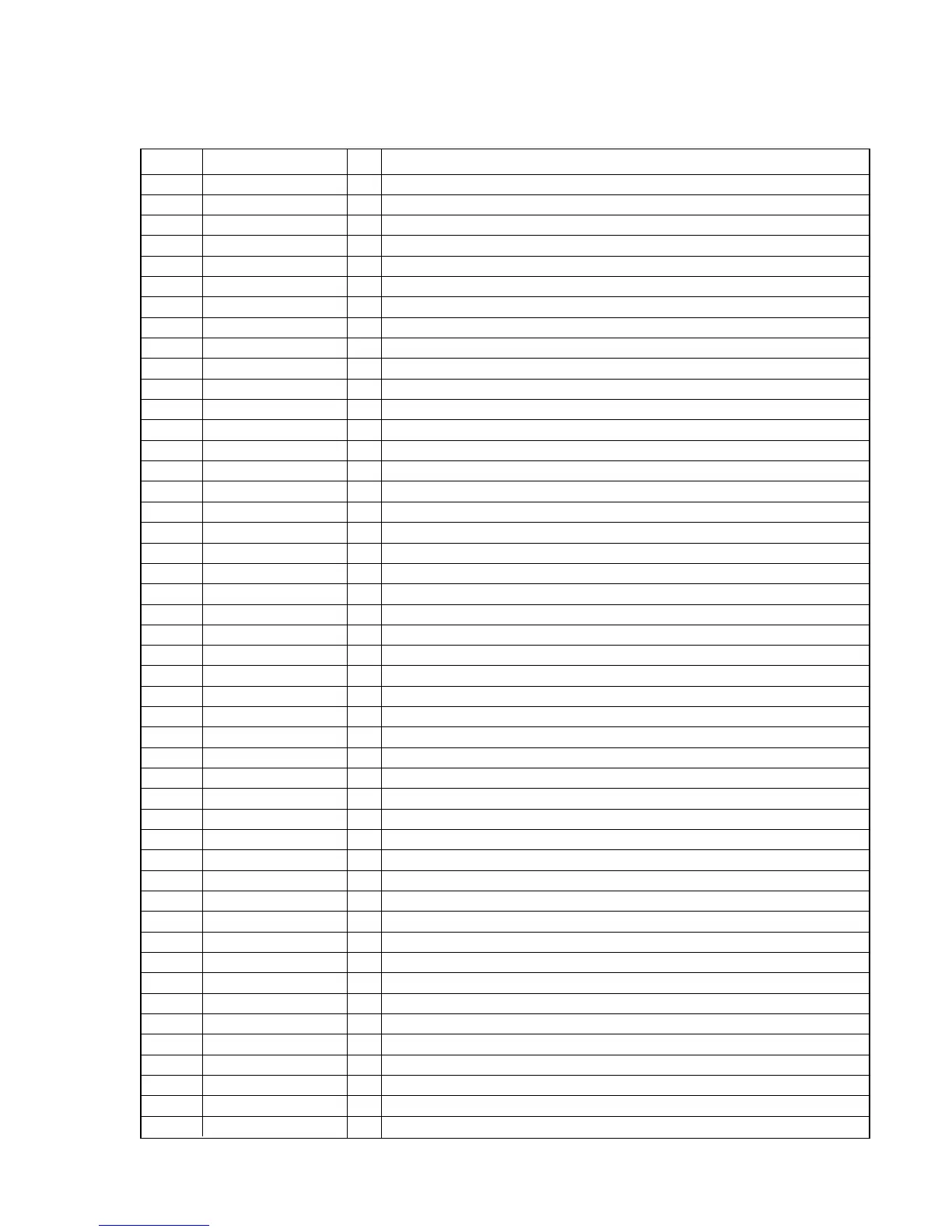

Pin No. Pin name I/O Description

SECTION 5

DIAGRAMS

5-1. EXPLANATION OF IC TERMINALS

IC601 CXD3029R (SYSTEM CONTROL)

1 XRAM O DRAM low address strobe signal outut.

2 XWE O DRAM data input enable signal output.

3 to 6 D0 to 3 I/O DRAM data bus 0-3.

7 DCLK O Not used (OPEN).

8 DCKE O Not used (OPEN).

9 XCAS O DRAM column address storobe signal output.

10 WFCK O Not used (OPEN).

11 to 13 A7 to 9 O DRAM address 7 – 9.

14 DVss – Ground terminal for DRAM interface.

15 to 17 A4 to 6 O DRAM addres 4 – 6.

18 XRDE I/O Not used (OPEN).

19 VDD0–Power supply for digital.

20 CLOCK I Serial data transfer clock input.

21 SDTO I Serial data input.

22 SENS O SENS output.

23 XLAT I Latch input.

24 XSOE I CPU serial data output enable signal input.

25 SYSM I Mute input. “H” : MUTE

26 WDCK O Word clock output.

27 SCOR O SCOR output.

28 XRST I Reset terminal.

29 PWMI I Spindle moter external control input.

30 XQOK I/O Not used (OPEN).

31 XWRE I/O Not used (Fixed at “L”).

32 R4M O System clock output.

33 Vss0 – Digital ground terminal.

34 SQCK I Not used (Fixed at “H”).

35 SCLK I Not used (Fixed at “H”).

36 SQSO O Not used (OPEN).

37 XEMP O Not used (OPEN).

38 XWIH O Not used (OPEN).

39 SBSO O Not used (OPEN).

40 EXCK I Not used (Fixed at “L”).

41 XTSL I Not used (Fixed at “L”).

42 HVss – Ground terminal for headphones.

43 HPL O Not used (OPEN).

44 HPR O Not used (OPEN).

45 HVDD – Power supply terminal for headphones.

46 XVDD – Power supply terminal for master clock.

47 XTAI I Master clock input (16.9MHz).

48 XTAO O Master clock output (16.9MHz).

49 XVss – Ground terminal for master clock.

50 AVDD1–Power supply terminal for DAC block.

51 AOUT1 O Audio out (L-CH).

52 VREFL O VREF terminal (L-CH).

53 AVss1 – Ground terminal DAC block.

54 AVss2 – Ground terminal DAC block.

Loading...

Loading...