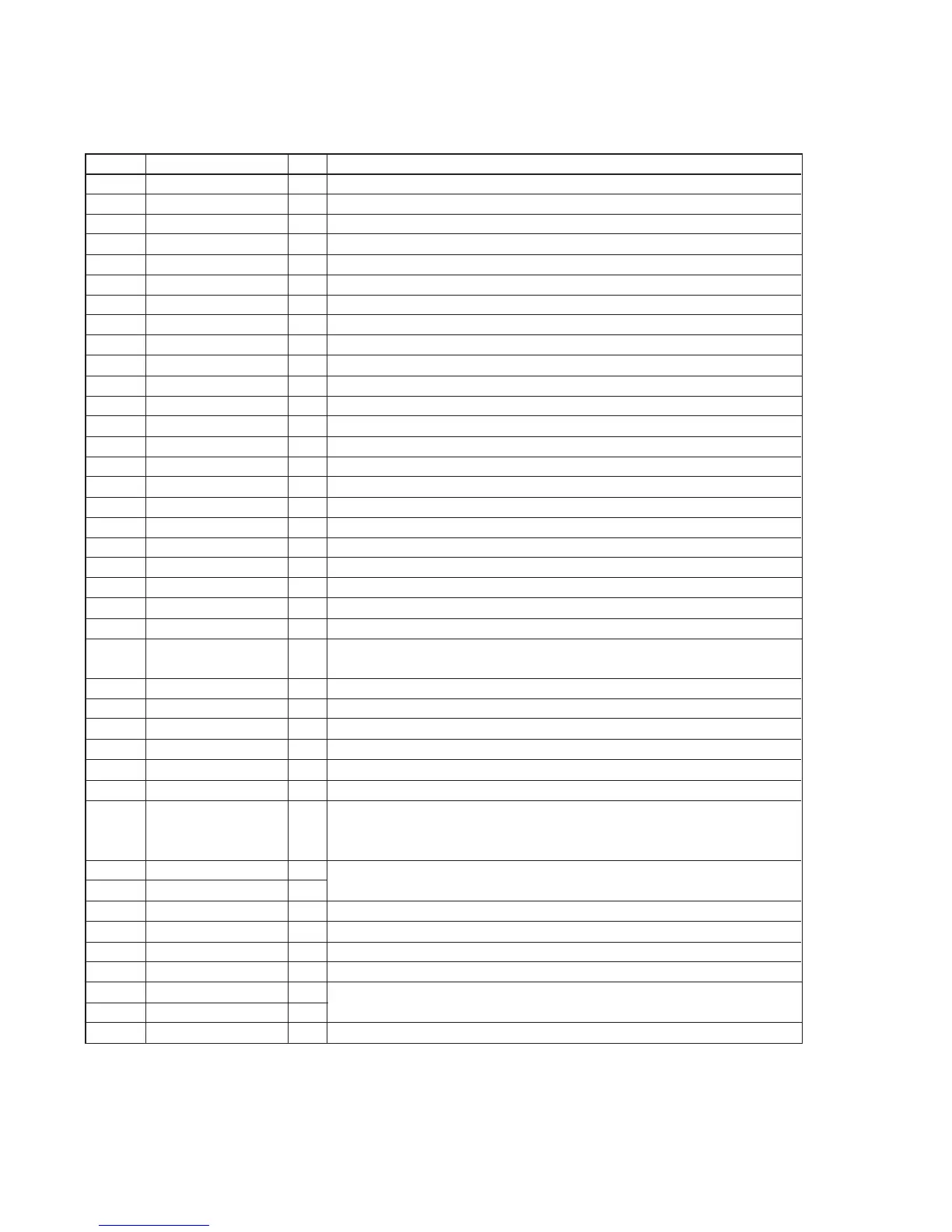

— 60 —

Function

Address output to external RAM. Address 13

Address output to external RAM. Address 8

Address output to external RAM. Address 9

Address output to external RAM. Address 11

Ground

Output enable signal to external RAM. Active at “L”

Address output to external RAM. Address 10

Data terminal with external RAM. For erasure pointer

Data terminal with external RAM. Data bus 7

Data terminal with external RAM. Data bus 6

Data terminal with external RAM. Data bus 5

Data terminal with external RAM. Data bus 4

Data terminal with external RAM. Data bus 3

Data terminal with external RAM. Data bus 2

Data terminal with external RAM. Data bus 1

Data terminal with external RAM. Data bus 0

Power supply (+5V)

Ground

VCXO output (Not used)

VCXO input

For testing IC (Fixed at “L”)

Phase comparator output (3-state)

“H” when AC-3 sync signal. For monitor (Not used)

Muting output. Muting at “H”

“H” when “MUTI=H” or not synchronized with AC-3

Parity flag output. Data is correct when “L”. Data may be incorrect if “H” (Not used)

L/Rch switching clock. 48 kHz. Lch when “H” (Not used)

Bit clock. 3.072 MHz (Not used)

Serial data output (Not used)

Digital out preamble B identification signal (Not used)

Digital output

A13

A8

A9

A11

GND

OE

A10

DBP

DB7

DB6

DB5

DB4

DB3

DB2

DB1

DB0

VDD

GND

VO

VI

TSTIN3

PDO

MSYC

MUTO

VLDY

LRCK

BCK

SDO

DASYO

DAOUT

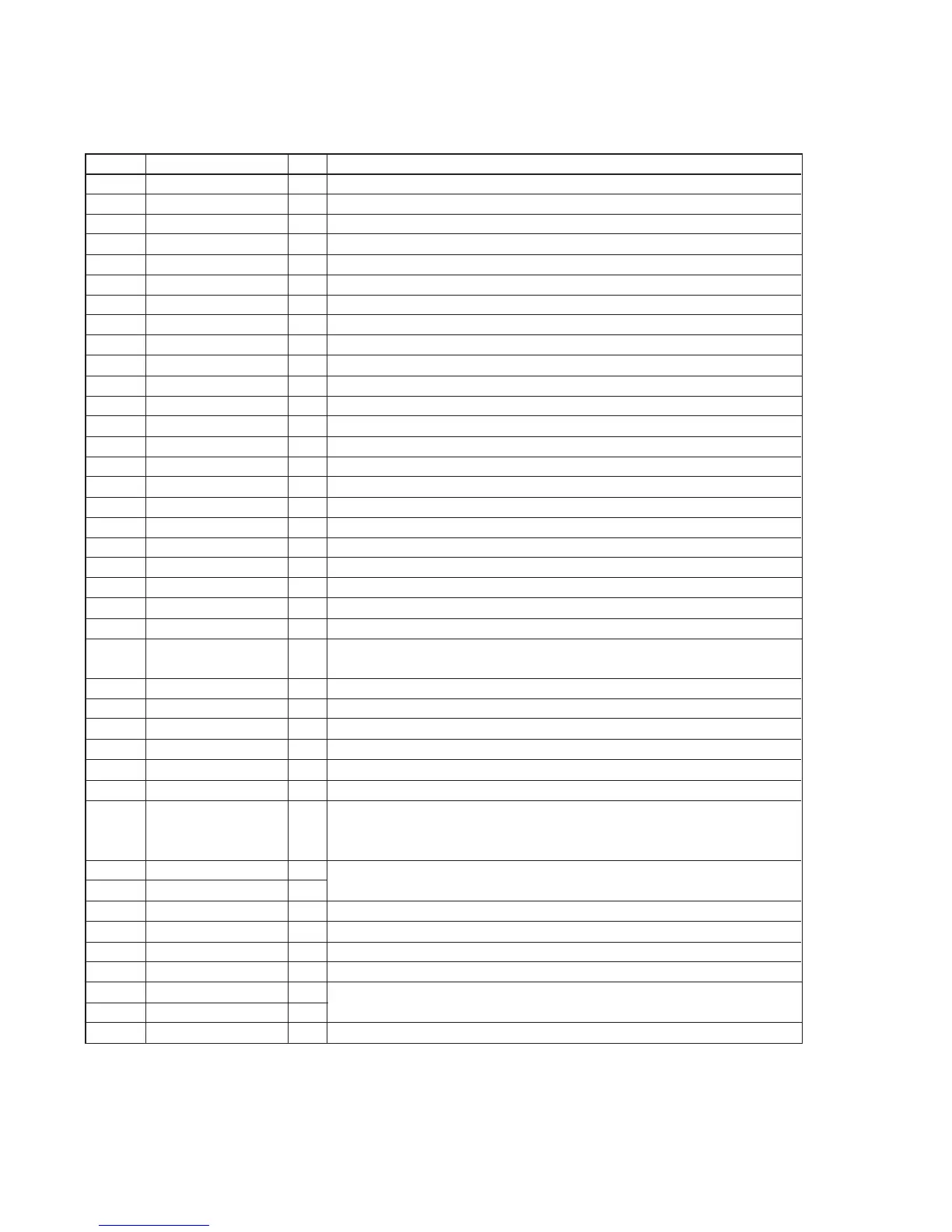

DAIN

TSTIN4

TSTIN5

C2F1

C2F0

C1F1

C1F0

DRY

DEN

ECCK

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

O

O

O

O

–

O

O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

–

–

O

I

I

O

O

O

O

O

O

O

O

O

I

I

I

O

O

O

O

O

O

O

FunctionPin No. Pin Name

I/O

For testing IC (Not used)

C2 error correction state display. Outputs if corrected properly (Not used)

C2 error correction state display. Outputs number of errors at C2 (Fixed at “H”)

C1 error correction state display. Outputs whether error is present at C1 (Fixed at “H”)

C1 error correction state display. Outputs number of errors at C1 (Fixed at “H”)

For monitoring error correction (Not used)

Error correction sector clock. 576 kHz (Not used)

Digital audio interface signal input

Select a digital output processed inside IC by internal register setting or signal from “DAIN”

and output to “DAOUT” (Not used)

Loading...

Loading...