– 57 –

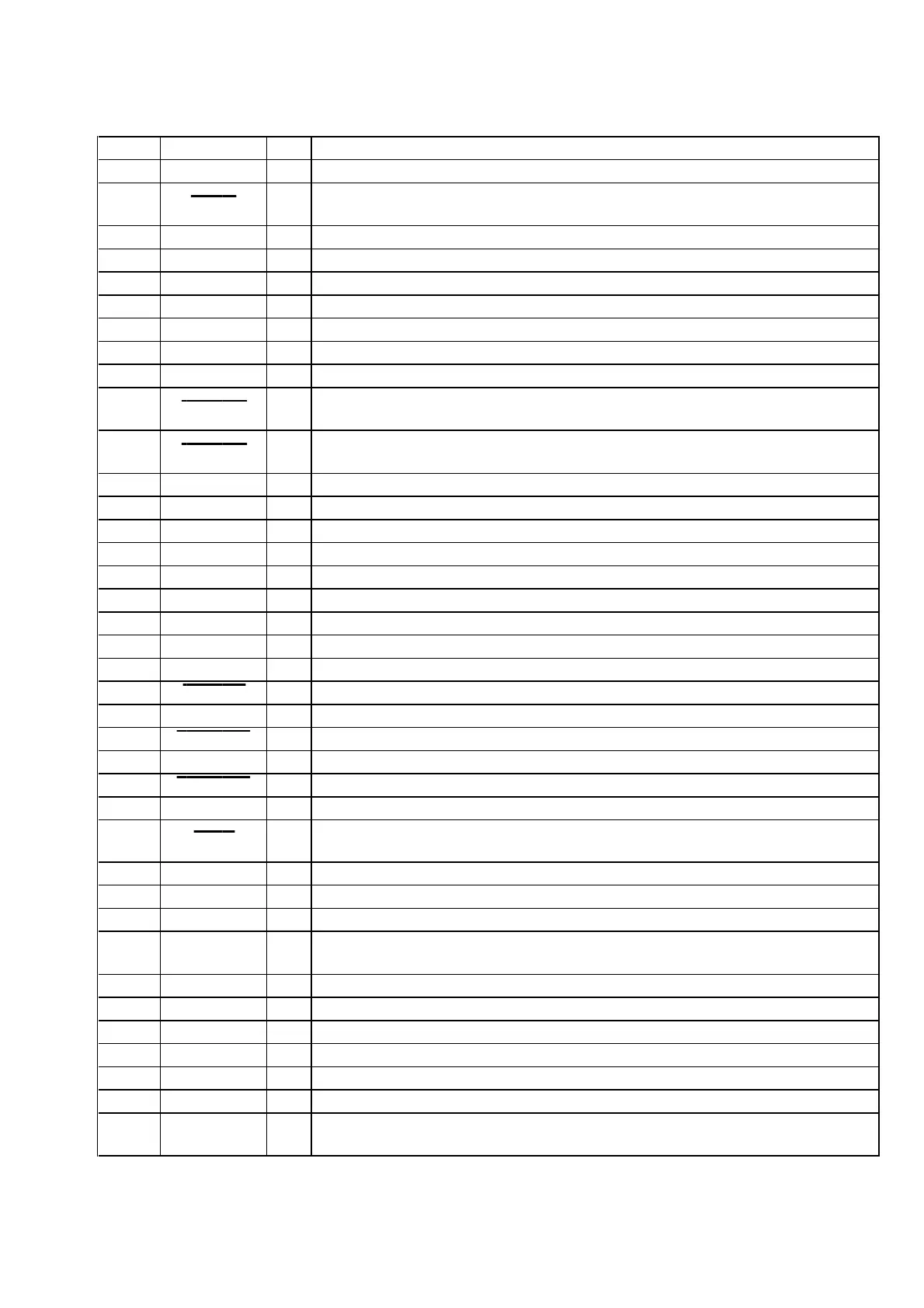

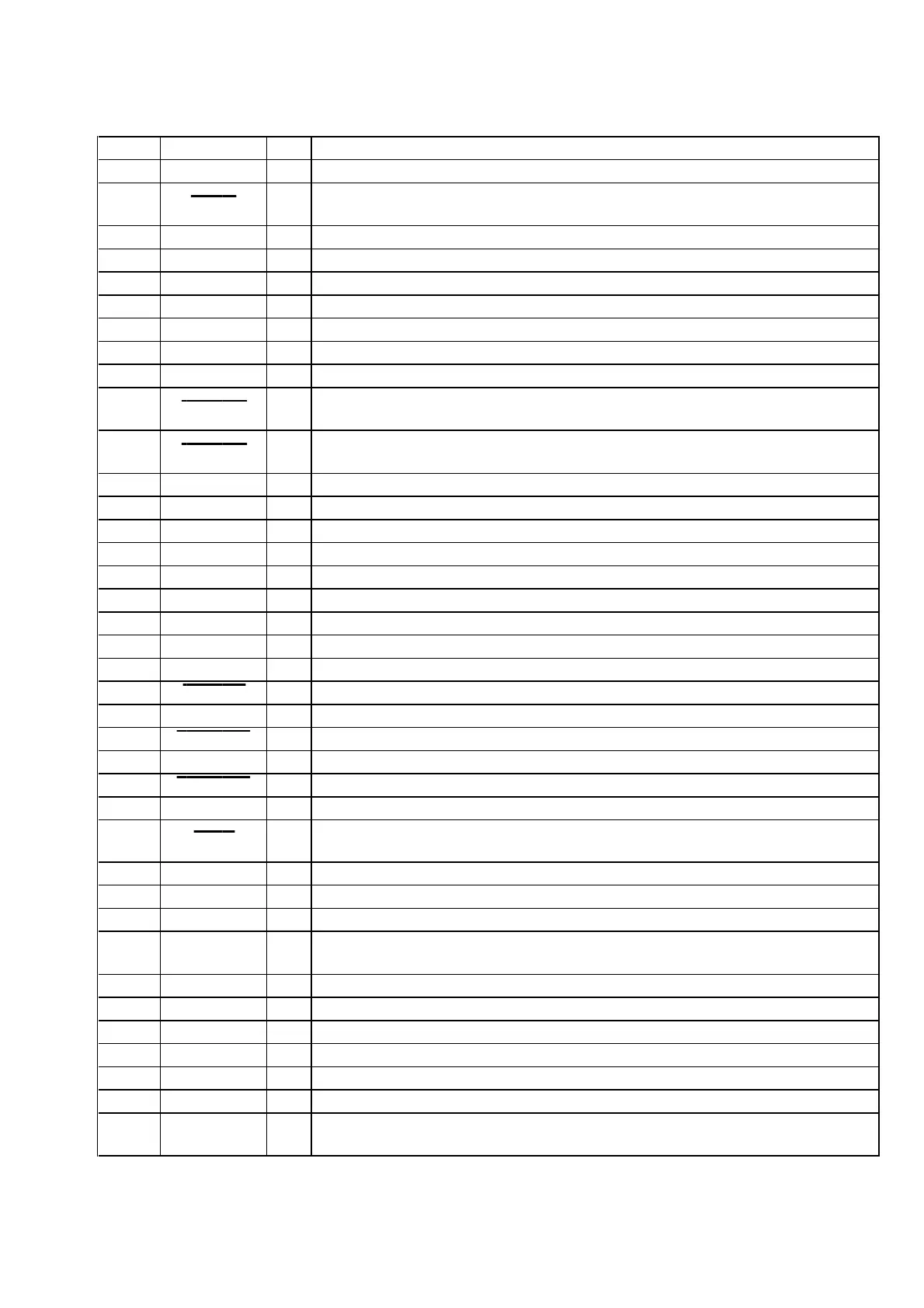

• HAND MAIN BOARD IC603 MB89174LPF-G-289-BND (SYSTEM CONTROLLER)

Pin No. Pin Name I/O Description

1 NC O Not used (open)

2 RESET I

System reset signal input from the reset signal generator (Q615) “L”: reset

For several hundreds msec. after the power supply rises, “L” is input, then it changes to “H”

3, 4 MOD0, MOD1 I Setting terminal for the CPU operational mode Fixed at “L” in this set

5 X0 I Main system clock input terminal (3.579545 MHz)

6 X1 O Main system clock output terminal (3.579545 MHz)

7VCC— Power supply terminal (+3V)

8 X0A I Sub system clock input terminal Not used (fixed at “L”)

9 X1A O Sub system clock output terminal Not used (open)

10 NC O Not used (open)

11 TX MUTE O

Muting control signal output to the IR3N74AN (IC602) “L”: muting on

At TX mode: During sending data to base unit, muting it

12 RX MUTE O

Muting control signal output to the IR3N74AN (IC602) “L”: muting on

At RX mode: After receiving premble bits from base unit muting it until data sent finished

13 SC O Main system power supply (+3V) on/off control signal output “H”: main system power on

14 NC O Not used (open)

15, 16 TALK LED O LED drive signal output of the TALK/BATT LOW indicator (D607) “L”: LED on

17 KEY LED O LED drive signal output of the key back light (D609 to D612) “L”: LED on

18 NC O Not used (open)

19 GND — Ground terminal

20 NC O Not used (open)

21 to 25 ROW5 to ROW1 I Key scan signal input from the key matrix

26 STPCNT O Wakeup control signal output terminal

27 WAKEUP I Wakeup input terminal

28 NC O Not used (open)

29 BATT OFF I Battery level detect signal input from the XC612N3328MR (IC605) “L”: battery off

30 to 34 COL5 to COL1 O Key scan signal output to the key matrix

35 BATT LOW I Battery level detect signal input from the XC612N3328MR (IC605) “L”: battery low level

36 CHG IN I Charge detection signal input terminal “H”: charge on

37 CONV O

Speaker output circuit power supply on/off control signal output

“L”: speaker output circuit power on

38 RING OUT O Buzzer sound drive signal output terminal

39 RING VOL O Buzzer sound level control signal output terminal “L”: low level, “H”: high level

40 DATA IN I Receive data input terminal

41 SQ IN I

Squelch signal (carrier detection signal) input from the MC3361CDR2 (IC601)

“L”: carrier present, “H”: no carrier

42 TX B O TX system power supply on/off control signal output “L”: TX system power on

43 GND — Ground terminal

44 DATA OUT O Transmit data output terminal

45 DATA EN O Transmit data enable signal output terminal

46 PLL CLK O PLL serial data transfer clock signal output to the M64884FP (IC502)

47 PLL DATA O PLL serial data output to the M64884FP (IC502)

48 PLL EN O

Chip enable signal output to the M64884FP (IC502)

When PLL EN goes from “L” to “H”, it load data from PLL DATA

Loading...

Loading...