4-22

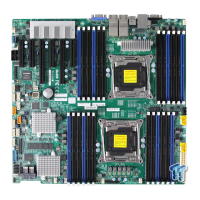

X10DRC/i-LN4+/-T4+ Motherboard User’s Manual

The following PCI information will be displayed:

• PCI Bus Driver Version

• PCI Device Common Settings

PCI Latency Timer

Select 32 to set the PCI latency timer to 32 PCI clock cycles. The options are 32,

64, 96, 128, 160, 192, 224, and 248 (PCI Bus Clocks).

PCI-X Latency Timer

bus. Select 32 to set the PCI latency timer to 32 PCI clock cycles. The options are

32, 64, 96, 128, 160, 192, 224, and 248 (PCI Bus Clocks).

PCI PERR/SERR Support

Select Enabled to support PERR (PCI/PCI-E Parity Error)/SERR (System Error)

runtime error reporting for a PCI/PCI-E slot. The options are Enabled and Disabled.

Above 4G Decoding (Available if the system supports 64-bit PCI decoding)

Select Enabled to decode a PCI device that supports 64-bit in the space above 4G

Address. The options are Enabled and Disabled.

SR-IOV (Available if the system supports Single-Root Virtualization)

Select Enabled for Single-Root IO Virtualization support. The options are Enabled

and Disabled.

Maximum Payload

Select Auto for the system BIOS to automatically set the maximum payload value

for a PCI-E device to enhance system performance. The options are Auto, 128

Bytes, and 256 Bytes.

Maximum Read Request

Select Auto for the system BIOS to automatically set the maximum size for a read

request for a PCI-E device to enhance system performance. The options are Auto,

128 Bytes, 256 Bytes, 512 Bytes, 1024 Bytes, 2048 Bytes, and 4096 Bytes.

Loading...

Loading...