51

Chapter 2: Installation

S-SGPIO Header

A Serial General Purpose Input/Output header (S-SGPIO) is located on the motherboard.

This header is used to communicate with the enclosure management chip on the backplane.

See the table below for pin denitions.

SGPIO Header

Pin Denitions

Pin# Denition Pin# Denition

1 NC 2 NC

3 Ground 4 DATA Out

5 Load 6 Ground

7 Clock 8 NC

NC = No Connection

Disk-On-Module Power Connector

The Disk-On-Module (DOM) power connectors at JSD1 and JSD2 provide 5V power to a

solid-state DOM storage devices connected to one of the SATA ports. See the table below

for pin denitions.

DOM Power

Pin Denitions

Pin# Denition

1 5V

2 Ground

3 Ground

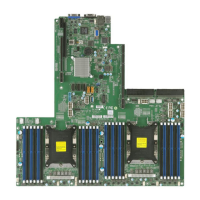

1. S-SGPIO

2. JSD1

3. JSD2

COM1

LAN

CTRL

DESIGNED IN USA

X11DPX-T

REV:1.01A

I-SATA4~7 I-SATA0~3

FANC FAND

CPU2

CPU1

BIOS

LICENSE

JBT1

M.2 CONNECTOR

SAN MAC

MAC CODE

JF1

BAR CODE

IPMI CODE

VGA

USB 2/3

BT1

JNVI2C2

JNVI2C1

PCH

FANA

FAN2

FAN5

FAN1

P2-DIMMC1

P2-DIMMB1

P2-DIMMA1

P2-DIMMA2

P2-DIMMD2

P2-DIMMD1

P2-DIMME1

P2-DIMMF1

FAN6

P1-DIMMA2

P1-DIMMA1

P1-DIMMB1

P1-DIMMC1

JPWR1

JPWR2

JPWR3

JPI2C1

FAN4

LEDBMC

S-UM12

S-SATA0

S-SATA1

FANB

FAN3

JNCSI1

S-SGPIO

JSTBY1

JWD1

JSEN1

COM2

P1-DIMMF1

P1-DIMME1

P1-DIMMD1

P1-DIMMD2

SP1

USB8 (3.0)

JTPM1

JPWR4

ALWAYS POPULATE DIMMx1 FIRST

ALWAYS POPULATE DIMMx1 FIRST

ALWAYS POPULATE DIMMx1 FIRST

ALWAYS POPULATE DIMMx1 FIRST

JUIDB1

(UID)

LED2

(UID-LED)

USB 6/7 (3.0)

JL1

LEDPWR

JSD1

JSD2

JIPMB1

JRK1

JPTG1

JPCIE11

(CPU2 SLOT11 PCI-E 3.0 x4 (IN x8))

JPME2

LAN 2 LAN 1

USB 0/1

IPMI_LAN

USB 4/5 (3.0)

BMC

JPCIE2

(CPU1 SLOT2 PCI-E 3.0 x16)

JPCIE1

(CPU1 SLOT1 PCI-E 3.0 x8)

JPCIE3

(CPU1 SLOT3 PCI-E 3.0 x8)

JPCIE6

(CPU2 SLOT6 PCI-E 3.0 x16)

JPCIE5

(CPU2 SLOT5 PCI-E 3.0 x8)

JPCIE7

(CPU1 SLOT7 PCI-E 3.0 x8)

JPCIE8

(CPU2 SLOT8 PCI-E 3.0 x16)

JPCIE4

(CPU1 SLOT4 PCI-E 3.0 x16)

JPCIE9

(CPU2 SLOT9 PCI-E 3.0 x8)

JPCIE10

(CPU2 SLOT10 PCI-E 3.0 x8)

1

2

3

Loading...

Loading...