48

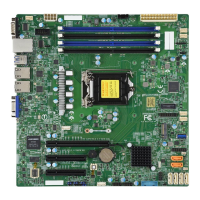

Super X11SCH-F/-LN4F User's Manual

DESIGNED IN USA

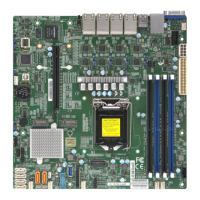

X11SCH-F

REV:1.01

IPMI CODE

BAR CODE

MAC CODE

MEGERAC

LICENSE

1

+

+

Intel

C246

ASpeed

AST2500

JSTBY1

JTPM1

JPWR1

JF1

I-SATA6

I-SATA7

I-SATA0

I-SATA4

I-SATA5

I-SATA3

I-SATA2

I-SATA1

I-SGPIO2

I-SGPIO1

JPWR2

JD1

JPI2C1

FANB

FAN4

FAN3

FAN2

FAN1

FANA

JIPMB1

JSD1

JSD2

JPG1

JPME2

JWD1

BT1

JLD2

JOH1

JL1

SP1

MH12

MH11

MH10

JUIDB1

LEDSSD2

LEDSSD1

LE1

LEDBMC

LEDPWR

JBT1

MH13

JLD1

M.2-P_2

M.2-P_1

LAN2/LAN4

USB8(3.0)

USB9/10(3.0)

USB4/5

USB2/3

COM1

USB0/1

IPMI_LAN

USB6/7(3.0)

LAN1/LAN3

VGA

CPU SLOT6 PCI-E 3.0 X8(IN X16)

CPU SLOT5 PCI-E 3.0 X8

CPU

NMI

JF1

LED

PWR

X

LED

HDD

NIC

LED

UID

2

NIC

1

RST

PWR

ON

FAIL

PS

COM2

DIMMA1

DIMMA2

DIMMB1

DIMMB2

Intel

i210

Intel

i210

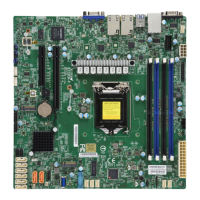

SGPIO Headers

There are two Serial Link General Purpose Input/Output (I-SGPIO1, I-SGPIO2) headers

located on the motherboard. The SGPIO headers are used to communicate with the enclosure

management chip on the back panel.

1. Chassis Intrusion Header

2. I-SGPIO1 Header

3. I-SGPIO2 Header

1

32

Chassis Intrusion

A Chassis Intrusion header is located at JL1 on the motherboard. Attach the appropriate cable

from the chassis to inform you of a chassis intrusion when the chassis is opened. Refer to

the table below for pin denitions.

Chassis Intrusion

Pin Denitions

Pin# Denition

1 Intrusion Input

2 GND

SGPIO Header

Pin Denitions

Pin# Denition Pin# Denition

1 NC 2 NC

3 GND 4 DATA Out

5 Load 6 GND

7 Clock 8 NC

NC = No Connection

I-SGPIO 1/2

I-SGPIO1 I-SATA 3.0 Ports 0-3

I-SGPIO2 I-SATA 3.0 Ports 4-7

Loading...

Loading...