8088

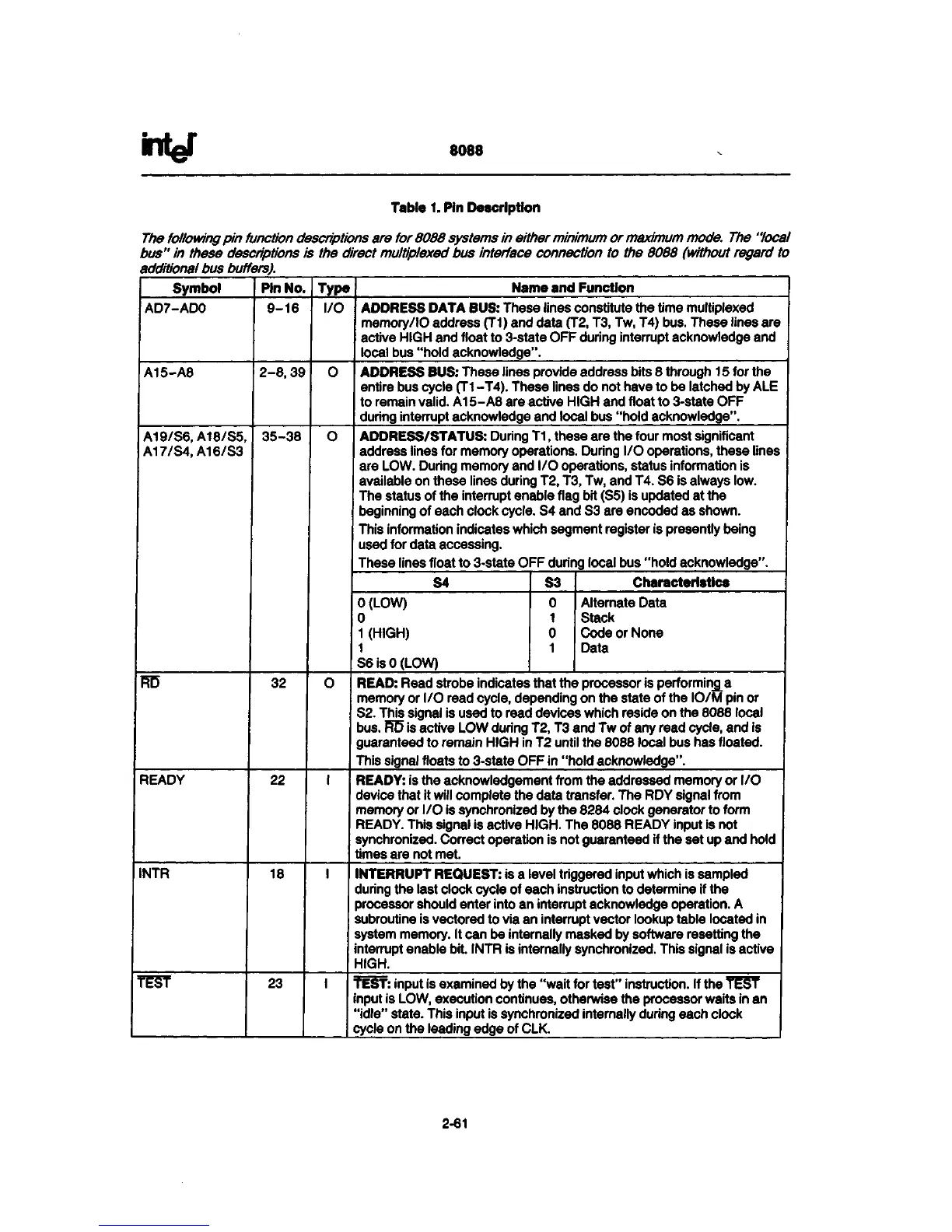

Table

1.

Pin Description

The

following pin function descriptions are for 8088 systems in either

minimum

or

maximum

mode.

The "local

bus" in these descriptions is the direct multiplexed bus interface connection to the 8088 (without regard to

additional bus buffers).

Symbol

AD7-AD0

A15-A8

A19/S6.A18/S5

A17/S4.A16/S3

m

READY

INTR

TEST

Pin

No

9-16

2-8,

39

35-38

32

22

18

23

Type

I/O

0

0

0

I

I

I

Name and Function

ADDRESS DATA

BUS:

These lines constitute the time multiplexed

memory/IO address (T1) and data

(T2,

T3, Tw, T4)

bus.

These lines are

active HIGH and float to

3-state

OFF during interrupt acknowledge and

local bus "hold acknowledge".

ADDRESS

BUS:

These lines provide address bits 8 through 15 for the

entire bus cycle (T1-T4). These lines do not have to be latched by ALE

to remain

valid.

A15-A8 are active HIGH and float to

3-state

OFF

during interrupt acknowledge and local bus "hold acknowledge".

ADDRESS/STATUS: During

T1,

these are the four most significant

address lines for memory operations. During I/O operations, these lines

are LOW. During memory and I/O operations, status information is

available on these lines during

T2,

T3, Tw, and

T4.

S6 is always low.

The status of the interrupt enable flag bit (S5) is updated at the

beginning of each clock

cycle.

S4 and S3 are encoded as shown.

This information indicates which segment register is presently being

used for data accessing.

These lines float to

3-state

OFF during local bus "hold acknowledge".

S4

0(LOW)

0

1 (HIGH)

1

S6isO(LOW)

S3

0

1

0

1

Characteristics

Alternate Data

Stack

Code or None

Data

READ:

Read strobe indicates that the processor is performing a

memory or I/O read

cycle,

depending on the state of the IO/M pin or

S2.

This signal is used to read devices which reside on the 8088 local

bus.

RU is active LOW during

T2,

T3 and Tw of any read cycle, and is

guaranteed to remain HIGH in T2 until the 8088 local bus has floated.

This signal floats to

3-state

OFF in "hold acknowledge".

READY: is the acknowledgement from the addressed memory or I/O

device that it will complete the data transfer. The RDY signal from

memory or I/O is synchronized by the 8284 clock generator to form

READY. This signal is active

HIGH.

The 8088 READY input is not

synchronized. Correct operation is not guaranteed if the set up and hold

times are not met.

INTERRUPT REQUEST: is a level triggered input which is sampled

during the last clock cycle of each instruction to determine if the

processor should enter into an interrupt acknowledge operation. A

subroutine is vectored to via an interrupt vector lookup table located in

system memory. It can be internally masked by software resetting the

nterrupt enable bit. INTR is internally synchronized. This signal is active

HIGH.

TE§T: input is examined by the "wait for test" instruction. If the TEST

nput is LOW, execution continues, otherwise the processor waits in an

'idle"

state. This input is synchronized internally during each clock

cycle on the leading edge of CLK.

2-61

Loading...

Loading...