Theory of Operation—492/492P Service Vol. 1 (SN B030000 & up)

From the filter, the signal is applied to broadband

feedback amplifier Q1023, which is biased at a relatively

substantial output current (approximately 50 mA) to exhibit

good intermodulation distortion performance. This perfor

mance is provided primarily through the large current capac

ity, by negative feedback through resistor R1025 and by

emitter degeneration resistor R1023.

At the output of amplifier Q1023 is a 6 dB attenuator that

provides a clean 50 Ω output to the 1 st Filter Select circuits

and reflects a 50 Ω termination back through the amplifier

for proper termination of the 1.2 MHz bandpass filter. The

output signal is transmitted via jumper B.

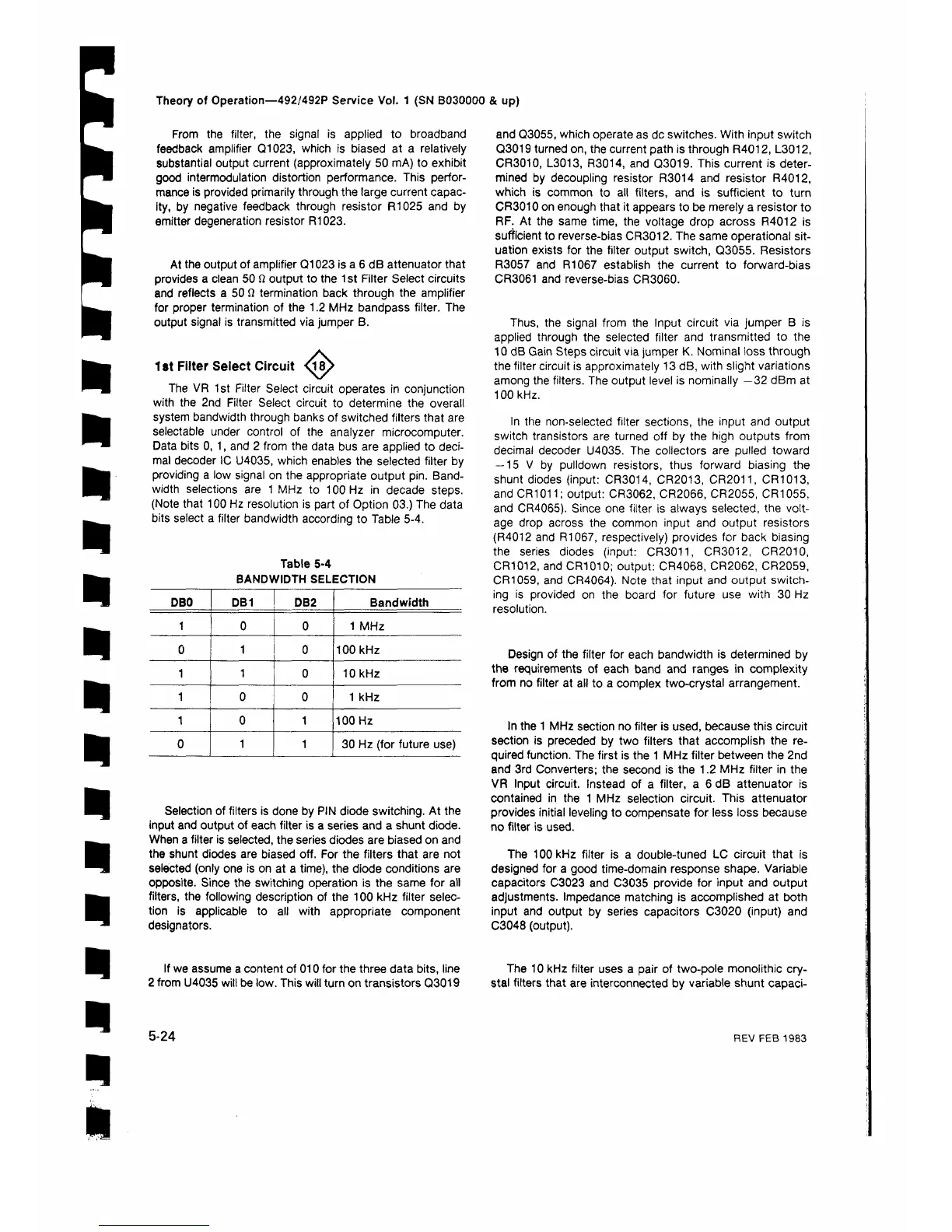

1st Filter Select Circuit

The VR 1st Filter Select circuit operates in conjunction

with the 2nd Filter Select circuit to determine the overall

system bandwidth through banks of switched filters that are

selectable under control of the analyzer microcomputer.

Data bits 0, 1, and 2 from the data bus are applied to deci

mal decoder IC U4035, which enables the selected filter by

providing a low signal on the appropriate output pin. Band

width selections are 1 MHz to 100 Hz in decade steps.

(Note that 100 Hz resolution is part of Option 03.) The data

bits select a filter bandwidth according to Table 5-4.

Table 5-4

BANDWIDTH SELECTION

DBO

DB1

DB2 Bandwidth

1

0 0 1 MHz

0

1

0 100 kHz

1

1

0 10 kHz

1 0

0 1 kHz

1 0 1

100 Hz

0

1

1

30 Hz (for future use)

Selection of filters is done by PIN diode switching. At the

input and output of each filter is a series and a shunt diode.

When a filter is selected, the series diodes are biased on and

the shunt diodes are biased off. For the filters that are not

selected (only one is on at a time), the diode conditions are

opposite. Since the switching operation is the same for all

filters, the following description of the 100 kHz filter selec

tion is applicable to all with appropriate component

designators.

and Q3055, which operate as dc switches. With input switch

Q3019 turned on, the current path is through R4012, L3012,

CR3010, L3013, R3014, and Q3019. This current is deter

mined by decoupling resistor R3014 and resistor R4012,

which is common to all filters, and is sufficient to turn

CR3010 on enough that it appears to be merely a resistor to

RF. At the same time, the voltage drop across R4012 is

sufficient to reverse-bias CR3012. The same operational sit

uation exists for the filter output switch, Q3055. Resistors

R3057 and R1067 establish the current to forward-bias

CR3061 and reverse-bias CR3060.

Thus, the signal from the Input circuit via jumper B is

applied through the selected filter and transmitted to the

10 dB Gain Steps circuit via jumper K. Nominal loss through

the filter circuit is approximately 13 dB, with slight variations

among the filters. The output level is nominally —32 dBm at

100 kHz.

In the non-selected filter sections, the input and output

switch transistors are turned off by the high outputs from

decimal decoder U4035. The collectors are pulled toward

— 15 V by pulldown resistors, thus forward biasing the

shunt diodes (input: CR3014, CR2013, CR2011, CR1013,

and CR1011; output: CR3062, CR2066, CR2055, CR1055,

and CR4065). Since one filter is always selected, the volt

age drop across the common input and output resistors

(R4012 and R1067, respectively) provides for back biasing

the series diodes (input: CR3011, CR3012, CR2010,

CR1012, and CR1010; output: CR4068, CR2062, CR2059,

CR1059, and CR4064). Note that input and output switch

ing is provided on the board for future use with 30 Hz

resolution.

Design of the filter for each bandwidth is determined by

the requirements of each band and ranges in complexity

from no filter at all to a complex two-crystal arrangement.

In the 1 MHz section no filter is used, because this circuit

section is preceded by two filters that accomplish the re

quired function. The first is the 1 MHz filter between the 2nd

and 3rd Converters; the second is the 1.2 MHz filter in the

VR Input circuit. Instead of a filter, a 6 dB attenuator is

contained in the 1 MHz selection circuit. This attenuator

provides initial leveling to compensate for less loss because

no filter is used.

The 100 kHz filter is a double-tuned LC circuit that is

designed for a good time-domain response shape. Variable

capacitors C3023 and C3035 provide for input and output

adjustments. Impedance matching is accomplished at both

input and output by series capacitors C3020 (input) and

C3048 (output).

If we assume a content of 010 for the three data bits, line The 10 kHz filter uses a pair of two-pole monolithic cry-

2 from U4035 will be low. This will turn on transistors Q3019 stal filters that are interconnected by variable shunt capaci-

5-24

REV FEB 1983

Loading...

Loading...