Chapter 5 BIOS

30 AI5TV Motherboard User’s Manual

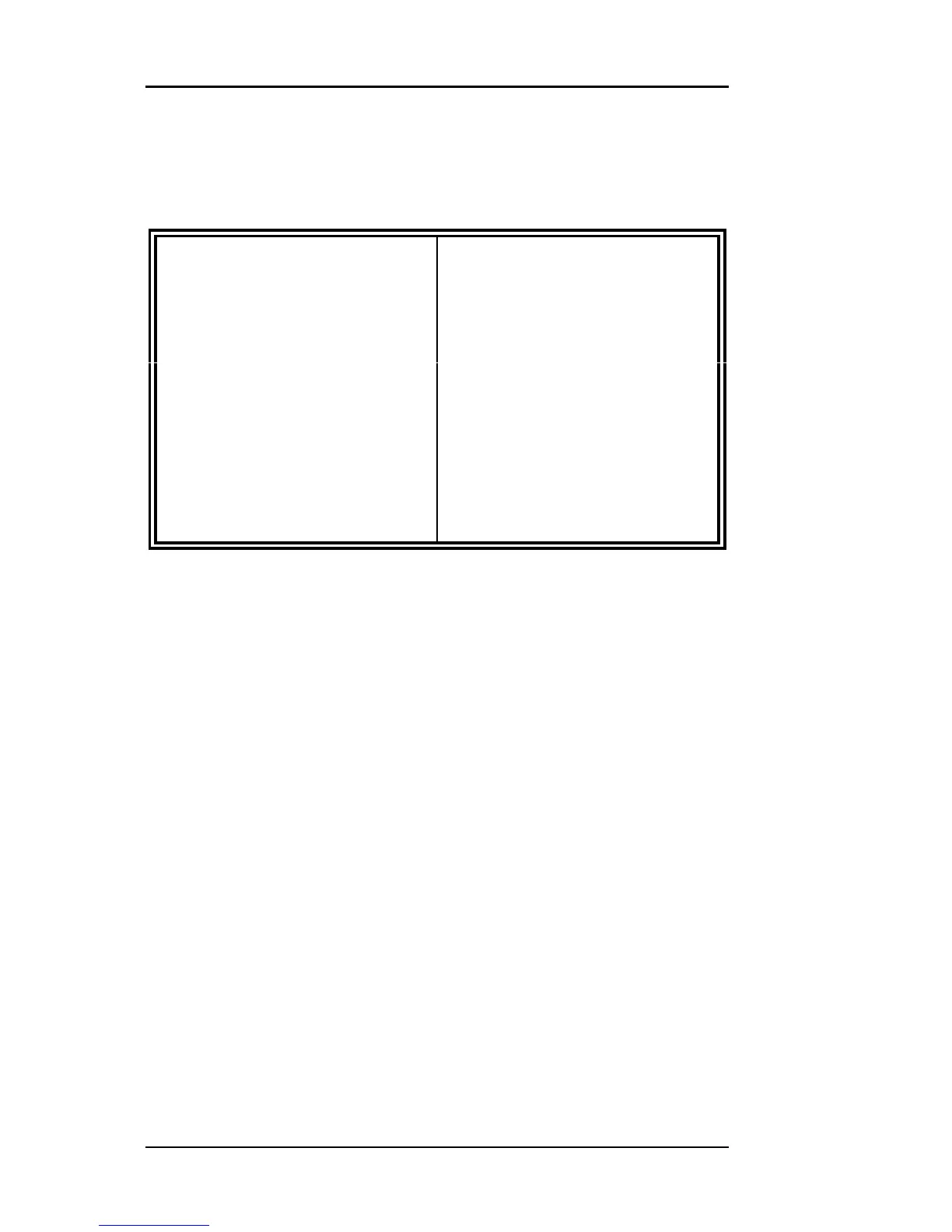

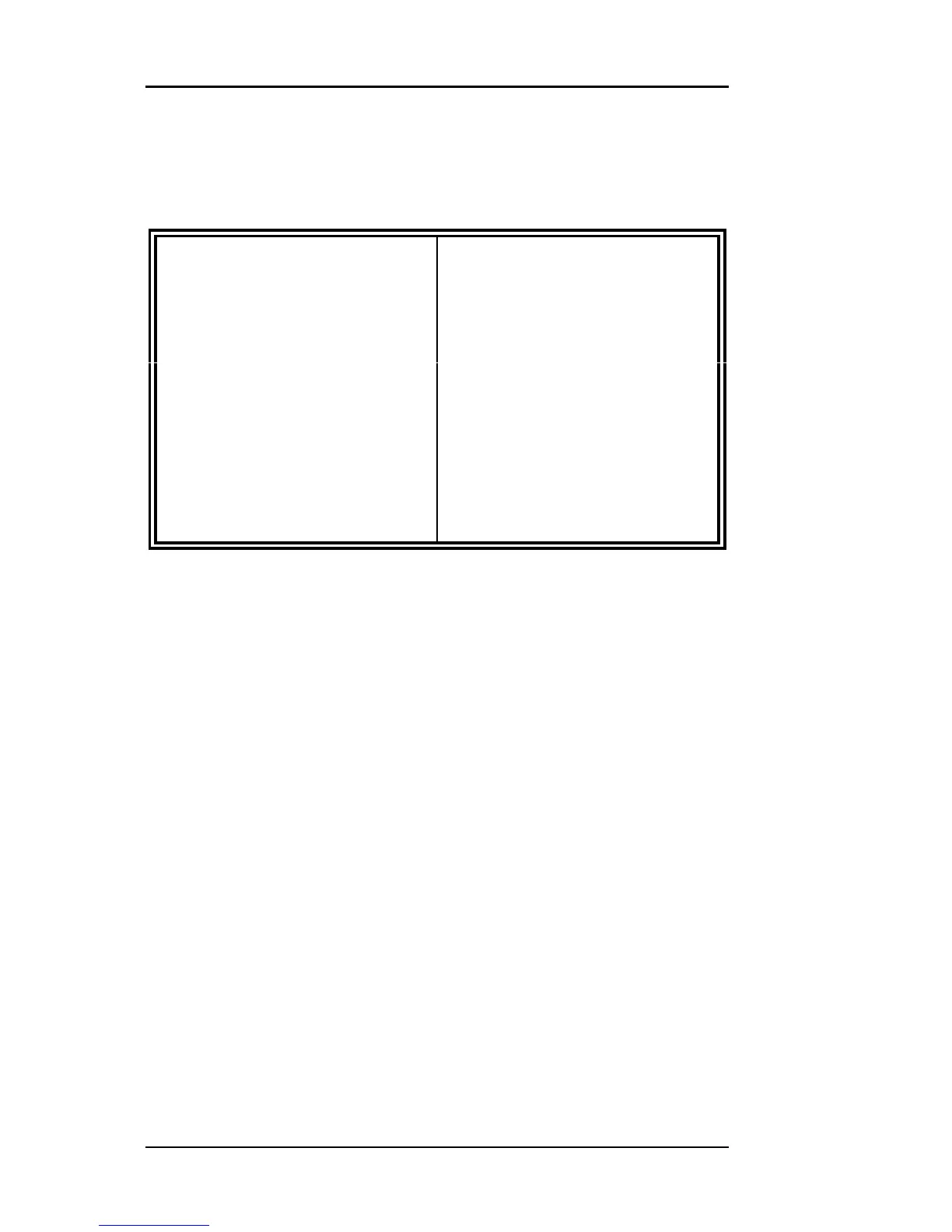

Chipset Features Setup

This Setup menu controls the configuration of the motherboard

chipset.

ROM PCI/ISA BIOS

CHIPSET FEATURES SETUP

AWARD SOFTWARE INC.

Auto Configuration : Enable

DRAM Timing 60ns

DRAM RAS# Precharge Time 3

DRAM R/W Leadoff Timing 6

Fast RAS To CAS Delay 3

DRAM Read Burst (EDO/FP) x222/x333

DRAM Write Burst Timing x3333

Fast MA to RAS# Delay CLK 1

Refresh Ras# Assertion 4CLKS

ISA Bus Clock PCI CLK/4

Pipeline Cache Timing Faster

System BIOS Cacheable Disabled

Video BIOS Cacheable Disabled ESC : Quit á â à ß : Select Item

8 Bit I/O Recovery Time 1 F1 : Help PU/PD/+/- : Modify

16 Bit I/O Recovery Time 1 F5 : Old Values (Shift) F2 : Color

Memory Hole At 15M-16M Disabled F6 : Load BIOS Defaults

Peer Concurrency Enabled F7 : Load Setup Defaults

Auto Configuration

This field predefined values for DRAM, cache timing according to

CPU type and system clock. When this field is enabled, the predefined

items will become read-only.

DRAM Timing

The DRAM timing is controlled by the DRAM Timing Registers. The

timing type is dependent on the system design. Slower rates may be

required in some system designs to support loose layouts or slower

memory.

DRAM RAS# Recharge Time

DRAM must continuously be refreshed or it will loose its data. This

option allows you to determine the number of CPU clocks allocated for

Row Address Strobe to accumulate its charge before DRAM is

refreshed. If refreshed time is not enough, refresh may be incomplete

and data will be lost.

DRAM R/W Leadoff Timing

This field allows you to set the number of CPU clocks before reads and

writes to DRAM. By default, it is set to 7/6 Leadoff timing.

Loading...

Loading...