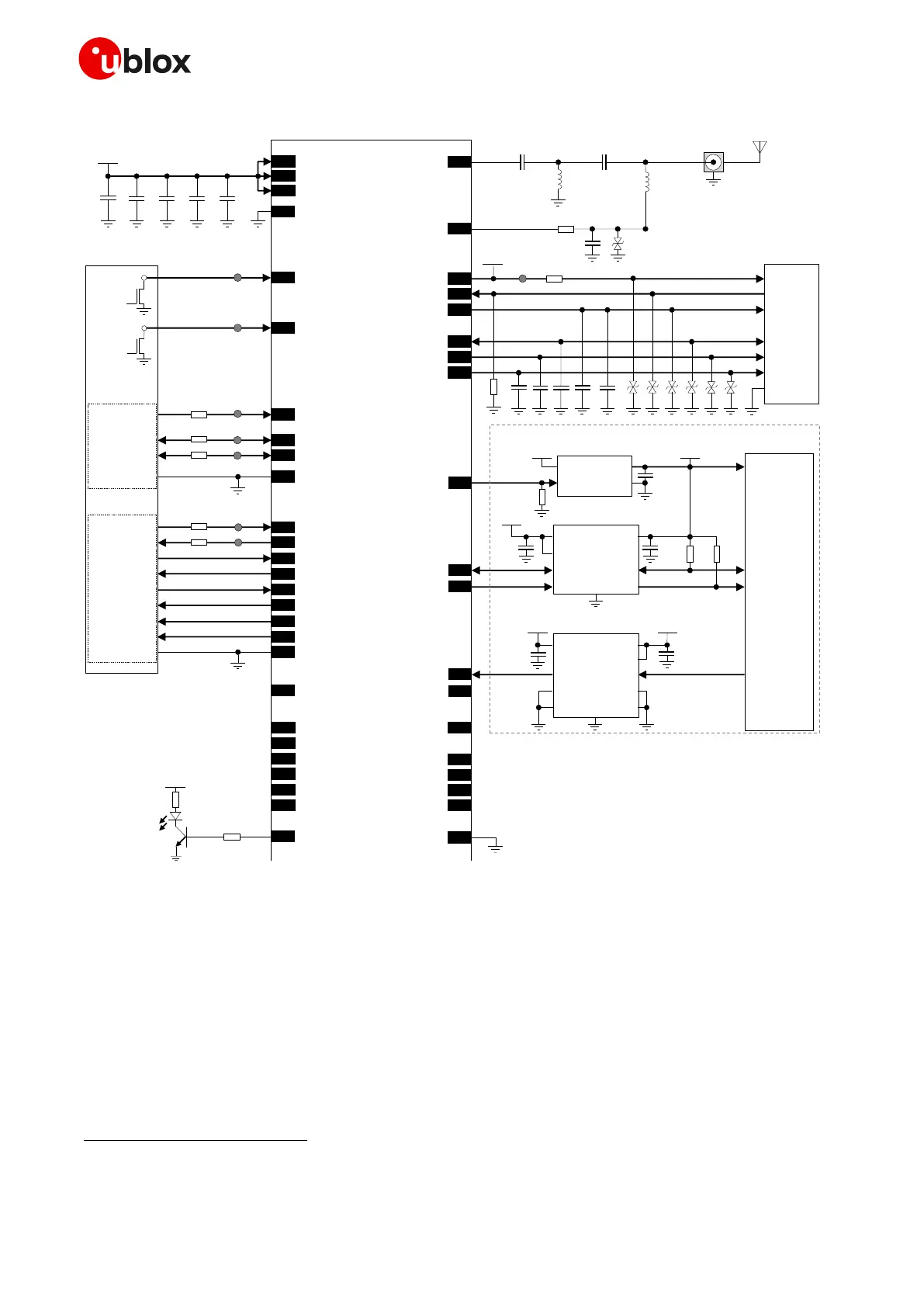

SARA-R4/N4 series - System Integration Manual

UBX-16029218 - R11 Design-in Page 117 of 157

3V8

GND

100uF 10nF

SARA-R4/N4

52 VCC

53 VCC

51 VCC

68pF

RSVD

18 RESET_N

Application

Processor

Open

drain

output

15 PWR_ON

Open

drain

output

TP

TP

12

TXD

13

RXD

8

DCD

10

RTS

11

CTS

9

DTR

6

DSR

7

RI

TP

TP

TXD

RXD

DCD

RTS

CTS

DTR

DSR

RI

1.8 V DTE

GND GND

USB 2.0 host

D-

D+

28

USB_D-

29

USB_D+

VBUS 17

VUSB_DET

TP

TP

GND GND

0Ω

0Ω

0Ω

0Ω

47pF

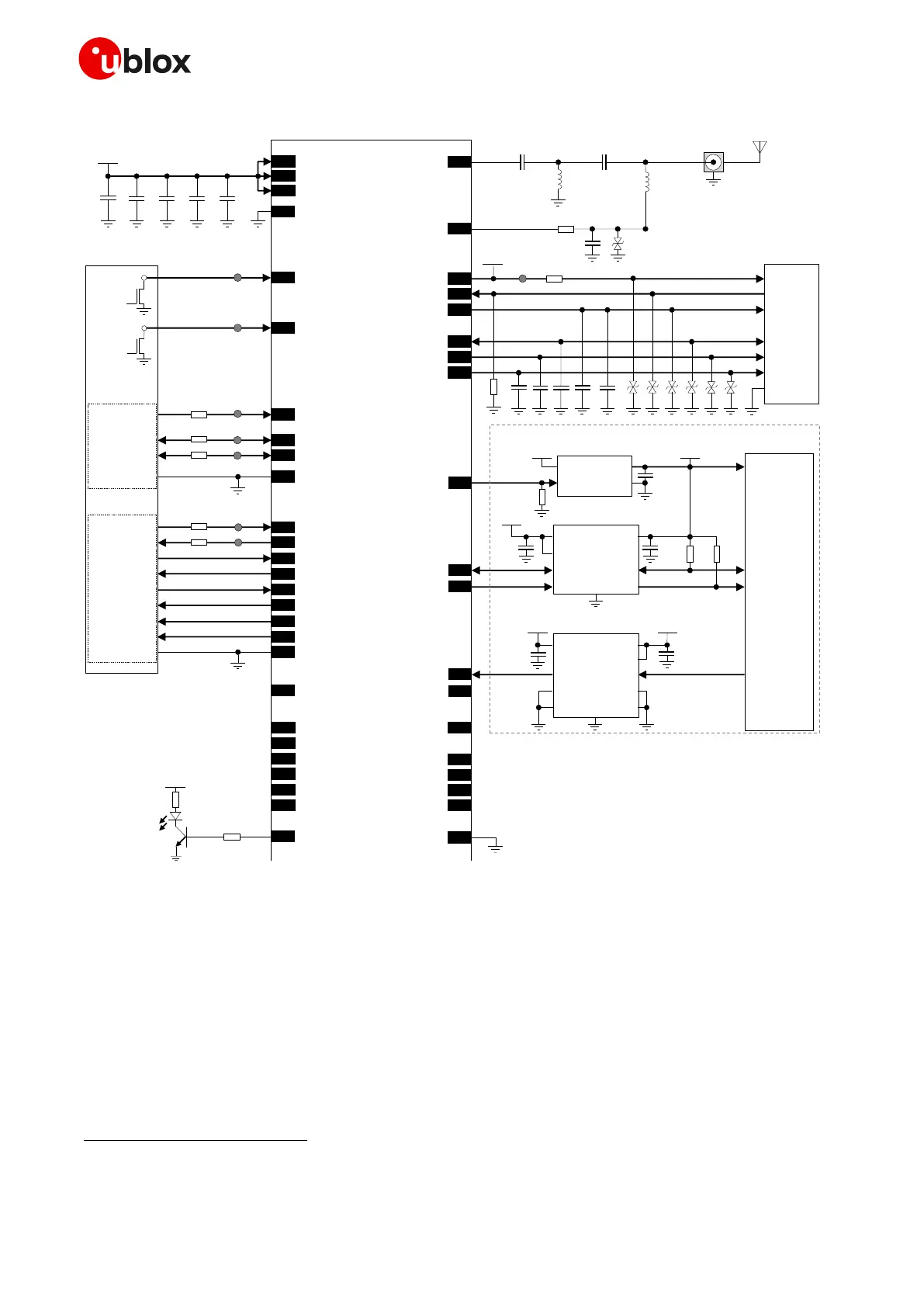

SIM Card

Holder

CCVCC (C1)

CCVPP (C6)

CCIO (C7)

CCCLK (C3)

CCRST (C2)

GND (C5)

47pF47pF 100nF

41VSIM

39SIM_IO

38SIM_CLK

40SIM_RST

47pF

SW1

SW2

4V_INT

42GPIO5

470k

ESD ESD ESD ESD ESD ESD

1k

TP

V_INT

62

ANT_DE

T

10k

27pF

ESD

68nH

56

Connect or

Ext ernal

antenna

33pF

ANT

TP

0Ω

39nH

15pF

15pF100nF

24GPIO3

V_INT

B1 A1

GND

B2 A2

VCCB VCCA

SN74AVC2T245

Volt age Translator

100nF

100nF

3V0

TxD1

4.7k

IN

OUT

LDO Regulat or

SHDNn

4.7k

3V8 3V0

23GPIO2

V_INT

SDA_A

SDA_B

GND

SCL_A

SCL_B

VCCA

VCCB

TCA9406

I2C Volt age Translator

100nF

100nF

100nF

47k

SDA2

SCL2

VCC

DIR1

DIR2OEn

OE

GND

EXTINT0GPIO4 25

u-blox GNSS

3.0 V receiver

26SDA

27SCL

Not support ed by ‘0 0 ’ and ‘0 1’ product version

GND

3V8

Network

Indicator

16

GPIO1

19GPIO6

SDIO_CMD

SDIO_D0

SDIO_D3

SDIO_D1

46

47

48

49

SDIO_D2

SDIO_CLK

44

45

36I2S_CLK / SPI_CLK

34I2S_WA / SPI_MOSI

35I2S_TXD / SPI_CS

37I2S_RXD / SPI_MISO

Figure 55: Example of schematic diagram to integrate a SARA-R4/N4 series module using all available interfaces

Flow control is not supported by ‘00’, ‘01’ and SARA-R410M-02B product versions, but the RTS input must be set low to use the UART on

‘00’ and ‘01’ versions. The DTR input must be set low to have URCs presented over UART on ‘00’, ‘01’ and ‘x2’ product versions.

Loading...

Loading...