Common Commands Introduction to Programming

Agilent 8163A/B, 8164A/B & 8166A/B Mainframes, Fifth Edition 31

Common Status Information

There are three registers for the status information. Two of these are

status-registers and one is an enable-registers. These registers conform to

the IEEE Standard 488.2-1987. You can find further descriptions of these

registers under

*ESE, *ESR?, and *STB?.

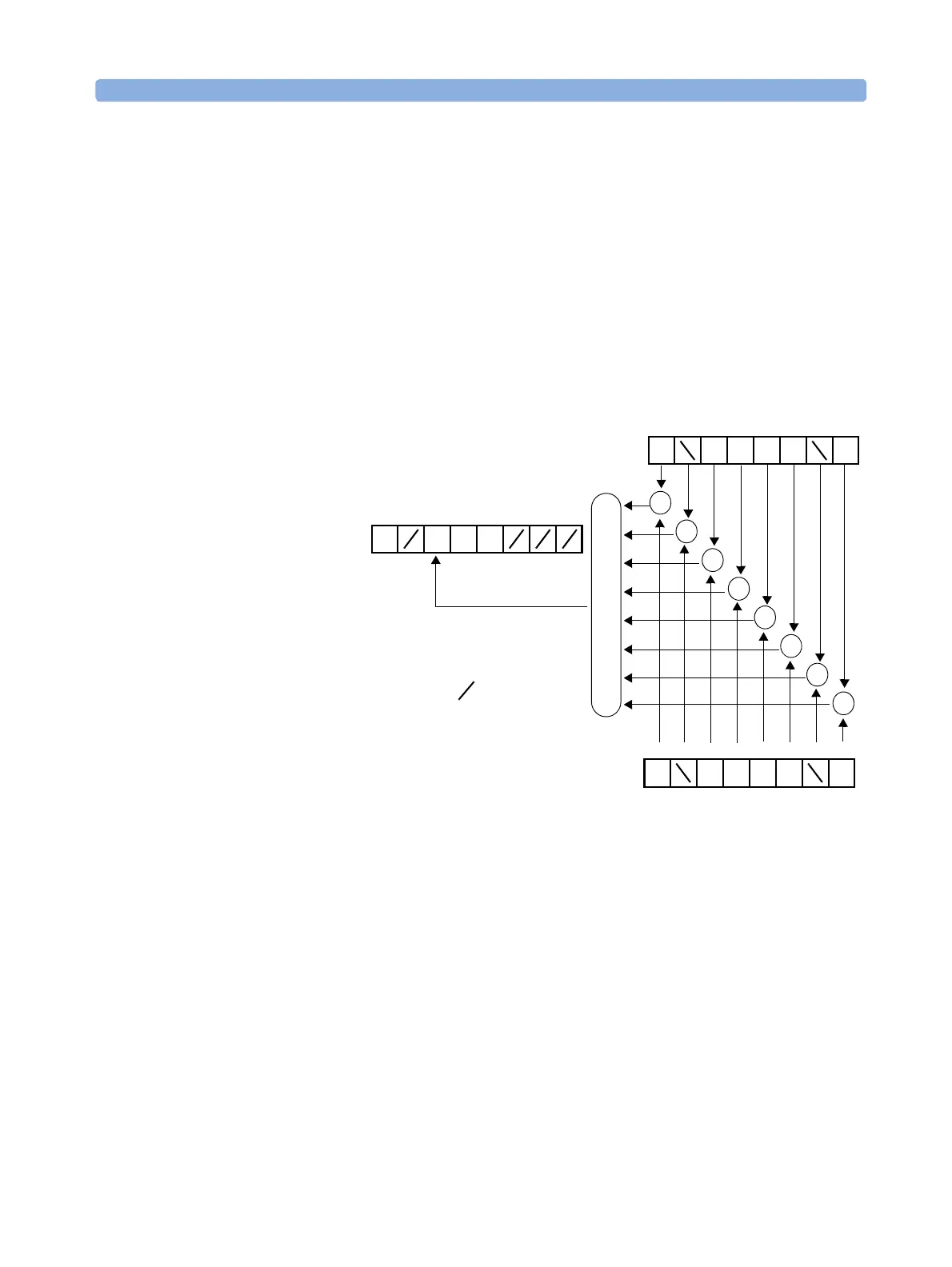

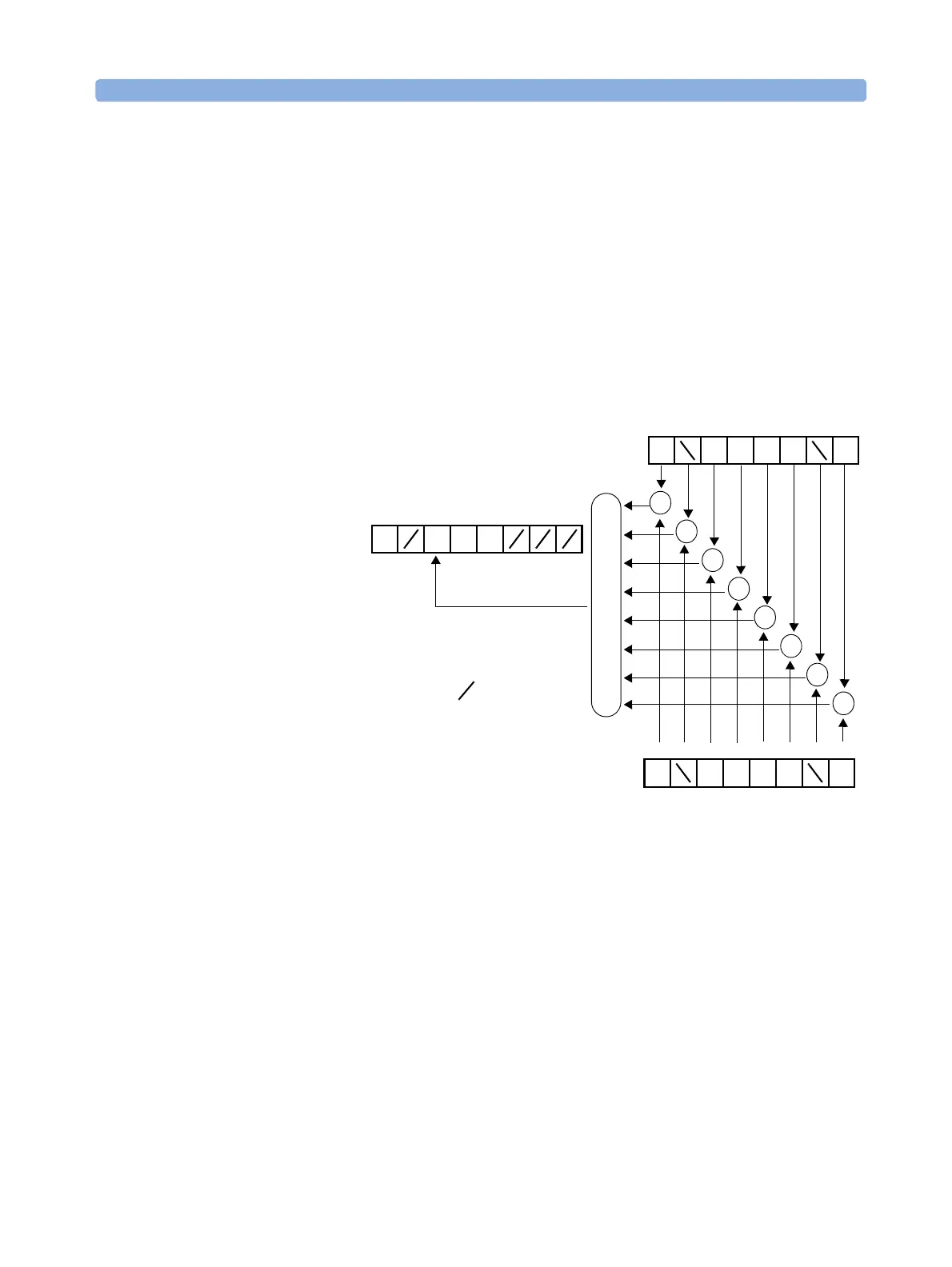

Figure 2 shows how the Standard Event Status Enable Mask (SESEM)

and the Standard Event Status Register (SESR) determine the Event Status

Bit (ESB) of the Status Byte.

Figure 2 The Event Status Bit

The SESR contains the information about events that are not slot specific.

For details of the function of each bit of the SESR, see “Standard Event

Status Register” on page 37.

The SESEM allows you to choose the event that may affect the ESB of the

Status Byte. If you set a bit of the SESEM to zero, the corresponding event

cannot affect the ESB. The default is for all the bits of the SESEM to be set

to 0.

The questionable and operation status systems set the Operational Status

Bit (OSB) and the Questionable Status Bit (QSB). These status systems

are described in “The Status Model” on page 33 and “Status Reporting –

The STATus Subsystem” on page 64.

01234567

*STB? returns the Status Byte Register

Status

OSB ESB QSB

*ESR? returns the Standard Event Status Register

001

01234567

Event

100000

Status

Register

01234567

Event

111111

Status

Enable

Mask

*ESE sets the Standard Event Status Enable Mask

&

&

&

&

&

&

&

&

OR

Byte

All bits shown as are unused

0

MAV

Loading...

Loading...