— 26 —

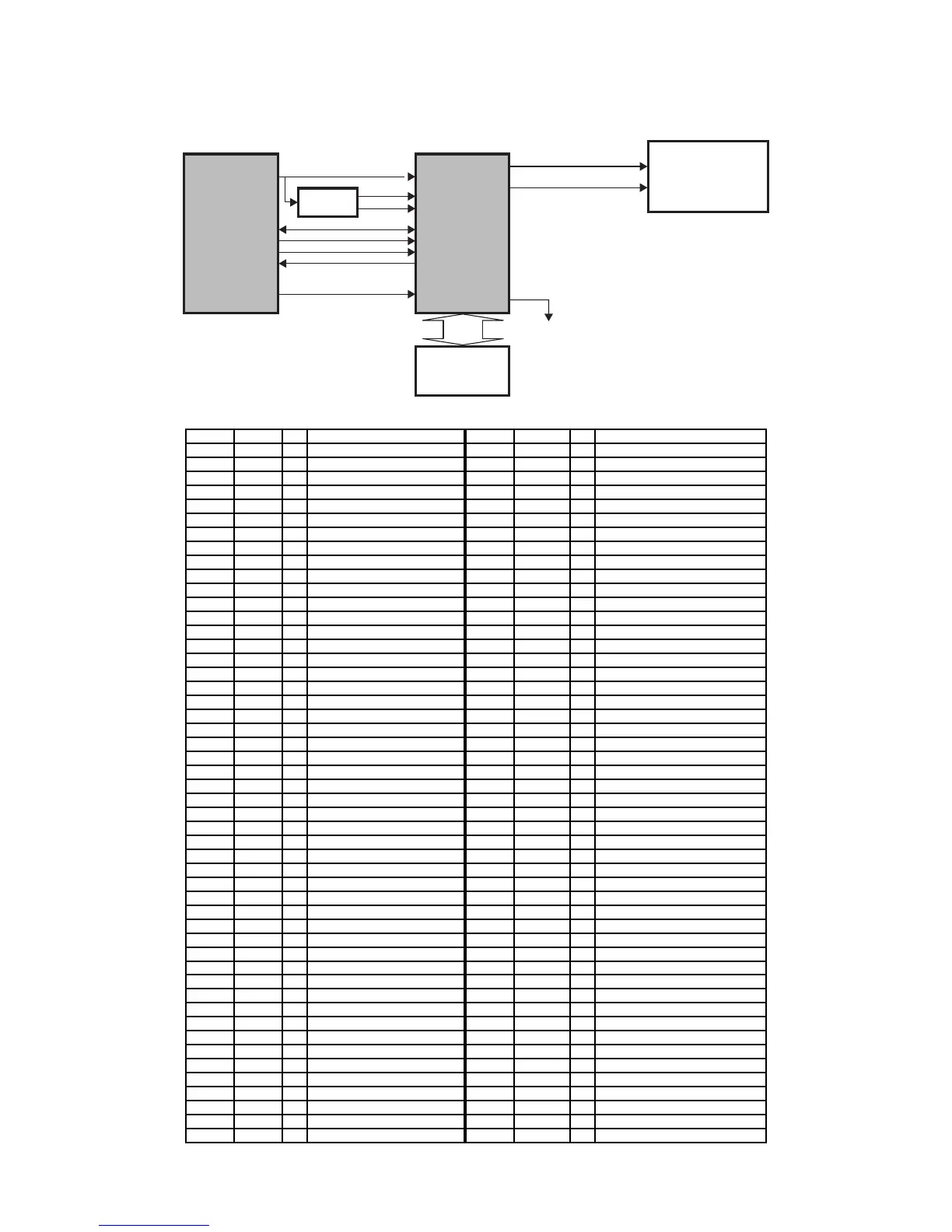

5-7. LCD CONTROLLER (IC4)

5-7-1. BLOCK DIAGRAM

5-7-2. Pin description

I/O

CONTROLLER

(IC11)

78 K IV

12.5 MHz

LCD

CONTROLLER

(IC4)

VRAM

BUS

Display memory

(IC1)

256 Kbit

A0-A15

DECODER

D0-D7

RD

WR

WAIT

MPUCLK (12.5 MHz)

IOCS

MEMCS

MCLK

6.00 Mhz

MCLK (LCD BUS CLOCK)

D0-D3

LCD

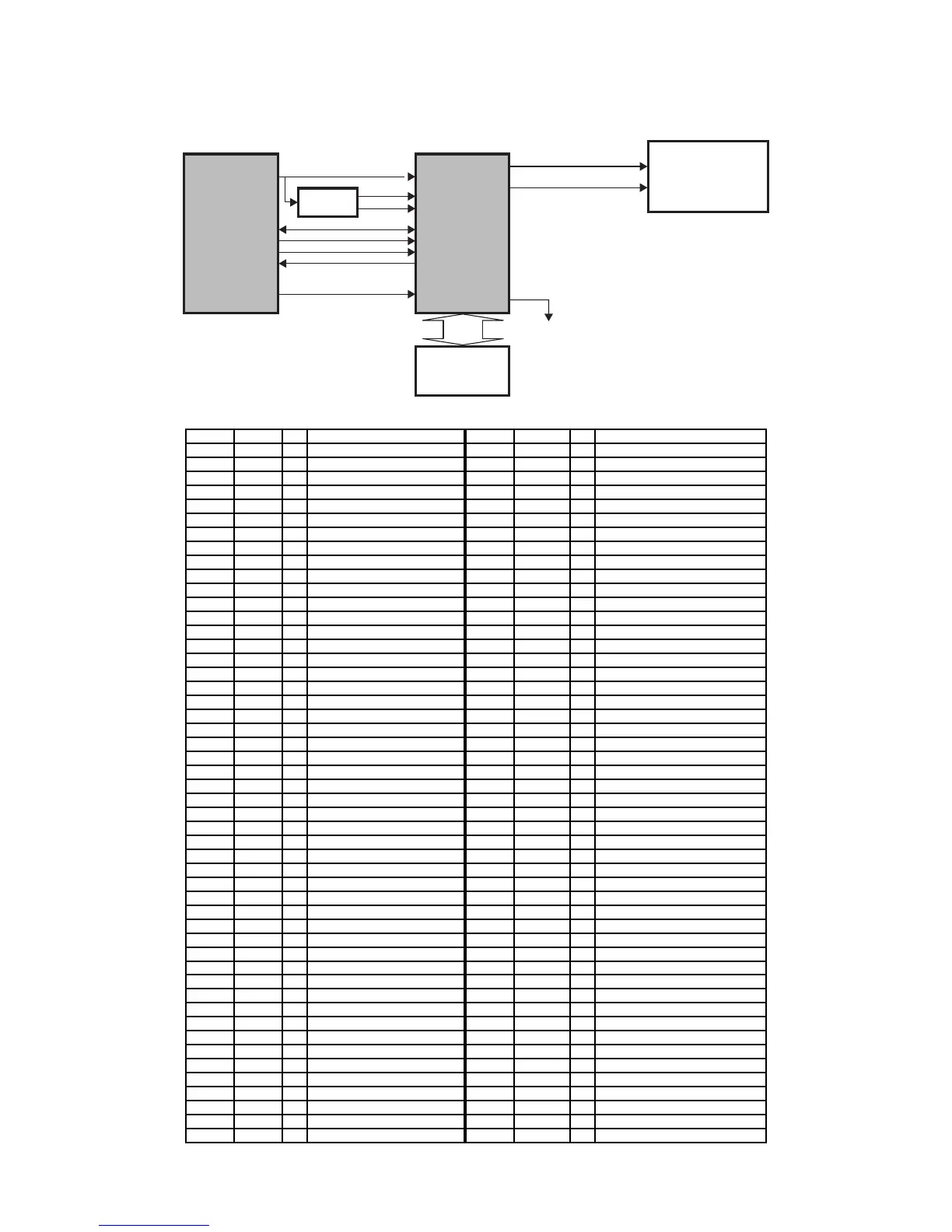

PIN NO NAME I/O DESCRIPTION PIN NO NAME I/O DESCRIPTION

1 DB7 I/O System data bus 51 VD7 I/O Display memory data bus

2 Vss GND 52 Vss GND

3 Vdd Vcc 53 Vdd Vcc

4 DB8 I/O Connected to Vdd 54 VD8 I/O Not used

5 DB9 I/O Connected to Vdd 55 VD9 I/O Not used

6 DB10 I/O Connected to Vdd 56 VD10 I/O Not used

7 DB11 I/O Connected to Vdd 57 VD11 I/O Not used

8 DB12 I/O Connected to Vdd 58 VD12 I/O Not used

9 DB13 I/O Connected to Vdd 59 VD13 I/O Not used

10 DB14 I/O Connected to Vdd 60 VD14 I/O Not used

11 DB15 I/O Connected to Vdd 61 VD15 I/O Not used

12 AB0 I System address bus 62 VA11 O Display memory address bus

13 AB1 I System address bus 63 VA12 O Display memory address bus

14 AB2 I System address bus 64 VA13 O Display memory address bus

15 AB3 I System address bus 65 O Display memory address bus

16 AB4 I System address bus 66 VA15 O Display memory address bus

17 AB5 I System address bus 67 VWE O Write signal for display memory

18 AB6 I System address bus 68 VCS0 O Select display memory

19 AB7 I System address bus 69 VCS1 O Not used

20 AB8 I System address bus 70 UD3 O Panel display data bus

21 AB9 I System address bus 71 UD2 O Panel display data bus

22 AB10 I System address bus 72 UD1 O Panel display data bus

23 AB11 I System address bus 73 UD0 O Panel display data bus

24 AB12 I System address bus 74 LD3 O Not used

25 AB13 I System address bus 75 LD2 O Not used

26 AB14 I System address bus 76 LD1 O Not used

27 AB15 I Connected to GND 77 LD0 O Not used

28 AB16 I Connected to GND 78 YD O Vertical scanning start pulse

29 AB17 I Connected to GND 79 LP O Display data latch clock

30 AB18 I Connected to GND 80 WF O Not used

31 AB19 I Connected to GND 81 XSCL O Display data shift clock

32 RESET I Reset signal 82 LCDENB O LCD enable signal output

33 VA0 O Display memory address bus 83 VOE O Read signal for display memory

34 VA1 O Display memory address bus 84 IOCS I Select internal registers

35 VA2 O Display memory address bus 85 IOW I Write signal for internal register

36 VA3 O Display memory address bus 86 IOR I Read signal for internal register

37 VA4 O Display memory address bus 87 MEMCS I Indicate a memory cycle

38 VA5 O Display memory address bus 88 MEMW I Indicate a memory write cycle

39 VA6 O Display memory address bus 89 MEMR I Indicate a memory read cycle

40 VA7 O Display memory address bus 90 READY O Ready signal

41 VA8 O Display memory address bus 91 BHE I Vcc

42 VA9 O Display memory address bus 92 OSC1 I Clock signal

43 VA10 O Display memory address bus 93 OSC2 O Clock signal

44 VD0 I/O Display memory data bus 94 DB0 I/O System data bus

45 VD1 I/O Display memory data bus 95 DB1 I/O System data bus

46 VD2 I/O Display memory data bus 96 DB2 I/O System data bus

47 VD3 I/O Display memory data bus 97 DB3 I/O System data bus

48 VD4 I/O Display memory data bus 98 DB4 I/O System data bus

49 VD5 I/O Display memory data bus 99 DB5 I/O System data bus

50 VD6 I/O Display memory data bus 100 DB6 I/O System data bus

Loading...

Loading...