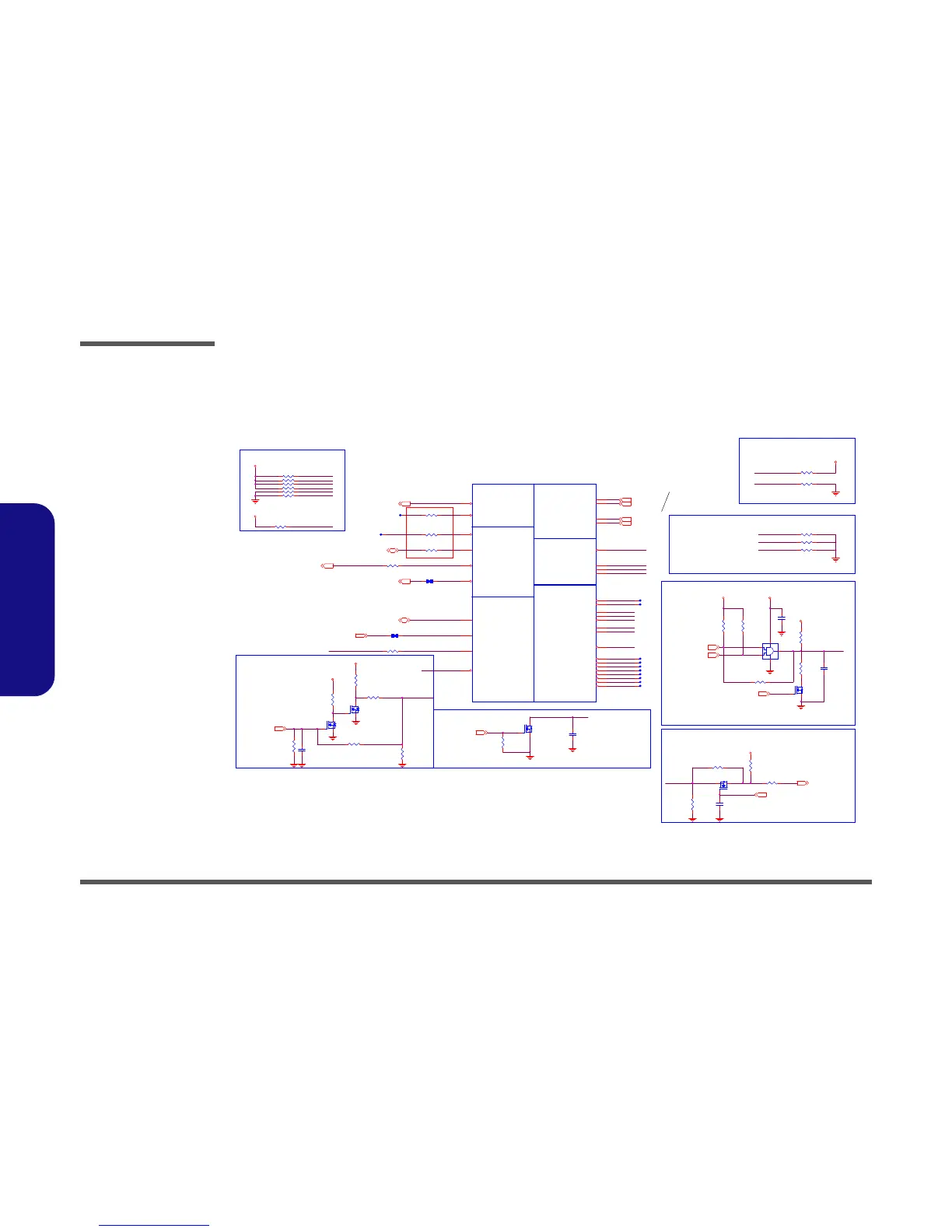

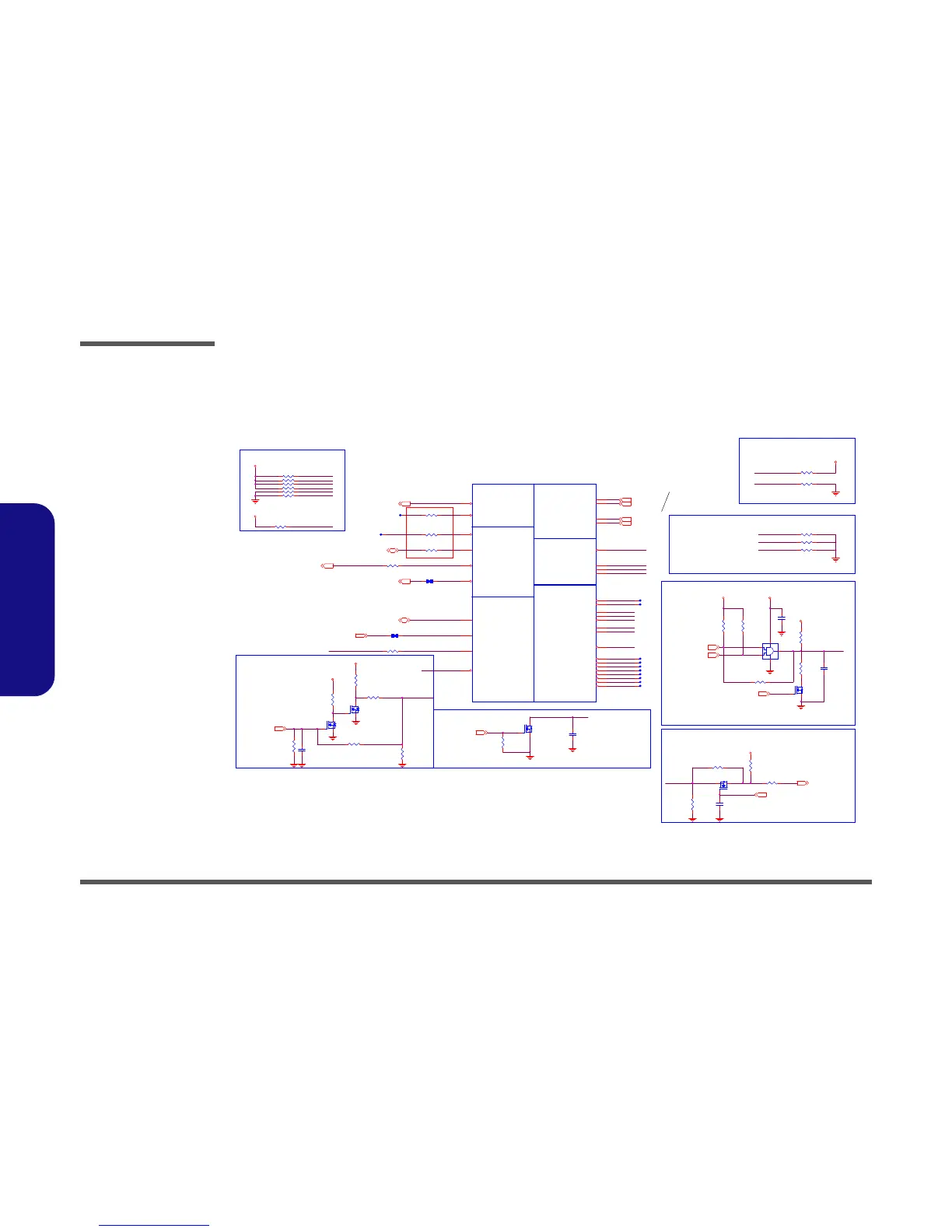

PMSYS_PWRGD_BUF

H_PROCHOT#

H_CPUPWRGD_R

CAD Note: C apacitor n eed to be placed

close to bu ffer outpu t pin

S3 circuit:- DRAM PWR GOOD logic

H_CPUPWRGD_R

R12510K_04

Processor Pullups/Pull downs

TRACE WIDTH 10MIL, LENGTH <500MILS

BUF_CPU_RST#

H_PROCHOT#

R209

*39_04

R282 * 0_04

C173

47p_50V_N PO_04

R213

75_04

R281

1K_04

R206

100K_04

R107 1K_04

R517 *10m il_short

R115 62_04

S

D

G

Q17B

MTDN7002ZH S6R

5

34

Q16

*MTN7002Z HS3

G

DS

R211

*750_1 %_04

R194

*200_04

S

D

G

Q17A

MTDN7002Z HS6R

2

61

R212 43. 2_1%_04

R205 *1. 5K_1%_04

R491 * 0_04

Q14

MTN7002ZHS 3

G

DS

R116 56_1%_04

R193

*100K_04

R106 * 0_04

R207

10K_04

R516 0 _04

C707

0.047u_10V_X7R_04

R199 130_1%_04

R200

200_1%_04

CLOCKS

MISCTHERMALPWR MANAGEMENT

DDR3

MISC

JTAG & BPM

U36B

Iv y Bridge _rPGA_2DPC_Rev 0p61

SM_RCOMP[1]

A5

SM_RCOMP[2]

A4

SM_DR AMRST#

R8

SM_RCOMP[0]

AK1

BCLK#

A27

BCLK

A28

DPLL_REF _CLK#

A15

DPLL_REF _CLK

A16

CATERR#

AL33

PEC I

AN33

PRO CHOT#

AL32

TH ERM TRI P#

AN32

SM_DR AMPWROK

V8

RESET#

AR33

PRD Y#

AP29

PRE Q#

AP27

TC K

AR26

TMS

AR27

TR ST#

AP30

TD I

AR28

TD O

AP26

DBR#

AL35

BPM#[0 ]

AT28

BPM#[1 ]

AR29

BPM#[2 ]

AR30

BPM#[3 ]

AT30

BPM#[4 ]

AP32

BPM#[5 ]

AR31

BPM#[6 ]

AT31

BPM#[7 ]

AR32

PM_SY NC

AM34

SKTOC C#

AN34

PRO C_SELEC T#

C26

UNCOREPWRGOOD

AP33

Q20

MTN7002ZH S3

G

DS

R276 1K_04

R208 0_04

C315

68p_50V_NPO_04

C300

*0. 1u_16V_Y5V_04

R496 *51_04

R275

4.99K_1%_04

U11

*MC74V HC1G08DF T1G

1

2

5

4

3

R148

100K_04

1.05VS_VTT

3.3VS

3.3V

1.5V

3.3V

1.5VS_CPU

3.3VS

1.05VS_VTT

1.05VS_VTT

CLK_EXP_N 19

CLK_EXP_P 19

CLK_DP_P 19

CLK_DP_N 19

H_PROCHOT#40,42

H_THRMTRIP#23

H_PECI23, 34

H_PM_SYNC20

PLT_RST#12,22, 28

H_CPUPWRGD23

DDR3_DRAMRST# 9,10

DRAMRST_CNTRL 6,19

H_SNB_IVB#23

H_PR OCHOT#_EC34

SUSB35,37,38

1.8VS_PW RGD20,37

PM_DR AM_PWRGD20

XD P _D B R _ R

SM_RC OMP_2

SM_RC OMP_1

SM_RC OMP_0H_PROCHOT# H_PROCHOT#_D

XD P _T MS

XD P _T R S T#

XD P _T C L K

VDDPWRGOOD_R

XDP_PR EQ#

XD P _T D I _ R

XD P _T D O _ R

CPUDRAMRST#

DDR3 Compensation Signals

If PROCHOT# is not used,

then it must be terminated

with a 56-£[ +-5% pull-up

resistor to 1.05VS_VTT .

BUF_CPU_RST#

SM_RCOMP_1

SM_RCOMP_0

XDP_BPM1_R

XDP_BPM0_R

SM_RCOMP_2

XDP_BPM5_R

XDP_BPM4_R

XDP_BPM3_R

XDP_BPM2_R

PMSYS_PWRGD_BUF

XD P _P R D Y #

XDP_BPM7_R

XDP_BPM6_R

Ivy Bridge Processor 2/7 ( CLK,MISC,JTAG )

Buffered reset to CPU

S3 circuit:- DRAM_RST# to memory

should be high during S3

CPUDRAMRST#

XD P _ TD O _ R

XDP_DBR_R

H_CATERR#

XD P _ TR S T#

XD P _ TM S

H_SNB_I VB#

PU/PD for JTAG signals

XDP_PR EQ#

XD P _ TD I _ R

XD P _ TC L K

C301

*0. 1u_10V_X5R_04

R183 140_1%_04

R521 200_1%_04

R520 25.5_1%_04

R493 *10mil_sho rt

R499 51_04

R503 51_04

R494 51_04

R495 51_04

R498 51_04

CAD NOTE: All DDR_COMP signals

should be routed such that :-

- max length = 500 mils

- trace width = 15mils and

- MB trace impedance < 68 mohms

(worst case resistance)

CAD Note: Use pad sharing method

for following clock resistor placement

Loading...

Loading...