H_PROCHOT#36

S

D

G

Q36B

L2N7002DW1T1G

5

3

4

R91 100K_04

C22

0.047u_10V_X7R_04

S3 circuit:- DRAM PWRGOOD logic

1.8VS_PWRGD15,33

PM_DRAM_PWRGD15

PMSYS_PWRGD_BUF

R73

*200_1%_04

1.5V_CPU

R57

10K_04

R58

*39_04

SUSB31,33,34

Q10

*MTN7002ZHS3

G

DS

3.3V

S

D

G

Q36A

L2N7002DW1T1G

2

6

1

R530 10K_04

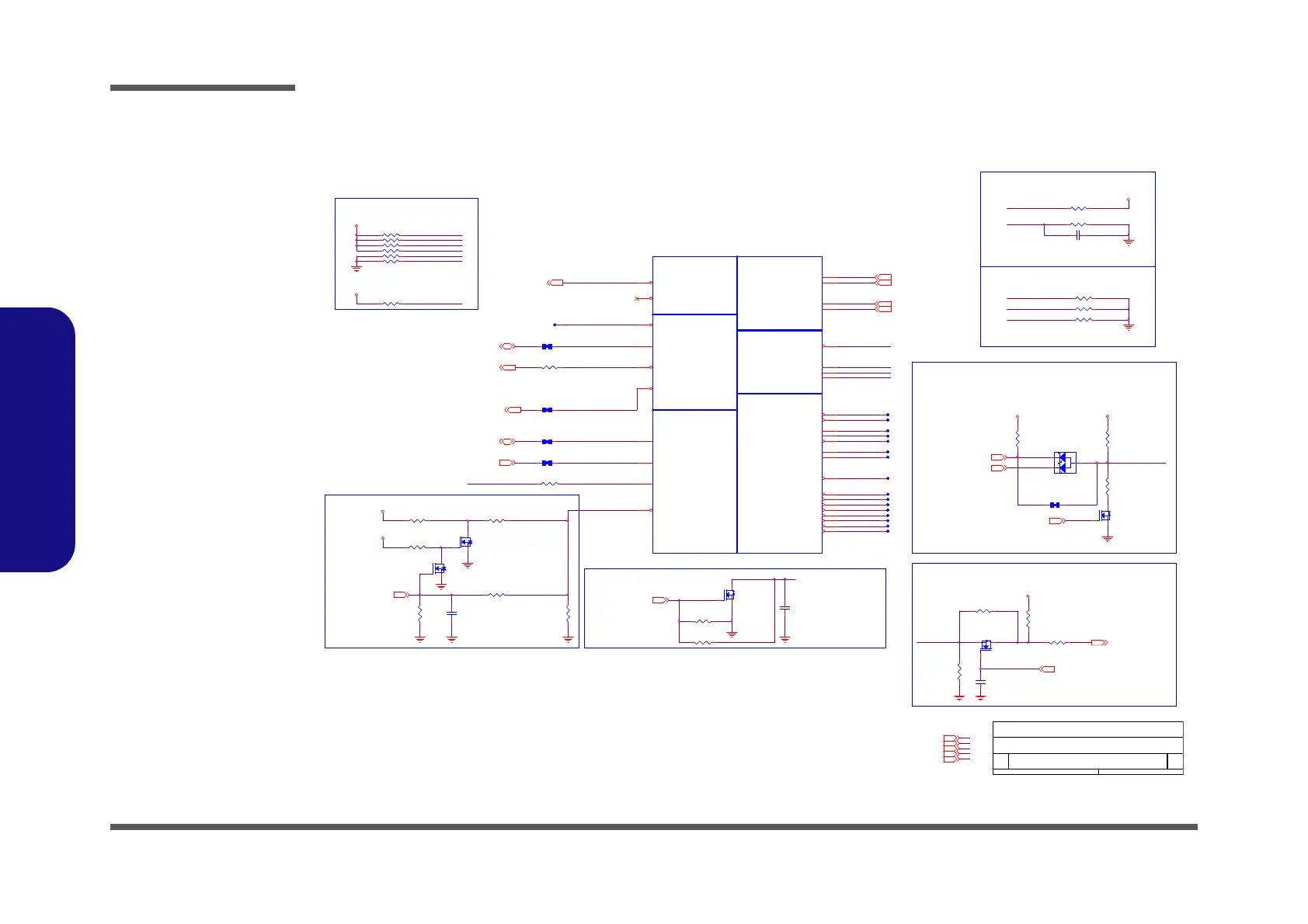

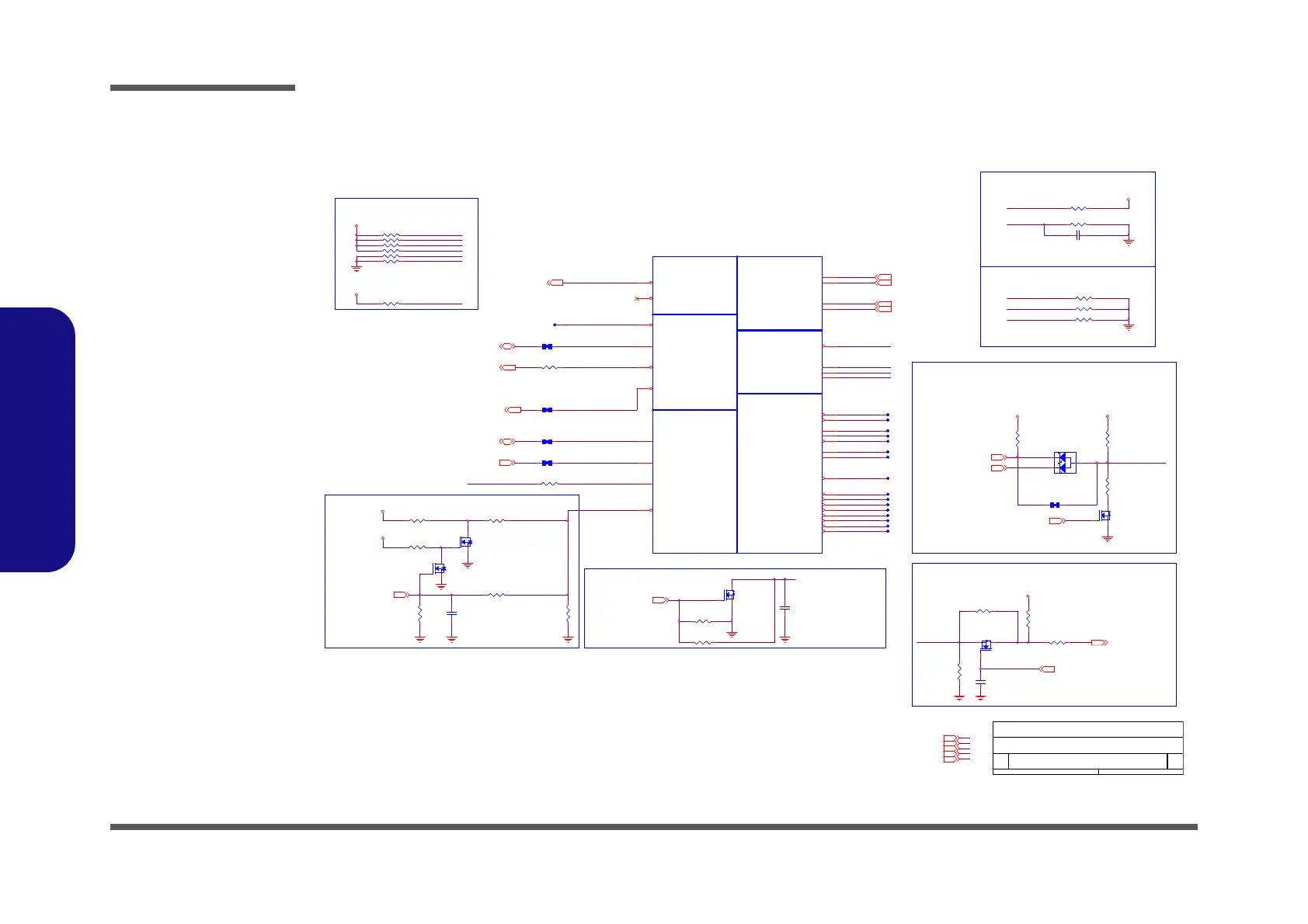

CLOCKS

MISCTHERMALPWR MANAGEMENT

DDR3

MISC

JTAG & BPM

U34B

PZ98827-364B-01F

SM_RCOMP[1]

A5

SM_RCOMP[2]

A4

SM_DRAMRST#

R8

SM_RCOMP[0]

AK1

BCLK#

A27

BCLK

A28

DPLL_REF_CLK#

A15

DPLL_REF_CLK

A16

CATERR#

AL33

PECI

AN33

PROCHOT#

AL32

TH ER MTR IP #

AN32

SM_DRAMPWROK

V8

RESET#

AR33

PRDY#

AP29

PREQ#

AP27

TCK

AR26

TMS

AR27

TR ST#

AP30

TDI

AR28

TDO

AP26

DBR#

AL35

BPM#[0]

AT28

BPM#[1]

AR29

BPM#[2]

AR30

BPM#[3]

AT30

BPM#[4]

AP32

BPM#[5]

AR31

BPM#[6]

AT31

BPM#[7]

AR32

PM_SYNC

AM34

SKTOCC#

AN34

PROC_SELECT#

C26

UNCOREPWRGOOD

AP33

R59 *10mil_04

C515

47p_50V_NPO_04

H_PROCHOT#

R90 *0_04

R60 130_1%_04

CAD Note: Capacitor

need to be placed

close to buffer output pin

H_PROCHOT_EC27

Q14

MTN7002ZHS3

G

DS

C

A

A

D20

*BAT54AS3

1

2

3

PMSYS_PWRGD_BUF

R414 51_04

R416 51_04

R108 51_04

R415 51_04

R109 *51_04

R95 51_04

3.3VS

VTT_C PU

XD P _ D B R _ R

R407 1K_04

XD P _ TMS

XD P _ TD O _ R

PU/PD for JTAG signals

XDP_TRST#

XDP_PREQ#

XD P _ TD I _ R

XD P _ TC L K

H_CPUPWRGD_R

R106

*750_1%_04

R112 *1.5K_1%_04

Processor Pullups/Pull downs

TRACE WIDTH 10MIL, LENGTH <500MILS

3.3VS

BUF_CPU_RST#

DDR3 Compensation Signals

SM_RCOMP_2

SM_RCOMP_1

SM_RCOMP_0

C96

*68p_50V_NPO_04

VDDPWRGOOD_R

XD P _ TR S T #

XD P _ TC L K

PLT_RST#17,23

XD P _ TMS

XD P _ TD I _ R

CPUDRAMRST#

H_PROCHOT#_D

H_CATERR#

Buffered reset to CPU

XD P _ TD O _ R

XDP_PREQ#

H _THR MTR IP #18

H_SNB_IVB#18

R382 25.5_1%_04

R381 200_1%_04

R419 *10mil_04

R412 10K_04

R413 140_1%_04

H_PECI18,27

PM_SYNC_R

If PROCHOT# is not used, then it must

be terminated with a 68-£[ +-5%

pull-up resistor to 1.05VS_VTT .

Ivy/Sandy Bridge Processor 2/7

( CLK,MISC,JTAG )

R418 *10mil_04

R410 62_04

VTT_CPU

H_PROCHOT#

SM_RCOMP_2

SM_RCOMP_0

SM_RCOMP_1

CLK_DP_N 14

CLK_EXP_N 14

CLK_EXP_P 14

H_PM_SYNC15

CLK_DP_P 14

H_SNB_IVB#

1.5V6,9,10,20,28,31,33

1.5V_CPU6,31

VTT_CPU2,5,18,19,20,34,35,36

3.3V2,6,11,13,14,15,17,18,19,20,22,23,26,27,28,31,33,34,35

H_CPUPWRGD18

Q8

MTN7002ZHS3

G

DS

R46

4.99K_1%_04

CPUDRAMRST#

R47 *0_04

1.5V

R45

1K_04

S3 circuit:- DRAM_RST# to memory

should be high during S3

DRAMRST_CNTRL 9,10,14

DDR3_DRAMRST# 9,10

R48 1K_04

10/1

XD P _ D B R _ R

R411 *10mil_04

XDP_BPM1_R

XDP_BPM0_R

XDP_BPM6_R

XDP_BPM5_R

XDP_BPM4_R

XDP_BPM3_R

XDP_BPM2_R

XDP_BPM7_R

H_PECI_R

R105 75_1%_04

R405 56_1%_04

Tit le

Size Document Number Rev

Date: Sheet

of

3.0

[03]PROCESSOR 2/7

A3

343Friday , Nov ember 18, 2011

ÂÅ ¤Ñ ¹q ¸£ CLEVO CO.

H_CPUPWRGD_R

R104 43_1%_04

R531

100K_04

C585 *0.1u_10V_X7R_04

XDP_PRDY #

VTT_C PU

3.3VS9,10,11,12,13,14,15,16,17,18,19,20,23,24,25,27,28,29,30,31,36

R417 *10mil_04

H _TH RMTR IP#_R

Loading...

Loading...