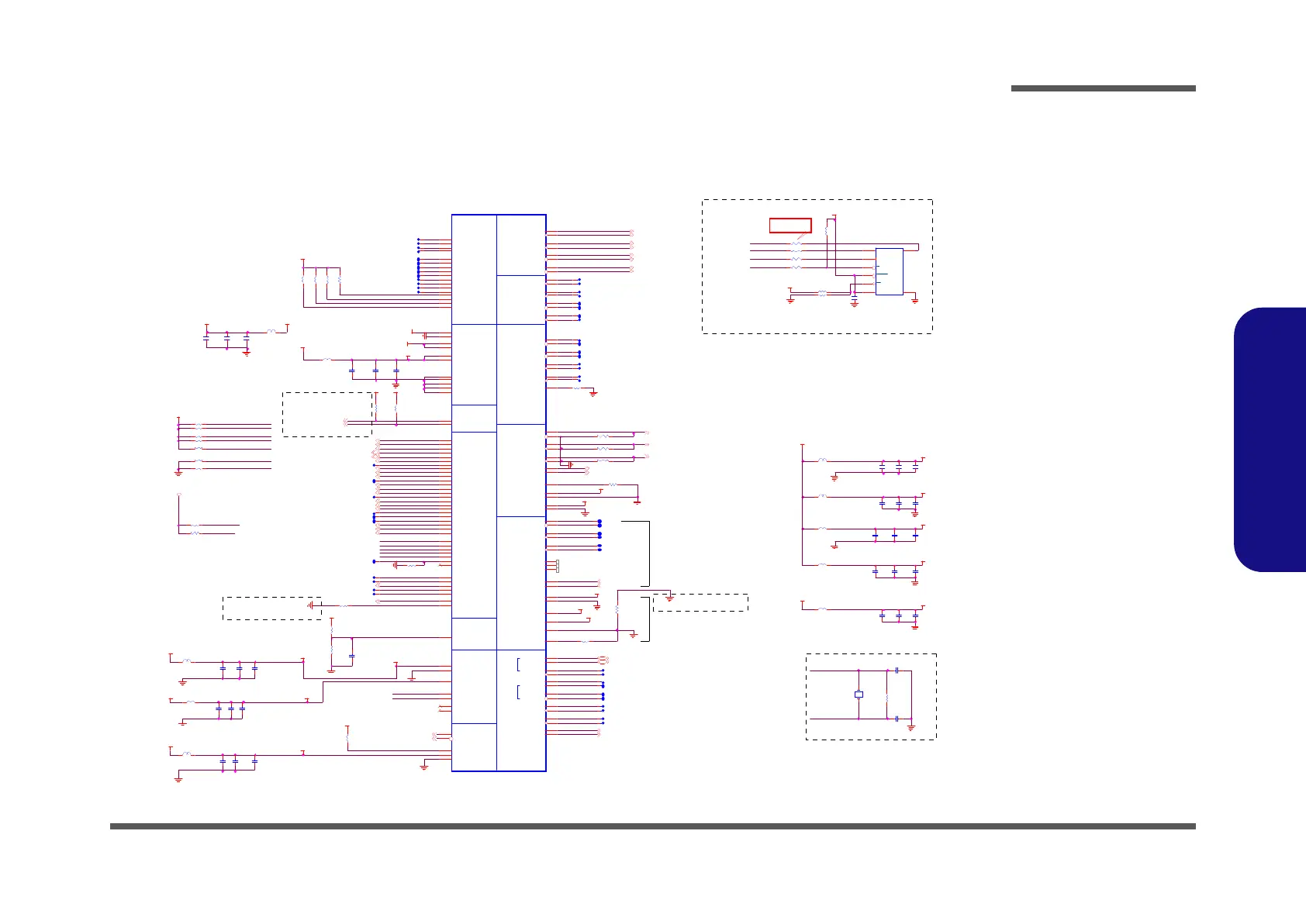

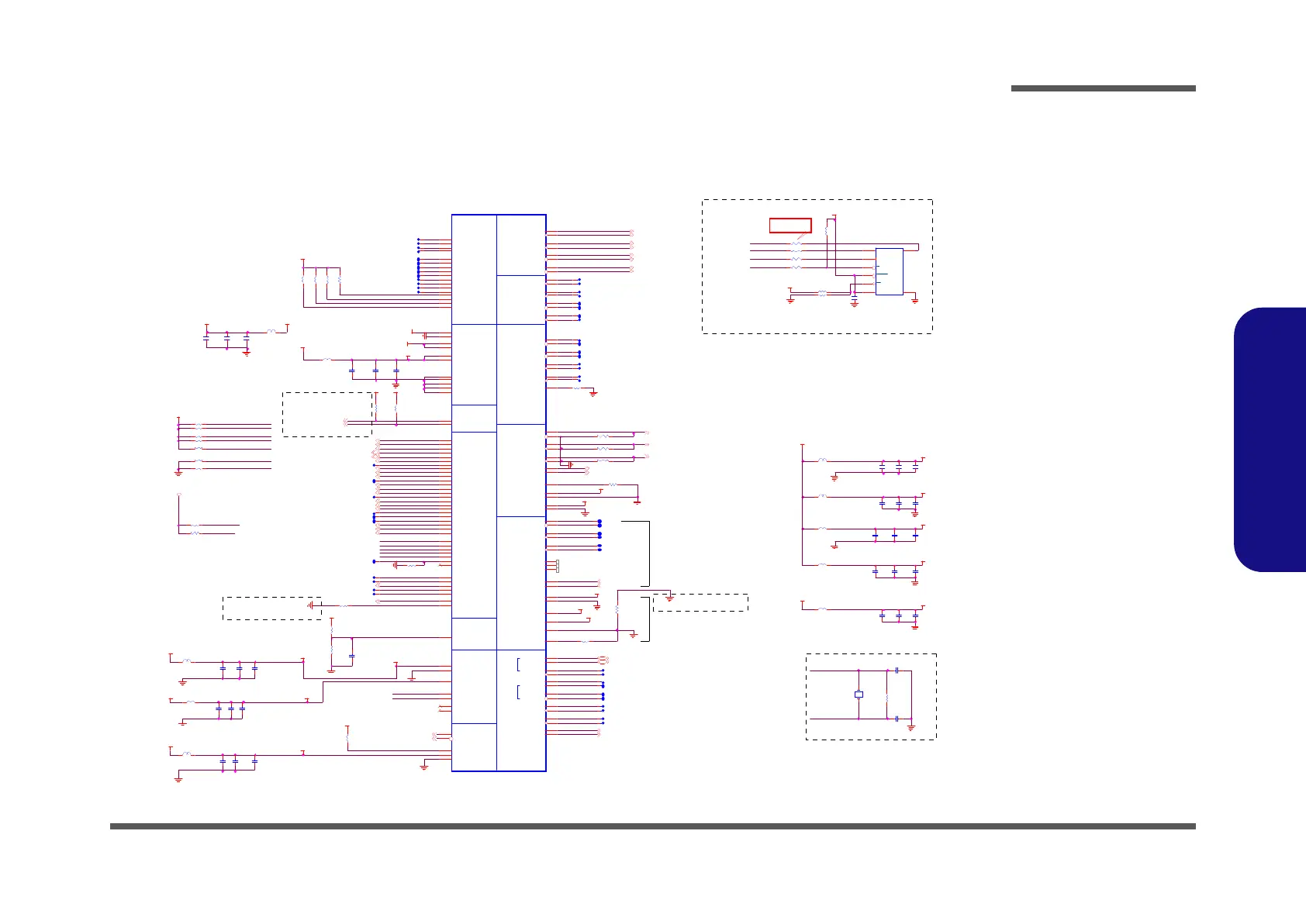

VBIOS FLASH ROM

R_DAC1

GPIO8

GPIO2 8_ TDO

GPIO2 4_ TRST B

TM D S _ T X1 P 21

TM D S _ T X2 N 21

TM D S _ T X2 P 21

TM D S _ T X1 N 21

GPU_T ALERT#10 , 17

TM D S _ T X0 P 21

TM D S _ T XC N 21

TM D S _ T XC P 21

TM D S _ T X0 N 21

*5.11K_1% _06

R 115

SB_MXM_CLKREQ#

*1 0K _ 04R68 5

ROBSON_GPIO16

NOTE: Designs t hat do not include an EEP RO M m ust still pr ovide

a ccess to the ROM interface signals for debug purposes

GEN_ B

1M bit SERIAL EEPRO M is r equired for Par k/Robson GDDR5 Design

(1.0V@110m A DPC_VDD10)

For PX_E N, refer to t he BACO

reference schem atics for detail

(1 .8V @2 0m A T SVDD)

(1 .0 V@1 25m A DPLL_ VDDC)

(1.8 V@75mA DPLL_PVDD)

GND Op tion If

XO_IN/XO_IN2

not used

TS_FDO

XTALIN

PLA CE VREFG DIVIDER A ND CAP

C LOSE TO ASIC

XTALOUT

COMPONENTS SHOWN ARE EXAMPLES ONLY

AND NOT NECESSAR ILY QUALIFIED

HPD121

SC L

SDA

Access to SCL and SDA is

mandatory on BACO designs

for debug purposes

DNI

ROM_SO

HPD_ 4

GPIO10 SCK/WEb

GPIO22

GPIO9

CSb

SI/A1 6

T E ST EN

0. 1"~ 0.5 "

(1 .8 V@1 50m A DPC_ VDD1 8 )

PX_EN

(3.3V @130mA A2VDD)

For Seymour,

DPC_PVDD is DPC_VDD18

DPC_PVSS and all DPC_VSSR are DP_VSSR

(1 .8V @2 m A A2 VD DQ)

1M bit SERIAL EEPRO M is optional for Seymour GDDR5 Design

(1.8V @65m A AVD D)

(1.8V @100m A VDD1DI)

(1.8V @100mA V DD2 DI)

MEM_ID1

MEM_ID0

MEM_ID2

MEM_ID3

ME M_ I D 0

ME M_ I D 1

ME M_ I D 2

ME M_ I D 3

B_DAC2

G_DAC2

R_DAC2

NC on Seymour

DDC1DATA 2 1

DDC1CLK 2 1

DDCDATA_AUX3N

AUX2N

AUX2P

DDC1DATA

DDCDATA_AUX5N

DDCCLK_ AUX3P

DDC1CLK

AUX1N

AUX1P

DDC6CLK

DDC2DATA

DDC2CLK

G P I O 24 _T R ST B

DDC6DATA 21

DDC6CLK 21

DDCCLK_ AUX5P

DDC6DATA

G P I O 25 _T D I

RB_DAC2

GB_DA C2

BB_DAC2

GPIO7_ B LON

G P I O 26 _T C K

G P I O 27 _T M S

SB_MXM_CLKREQ#

GPIO21

GPIO22

GPIO20

G P I O _1 9_ C TF

Se y m o u r

DAC2 i s NC on Se ymour

G P I O 26 _T C K

G P I O 24 _T R S TB

G P I O 25 _T D I

HPD1

G P I O 28 _T D O

G P I O 27 _T M S

GPIO6

GPIO0

GPIO7_ B LON

GPIO13

GPIO12

GPIO1

GPIO11

GPIO10

MXM_SDA TA

GPIO9

GPIO8

GPIO2

HPD2

ROBSON_GPIO15

GPU_TALERT#

G P I O 18 _H P D 3

GPIO5

MXM_SCL K

ROBSON_GPIO1536

GEN_ A

R716 *150_1%_04

G_DAC1

* 5. 1 1K _1 % _ 06R116

512Kbit

XTALOUT

XTALIN

SB_MXM_CLKREQ#16

SB _MX M_C L KR EQ#

*2.2 K_ 04

R16 7

3. 3 VS_GPU

XTAL Option

*1u_6.3 V _X5 R _0 4

C 179

*1 0K _ 04R10 8

* 0 . 1u _10 V _X5 R _0 4

C203

*1 0K _ 04R11 0

*10u_6.3V_X5R_06

C197

*10u_6.3V_X5R_06

C19 3

*1K _0 4R11 3

*EN25P05-50GCP

U5

S

1

VCC

8

Q

2

HOLD

7

VSS

4

D

5

C

6

W

3

L64

* H C B 16 08 KF - 12 1T 25

* 2 2p_ 50 V _N P O _0 4C200

*1u_6.3 V _X 5R _0 4

C175

*10u_6.3V_X5R_06

C20 1

*1u_6.3 V _X5 R _0 4

C 188

R715 *150_1%_04

L67

* HCB160 8KF-121T2 5

*0_ 04R1 02

* 0 _04

R117

* 1 0u _6 .3 V _X 5R _0 6

C 186

* 10 u_6 . 3V _X 5R _ 06

C17 4

* 1 0u_ 6. 3 V_ X5 R _0 6

C180

*1 0K _ 04

R98

*0.1u_10V_X5R_04

C 182

* 1 50_ 1% _0 4R103

* 4 99 _1% _0 4

R112

* 2 2p_ 50 V _N P O _0 4C196

R717 *150_1%_04

BB_DAC1

B_DAC1

R94 * 33_ 04

* 0. 1 u_1 0V _ X5R _ 04

C176

G_DAC1 21

L70

* HCB160 8KF-121T2 5

*1 0K _ 04R10 9

B_ DAC1 21

R_DAC1 21

* 1 u_ 6. 3V _ X5 R _04

C198

HSYNC_ DAC 1 10, 2 1

VSYNC_DAC1 10,21

*1 0K _ 04R10 6

*1u_6.3 V _X5 R _0 4

C 185

RB_DAC1

GB_DA C1

R92 * 33_ 04

* 4 99 _1 % _0 4

R118

*0.1u_10V_X5R_04

C184

X2

* F SX 8L _2 7M H z

12

* 2 49 _1 % _0 4

R120

*71 5_ 1%_ 04R1 19

* 1 0K _0 4

R99

*4 .7K_0 4

R104

L68

* HCB160 8KF-121T2 5

* 1 u_ 6. 3V _ X5R _ 04

C19 0

*1 0K _ 04R10 7

*0.1u_10V_X5R_04

C17 8

L71

*HCB1 60 8KF-121 T25

* 1 u_ 6. 3V _ X5R _ 04

C18 1

*1K _0 4R11 4

*1 0K _ 04R11 1

* 1 0u _6 .3 V _X 5R _0 6

C 183

*0 .1u_10V_X5R_04

C170

L6 5

*HCB1608 KF-12 1T25

L73

*HCB1 60 8KF-121 T25

* 1u _6 . 3V _X 5R _ 04

C 194

*0.1u_10V_X5R_04

C187

*0.1u_10 V_X5R_04

C171

* 1u _6 . 3V _X 5R _ 04

C17 2

GPIO7_ BLON20

DP A

DP B

DVO

I2 C

G ENE RA L PU RPO SE I /O

DA C1

DA C2

DD C/ AU X

THE RM AL

PL L/ CLO CK

DP C

* R O B S O N XT S3

U4B

DMINUS

T2

DPL L_ PVDD

AF1 4

DPL L_PVSS

AE14

DPL L_ VD DC

AD14

DPL US

T4

DPC_ VSSR# 1

U1

DVDATA_ 7

AC7

T X2 M _D P C 0N

Y2

TX C C M _D P C 3N

U5

DPC_ VSSR# 5

AA1

TX 1P _D P C 1 P

Y4

DVDATA_ 0

Y7

T X0 M _D P C 2N

V2

DPC_ VDD18 #1

AC6

DPC_ PVDD

W6

DVDATA_ 9

AD7

TX 2P _D P C 0 P

AA3

DVDATA_ 8

AC8

DPC_ VDD10 #1

AA5

DVDATA_ 12

AE8

DPC_ VDD10 #2

AA6

DVCNTL_ 0

AE9

DVDATA_ 3

AB4

DVDATA_ 1

Y8

DVDATA_ 11

AD9

DVDATA_ 2

AB2

DVDATA_ 10

AC10

DPC_ VDD18 #2

AC5

TXCCP_DPC3P

V4

DVDATA_ 4

AB7

DPC_ VSSR# 2

W1

DVDATA_ 5

AB8

TX 0P _D P C 2 P

W3

DVDATA_ 6

AB9

T X1 M _D P C 1N

W5

GENERICA

AB13

GENERICB

W8

GENERICC

W9

GENERICD

W7

GENERICE_HPD4

AD10

GPIO_ 0

U6

GPIO_ 1

U10

GPIO_10 _ROMSCK

P2

GPIO_ 11

N6

GPIO_ 12

N5

GPIO_ 13

N3

GPIO_14 _HPD2

Y9

GPIO_ 15 _PWRCN TL_ 0

N1

GPIO_16_SSIN

M4

GPIO_17_THERMAL_INT

R6

GPIO_18 _HPD3

W1 0

GPIO_ 19 _CT F

M2

GPIO_ 2

T1 0

GPIO_ 20 _PWRCN TL_ 1

P8

GPIO_21_BB_EN

P7

GPIO_ 22 _ROMCSB

N8

GPIO_ 23 _CL KREQB

N7

GPIO_ 3_ SMBDATA

U8

GPIO_ 4_ SMBCL K

U7

GPIO_ 5_ AC_ BATT

T9

GPIO_ 6

T8

GPIO_7_BLON

T7

GPIO_ 8_ ROMSO

P1 0

GPIO_ 9_ ROMSI

P4

H2SYNC

AL13

HPD1

AC14

HSYNC

AH26

JT AG _ TC K

L3

JT AG _ TD I

L5

JT AG _ TD O

K4

JT AG _ TMS

L1

JT AG _ TR S TB

L6

DDCDATA_AUX3N

AC20

DDCCLK_AUX3P

AD20

TS _F D O

R5

TSVDD

AD17

TSVSS

AC17

VR E F G

AC16

VSS1 DI

AD23

VSS2 DI

AC19

XT AL I N

AM28

XT AL O U T

AK28

A2VDD

AE20

A2 VDDQ

AE17

A2VSSQ

AE19

AUX1N

AD4

AUX1P

AD2

AUX2N

AD11

AUX2P

AD13

AVDD

AG24

AVSSQ

AE22

B

AH24

B2

AK10

B2B

AL9

BB

AG25

C

AH12

COMP

AJ9

DDC1CLK

AE6

DDC1DATA

AE5

DDC2CLK

AC11

DDC2DATA

AC13

DDC6CLK

AC1

DDC6DATA

AC3

DDCDATA_AUX5N

AD16

DDCCLK_AUX5P

AE16

G

AL25

G2

AL11

G2 B

AJ11

GB

AJ25

R

AM26

R2

AM12

R2B

AK12

R2SET

AG13

RB

AK26

RSET

AD22

SC L

R1

SD A

R3

TX0 M_DPA2N

AG5

TX0P_DPA2P

AG3

TX1 M_DPA1N

AH1

TX1P_DPA1P

AH3

TX2 M_DPA0N

AK1

TX2P_DPA0P

AK3

TX3 M_DPB2N

AM5

TX3P_DPB2P

AK6

TX4 M_DPB1N

AH6

TX4P_DPB1P

AJ7

TX5 M_DPB0N

AL7

TX5P_DPB0P

AK8

TXCAM_DPA3N

AF4

TX C A P_ D PA 3 P

AF2

TXCBM_DPB3N

AM3

TX C B P_ D PB 3 P

AK5

V2SYNC

AJ13

VDD1 DI

AE23

VDD2 DI

AD19

VSYNC

AJ27

Y

AM10

XO _ IN2

AB22

XO _ IN

AC22

TESTEN_LEGACY

AF2 4

DVCNTL_ 2

N9

DPC_ VSSR# 3

U3

DPC_ PVSS

V6

DPC_ VSSR# 4

Y6

DVCNTL_ 1

L9

DVCL K

Y11

DPC_CALR

J8

PX _ E N

AB16

TESTEN

K7

* 1 0u _6 . 3V _X 5R _ 06

C173

R95 * 33_ 04

L69

* HCB160 8KF-121T2 5

R93 * 33_ 04

* 1 0u _6 .3 V _X 5R _0 6

C189

* 0 . 1u _10 V _X5 R _0 4

C195

*4.7 K_ 04

R105

*10K_04

R97

*0_ 04R1 00

* 0. 1 u_1 0V _ X5R _ 04

C19 2

L7 2

*HCB1 60 8KF-121 T25

*1 M_0 4

R1 21

L66

* HCB160 8KF-121T2 5

* 0.1u_10V_X5R_04

C199

* 1 0u _6. 3 V _X5 R _0 6

C177

* 1 0K _0 4

R96

*1 0K _0 4

R10 1

*0.1u_10V_X5R_04

C 191

* 1 u_6 . 3V _X 5R _ 04

C20 2

DPC_ VDD18

1 . 0V _R E G

DPC_ VDD10

1. 0 V_REG

1. 8 V_REG

DPLL_PVDD

1. 8 V_REG

DPLL _PVDD

1 . 8V _R E G

TSVDD

D P LL _V D D C

3. 3V S _G P U

3.3VS_GPU3. 3V S _G P U

3. 3 VS _ G PU

A2VDD

3. 3 VS _G PU

1.8V_REG

DPC_ VD D18

VDD2DI

A2VDDQ

VDD1 DI

AVDD

1.8V_REG

DPC_ VDD18

1. 8 V_ R E G

VDD1DI

AV D D

3.3VS_GPU

VD D 2 D I

A2VDDQ

A2VDD

GPU_DPLUS10

3. 3 VS _ G PU

SCL20

GPU_DMINUS10

SDA20

GPIO2 110

VSYNC_DAC2 10

HSYNC_DAC2 10

GPIO010

GPIO510

GPIO2 210

GPIO910

GPIO210

GPIO110

GPIO1310

GPIO1210

GPIO1110

MXM_SDATA10

GENERICC10

GPIO810

ROBSON_GPIO1636

MXM_ SCLK10

Loading...

Loading...