RPD1

*4.99K_1%_04

T9 7

CSHUNT1

* 040 2_12 0pF _50 V_ 5%

RSER2

* 49. 9_1 %_ 04

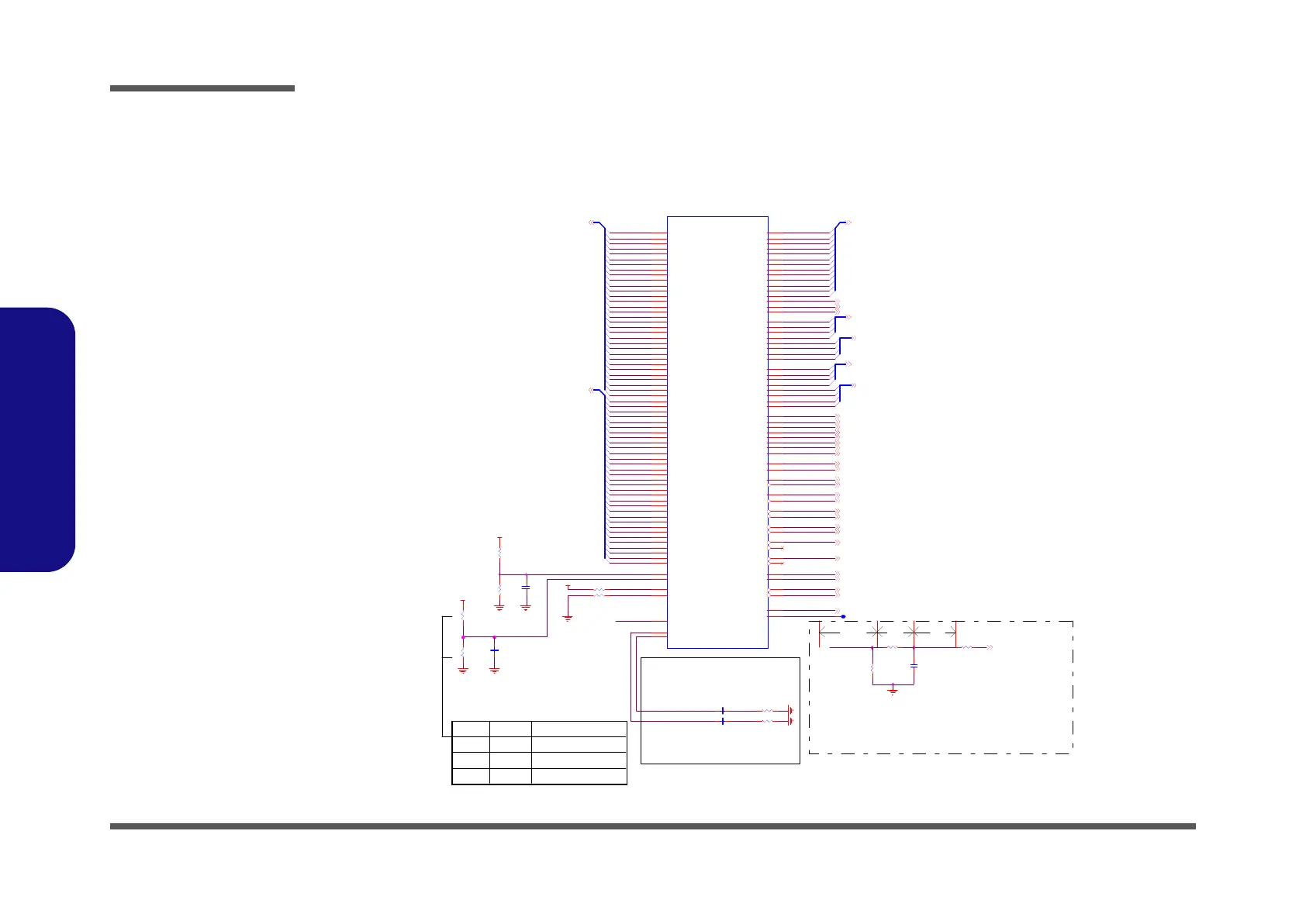

MEMORY INTERFACE

GDDR5/DDR3

G DDR5 /DD R3

G DDR 5/DD R3

*ROBSON XT S3

U4C

DQ A0 _0 /D Q A_ 0

K2 7

DQ A0 _1 /D Q A_ 1

J2 9

DQ A0 _10/ D QA_10

A2 8

DQ A0 _11/ D QA_11

C2 8

DQ A0 _12/ D QA_12

E2 7

DQ A0 _13/ D QA_13

G2 6

DQ A0 _14/ D QA_14

D2 6

DQ A0 _15/ D QA_15

F2 5

DQ A0 _16/ D QA_16

A2 5

DQ A0 _17/ D QA_17

C2 5

DQ A0 _18/ D QA_18

E2 5

DQ A0 _19/ D QA_19

D2 4

DQ A0 _2 /D Q A_ 2

H3 0

DQ A0 _20/ D QA_20

E2 3

DQ A0 _21/ D QA_21

F2 3

DQ A0 _22/ D QA_22

D2 2

DQ A0 _23/ D QA_23

F2 1

DQ A0 _24/ D QA_24

E2 1

DQ A0 _25/ D QA_25

D2 0

DQ A0 _26/ D QA_26

F1 9

DQ A0 _27/ D QA_27

A1 9

DQ A0 _28/ D QA_28

D1 8

DQ A0 _29/ D QA_29

F1 7

DQ A0 _3 /D Q A_ 3

H3 2

DQ A0 _30/ D QA_30

A1 7

DQ A0 _31/ D QA_31

C1 7

DQ A1 _0 /D Q A_ 32

E1 7

DQ A1 _1 /D Q A_ 33

D1 6

DQ A1 _2 /D Q A_ 34

F1 5

DQ A1 _3 /D Q A_ 35

A1 5

DQ A1 _4 /D Q A_ 36

D1 4

DQ A1 _5 /D Q A_ 37

F1 3

DQ A1 _6 /D Q A_ 38

A1 3

DQ A1 _7 /D Q A_ 39

C1 3

DQ A0 _4 /D Q A_ 4

G2 9

DQ A1 _8 /D Q A_ 40

E1 1

DQ A1 _9 /D Q A_ 41

A1 1

DQ A1 _10/ D QA_42

C1 1

DQ A1 _11/ D QA_43

F1 1

DQ A1 _12/ D QA_44

A9

DQ A1 _13/ D QA_45

C9

DQ A1 _14/ D QA_46

F9

DQ A1 _15/ D QA_47

D8

DQ A1 _16/ D QA_48

E7

DQ A1 _17/ D QA_49

A7

DQ A0 _5 /D Q A_ 5

F2 8

DQ A1 _18/ D QA_50

C7

DQ A1 _19/ D QA_51

F7

DQ A1 _20/ D QA_52

A5

DQ A1 _21/ D QA_53

E5

DQ A1 _22/ D QA_54

C3

DQ A1 _23/ D QA_55

E1

DQ A1 _24/ D QA_56

G7

DQ A1 _25/ D QA_57

G6

DQ A1 _26/ D QA_58

G1

DQ A1 _27/ D QA_59

G3

DQ A0 _6 /D Q A_ 6

F3 2

DQ A1 _28/ D QA_60

J6

DQ A1 _29/ D QA_61

J1

DQ A1 _30/ D QA_62

J3

DQ A1 _31/ D QA_63

J5

DQ A0 _7 /D Q A_ 7

F3 0

DQ A0 _8 /D Q A_ 8

C3 0

DQ A0 _9 /D Q A_ 9

F2 7

MV R E F D A

K2 6

MV R E F SA

J2 6

ME M_ C AL R N 0

J2 5

ME M_ C AL R P 0

K2 5

C ASA0B

G1 9

C ASA1B

G1 6

CKEA0

K20

CKEA1

J1 7

CLKA0

H2 6

CLKA0B

H2 5

CLKA1

G9

CLKA1B

H9

CS A0 B_ 0

H2 2

CS A0 B_ 1

J2 2

CS A1 B_ 0

G1 3

CS A1 B_ 1

K13

WCKA0_0/DQMA_0

E32

W C KA 0 B _0 / D QM A_ 1

E30

WCKA0_1/DQMA_2

A21

W C KA 0 B _1 / D QM A_ 3

C2 1

WCKA1_0/DQMA_4

E13

W C KA 1 B _0 / D QM A_ 5

D1 2

WCKA1_1/DQMA_6

E3

W C KA 1 B _1 / D QM A_ 7

F4

MA A0 _ 0/ MA A_ 0

K17

MA A0 _ 1/ MA A_ 1

J2 0

MAA 1_ 2/ M AA _ 1 0

J1 1

MAA 1_ 3/ M AA _ 1 1

J1 3

MAA 1_ 4/ M AA _ 1 2

H1 1

MAA1_5/MAA_13/BA2

G1 1

MAA1_6/MAA_14/BA0

J1 6

MAA1_7/MAA_15/BA1

L1 5

MA A0 _ 2/ MA A_ 2

H2 3

MA A0 _ 3/ MA A_ 3

G2 3

MA A0 _ 4/ MA A_ 4

G2 4

MA A0 _ 5/ MA A_ 5

H2 4

MAA 0_ 6/ M AA 0 _ 6

J1 9

MAA 0_ 7/ M AA 0 _ 7

K19

MA A1 _ 0/ MA A_ 8

J1 4

MA A1 _ 1/ MA A_ 9

K14

ADBI A0/OD TA0

L1 8

ADBI A1/OD TA1

K16

R ASA0B

G2 2

R ASA1B

G1 7

EDCA0_ 0/RD QSA_ 0

H2 8

EDCA0_ 1/RD QSA_ 1

C2 7

EDCA0_ 2/RD QSA_ 2

A23

EDCA0_ 3/RD QSA_ 3

E19

EDCA1_ 0/RD QSA_ 4

E15

EDCA1_ 1/RD QSA_ 5

D1 0

EDCA1_ 2/RD QSA_ 6

D6

EDCA1_ 3/RD QSA_ 7

G5

MAA 1_8 _R SV D

G1 4

MAA 0_ 8/ M AA _ 1 3

G2 0

DDBI A0_ 0/WD QSA_ 0

H2 7

DDBI A0_ 1/WD QSA_ 1

A27

DDBI A0_ 2/WD QSA_ 2

C2 3

DDBI A0_ 3/WD QSA_ 3

C1 9

DDBI A1_ 0/WD QSA_ 4

C1 5

DDBI A1_ 1/WD QSA_ 5

E9

DDBI A1_ 2/WD QSA_ 6

C5

DDBI A1_ 3/WD QSA_ 7

H4

WEA0B

G2 5

WEA1B

H1 0

DR AM_RST

L1 0

CL KT ESTA

K8

CL KT ESTB

L7

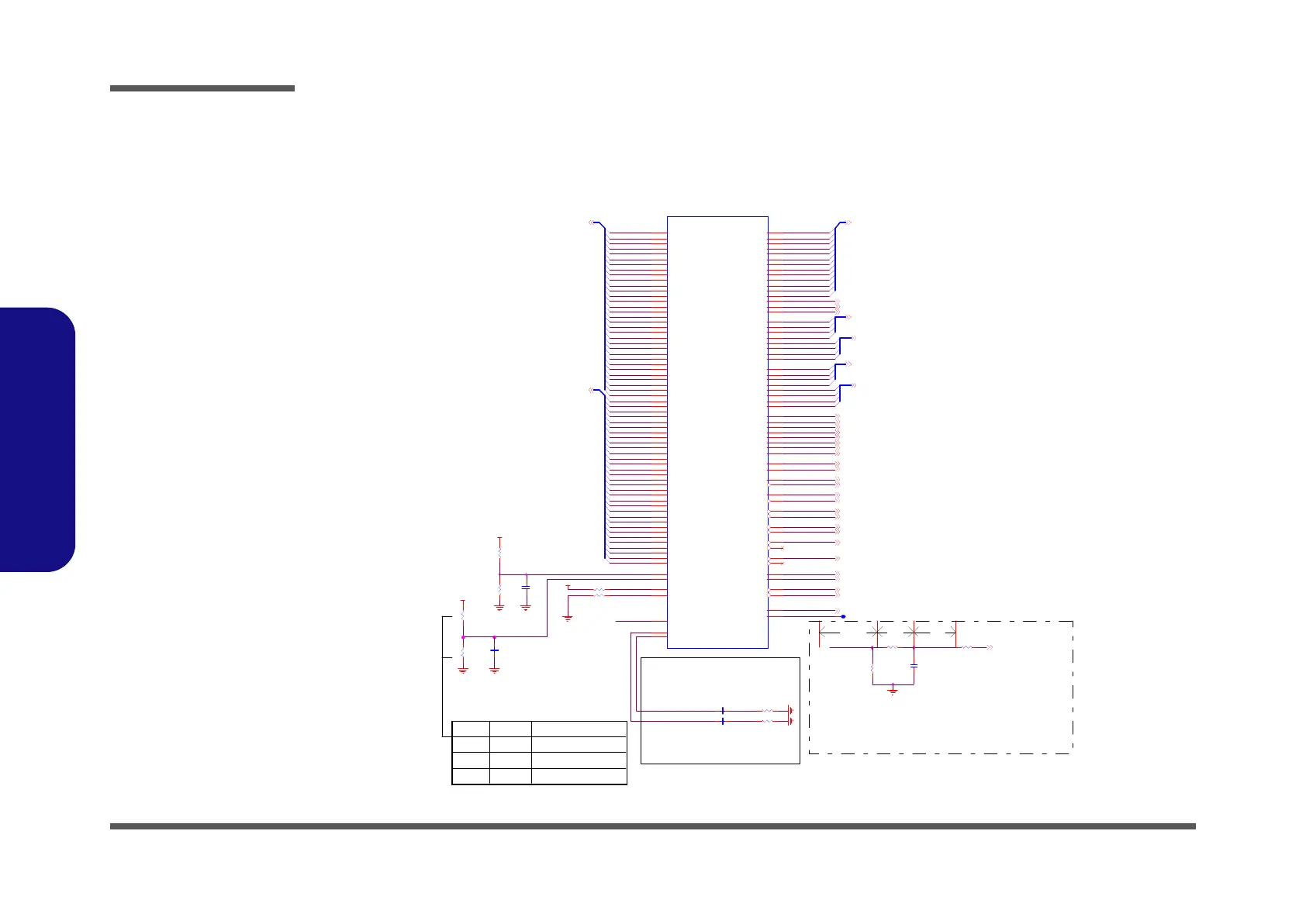

* 0 . 1 u _ 1 0 V_ X5 R _ 04

C2 06

* 51. 1_1 %_0 4

R 129

* 40. 2_1% _0 4

R122

*0 .1u _10V _X5R _0 4

C204

* 100 _04

R123

RSER 1

* 10 _04

* 0. 1u_1 0V _X5R _04

C2 07

* 0. 1u_ 10V _X5 R _04

C 205

*100_04

R1 27

*2 43_1 %_ 04R125

*5 1.1 _1% _04R 128

* 40 . 2_1 %_ 04

R1 26

*2 43_1 %_ 04R124

MVDD Q

MVDDQ

MV D D Q

QS A0_2 B 13

MAA [12 .. 0] 1 3, 14

CKEA0 13

CSA0b_0 13

QS A0_3 B 13

CLKA0 13

DQA 0_[ 31. .0]13

DQ MA0_[ 3 .. 0 ] 13

QS A0_0 B 13

ODT A0 13

MEM_RS T 13, 14

QS A0_1 B 13

MAA 13 13 , 1 4

R AS A0# 13

WEA 0# 13

C AS A0# 13

CKEA0

RASA0#

CS A0 b_0

CASA0#

CLKA0

ODTA 0

QS A1 _[ 3 .. 0 ] 14

A_BA0 13,14

A_BA2 13,14

A_BA1 13,14

CLKA1#

CASA1#

RASA1#

CLKA0#

CKEA1

WEA 1# 14

CKEA1 14

R AS A1# 14

DQMA 1_ [3. . 0] 1 4

DQMA1_ 2

DQMA1_ 3

DQMA1_ 0

DQMA1_ 1

CLKA1# 14

C AS A1# 14

WEA1#

CLKA0# 13

CLKA1 14

CLKA1

ODT A1 14

ODTA 1

CSA1b_0 14

CS A1 b_0

DQA 1_[ 31. .0]14

25mm (max)

DQA0_ 10

DQA0_ 3

DQA0_ 20

DQA0_ 19

DQA0_ 4

DQA0_ 22

DQA0_ 21

DQA0_ 24

DQA0_ 23

DQA0_ 5

DQA0_ 11

DQA0_ 0

DQA0_ 26

DQA0_ 25

DQA0_ 28

DQA0_ 27

DQA0_ 12

DQA0_ 6

DQA0_ 30

DQA0_ 29

DQA0_ 8

DQA0_ 1

DQA0_ 7

DQA0_ 2

DQA0_ 9

DQA0_ 31

DQA0_ 14

DQA0_ 13

DQA0_ 18

DQA0_ 17

DQA0_ 16

DQA0_ 15

COMPONENTS SHOWN ARE EXAMPLES ONLY

AND NOT NECESSARILY QUALIFIED

DME M_ RST

1 0.0

DDR3 Memory

Interface

From GPU

MA A1 _ 8

DDR3/GDDR 3 Me mory Stuff Option

WEA0#

MAA6

MAA1

MAA11

MAA9

MAA2

MAA10

MAA0

MAA8

MAA4

MAA7

MAA5

MAA3

DQMA0_ 3

DQMA0_ 0

DQMA0_ 1

DQMA0_ 2

Place all these components very close to GPU (Within

25mm) and keep all component close to each Other (within

5mm) except Rser2

MAA12

Ra

Ra

Ra

Rb

Rb

Rb

GDDR5

MVDDQ

5m m (m a x )

QS A1_0 B 14

QS A1_3 B 14

QS A1_2 B 14

QS A0_[ 3. . 0] 1 3

QS A1_1 B 14

QS A1 _3B

QS A1 _1B

QS A1 _2B

QS A1 _0B

MA A1 3

1.5V/1.8V

25mm (max)

This basi c topo logy s hould be use d for DRAM_ RST fo r DDR3 /GDDR5 .Thes e

Capa citor s and Resist or val ues ar e an exampl e only . The Series R an d

|| C ap va lues w ill de pend o n the DRAM load a nd wil l have to be

calc ulate d for diffe rent M emory ,DRAM Load and bo ard t o pass Rese t

Sign al Sp ec.

DDR3

DMEM_RST

1.5V

100R

40.2R

40.2R

100R

QS A0 _2B

QS A0 _3B

QS A0 _1B

QS A0 _2

QS A0 _0

QS A0 _1

QS A0 _3

QS A0 _0B

C LKTESTA

PLACE MVREF DIVIDERS

AND CAPS CLOSE TO ASIC

CLKTESTB

r oute 50o hms sin gle- ende d/1 00oh ms d iff

a nd k eep sho rt

D ebug onl y, for cloc k ob ser vati on, if n ot need ed, DNI

DQA1_ 6

DQA1_ 3

DQA1_ 2

DQA 1_11

DQA 1_10

DQA1_ 5

DQA1_ 4

DQA1_ 7

DQA1_ 9

DQA1_ 8

DQA 1_13

DQA 1_12

DQA 1_15

DQA 1_14

DQA 1_23

DQA 1_22

DQA 1_19

DQA 1_18

DQA1_ 0

DQA1_ 1

DQA 1_17

DQA 1_16

DQA 1_21

DQA 1_20

DQA 1_29

DQA 1_28

DQA 1_31

DQA 1_30

DQA 1_27

DQA 1_26

DQA 1_25

DQA 1_24

QS A1 _1

QS A1 _3

QS A1 _2

QS A1 _0

Loading...

Loading...