9

8xC251Tx Hardware Description

3.2 Special Function Register Definitions

The following describes the special function registers associated with the second serial I/O port and their bit

definitions.

3.2.1 SCON1

Address: 9AH

Reset Value: 0000 0000B

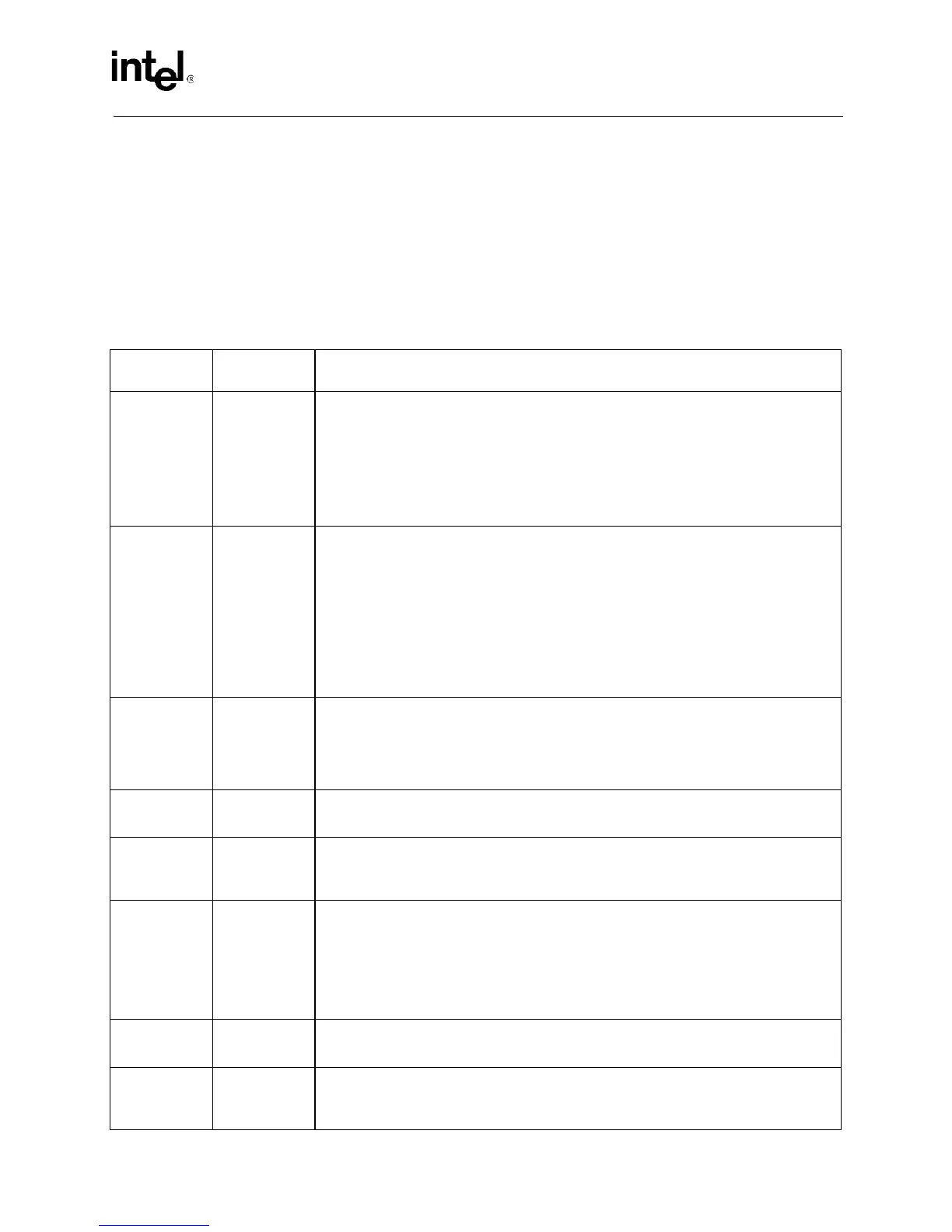

Table 6. SCON1 Special Function Register Definitions

Bit Number

Bit

Mnemonic

Function

7 FE1SM0 Framing Error Bit 1:

To Select this function, set the SMOD0 bit in the BGCON register. Set by hard-

ware to indicate an invalid stop bit. Cleared by software, not by valid frames

Second Serial I/O Port Mode Bit 0:

To select this function, clear the SMOD0 bit in the BGCON register. Software

writes to bit SM0 and SM1 to select the second serial I/O port operating

mode. Refer to SM1 bit for mode selections

6 SM1 Second Serial I/O Port Mode Bit 1:

Software write to bit SM0 and SM1 (above) to select the serial port operating

mode.

SM0 SM1 Mode Description Baud Rate

0 0 0 Shift Register Fosc/12

0 1 1 8 bit UART variable

1 0 2 9 bit UART Fosc/32* or Fosc/64*

1 1 3 9 bit UART variable

* Select by programming the SMOD0 bit in the BGCON register

5 SM2 Second Serial I/O Port Mode Bit 2:

Software writes to SM2 enable and disable the multiprocessor communica-

tion and automatic address recognition features. This allows the second

serial I/O port to differentiate between data and command frames and to rec-

ognize slave and broadcast addresses

4 REN1 Receive Enable Bit 1:

To enable reception, set this bit. To enable transmission, clear this bit

3 TB8 Transmit Bit 8:

In modes 2 and 3, software writes the ninth data bit to be transmitted to TB8.

Not used in modes 0 and 1

2 RB8 Receive Bit 8:

Mode 0: not used

Mode 1 (SM2 clear): Set or cleared by hardware to reflect the stop bit

received

Modes 2 and 3 (SM2 set): Set or cleared by hardware to reflect the ninth

data bit received

1 TI1 Second Serial I/O Port Transmit Interrupt Flag Bit:

Set by transmitter after the last data bit is transmitted. Cleared by software

0 RI1 Second Serial I/O Port Receive Interrupt Flag Bit:

Set by the receiver after the last data bit of a frame has been received.

Cleared by software

Loading...

Loading...