13

8xC251Tx Hardware Description

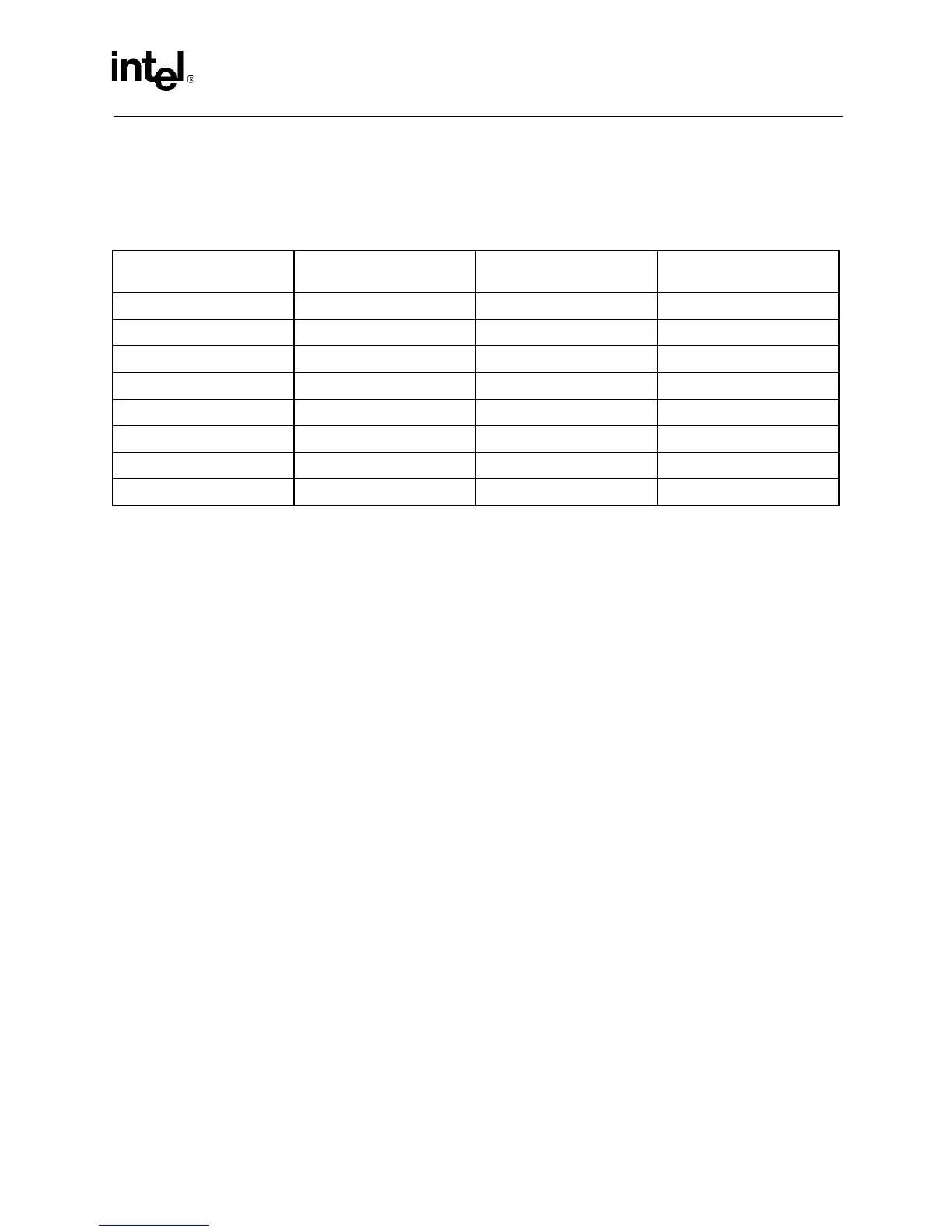

Table 13 shows the effect of programming EDF# and WSB#[1:0] on the extended data float timing feature as

well as the insertion of wait states for region 01:. It should be noted that enabling the extended data float

timing allows region 01: to have 1 or 3 wait states inserted (depending on WSB#[1:0]) but not 0 or 2 wait

states.

The external user configuration cycle (UCONF = 1 and EA# = 0) will be executed with the extended TRHDZ1

timing bus cycle.

Table 13. Summary of the EDF# and WSB#[1:0] Configuration Options

EDF# WSB#[1:0] Wait State

Extended Data Float

Timings

1 11 0 No

1 10 1 No

1 01 2 No

1 00 3 No

0 11 1 Yes

0 10 1 Yes

0 01 3 Yes

0 00 3 Yes

Loading...

Loading...