Technical Reference

47

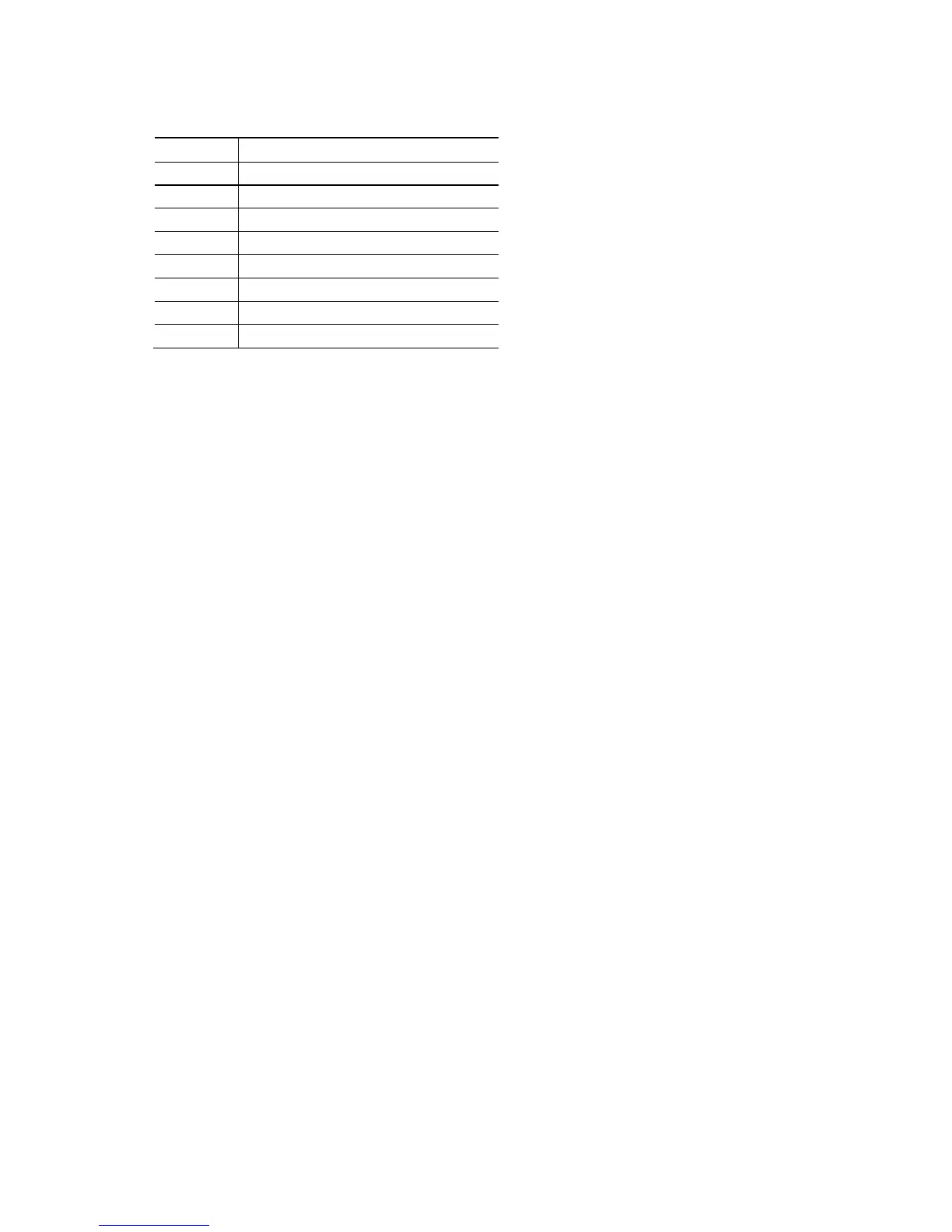

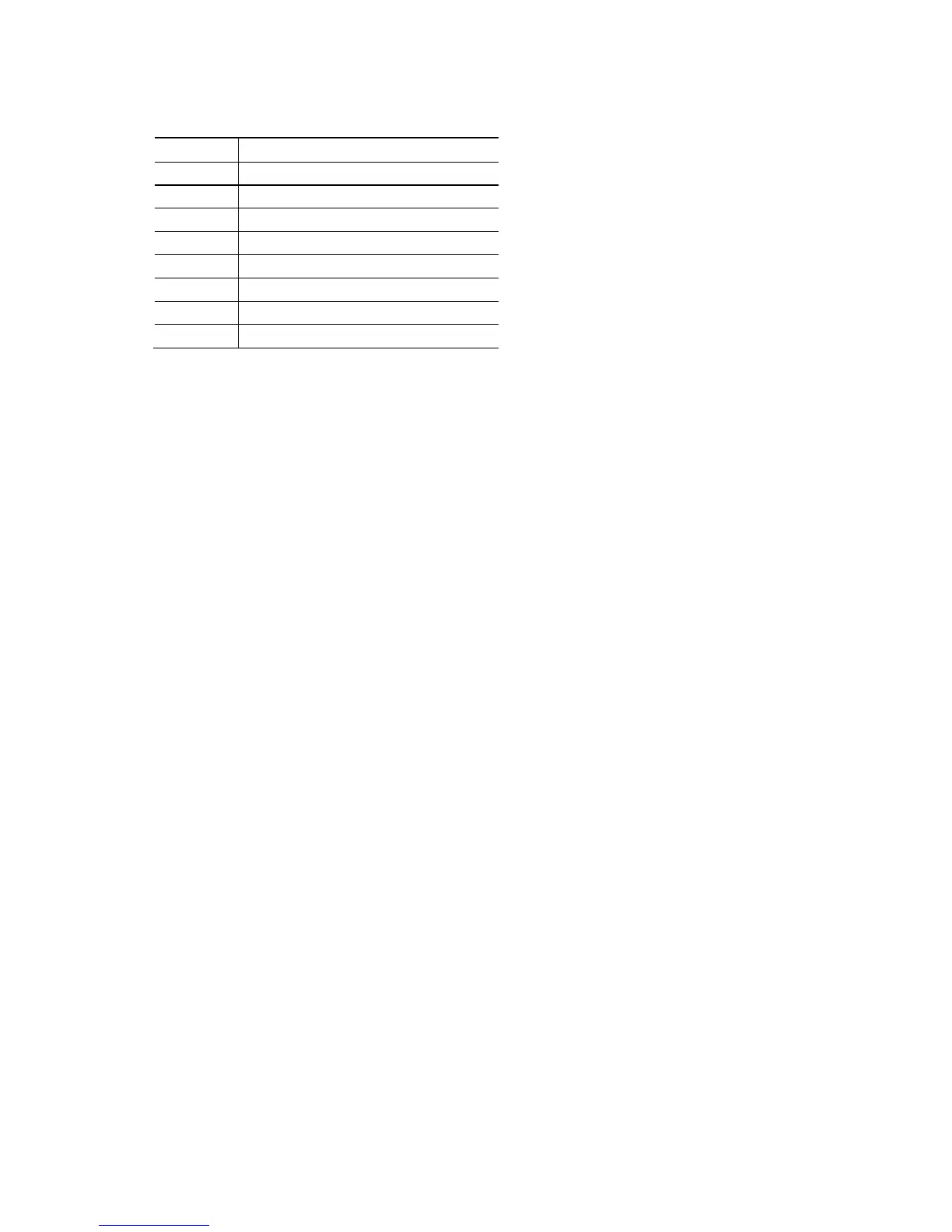

Table 21. Front Panel CIR Receiver (Input) Header

Pin Signal Name

1 Ground

2 LED

3 NC

4 Learn-in

5 5 V standby

6 VCC

7 Key (no pin)

8 CIR Input

2.2.2.2 Add-in Card Connectors

The board has the following add-in card connectors:

• PCI Express 2.0 x16: one PCI Express 2.0 x16 connector supporting simultaneous

transfer speeds up to 8 GB/s of peak bandwidth per direction and up to 16 GB/s

concurrent bandwidth.

• PCI Express 2.0 x1: two PCI Express 2.0 x1 connectors. The x1 interface

supports simultaneous transfer speeds up to 2.5 Gb/s of peak bandwidth per

direction and up to 5.0 Gb/s concurrent bandwidth.

• PCI Conventional (rev 2.3 compliant) bus: three PCI Conventional bus add-in card

connectors.

Note the following considerations for the PCI Conventional bus connectors:

• The PCI Conventional bus connectors are bus master capable.

• SMBus signals are routed to the PCI Conventional bus connectors. This enables

PCI Conventional bus add-in boards with SMBus support to access sensor data on

the desktop board. The specific SMBus signals are as follows:

⎯ The SMBus clock line is connected to pin A40.

⎯ The SMBus data line is connected to pin A41.

Loading...

Loading...