Intel DZ77GA-70K / DZ77RE-75K Desktop Board Performance Tuning Guide

34

B Parameter Descriptions for

Memory Performance Settings

NOTE

All multiplier values listed in Table B- are applied to the single 100 MHz (default) host

clock.

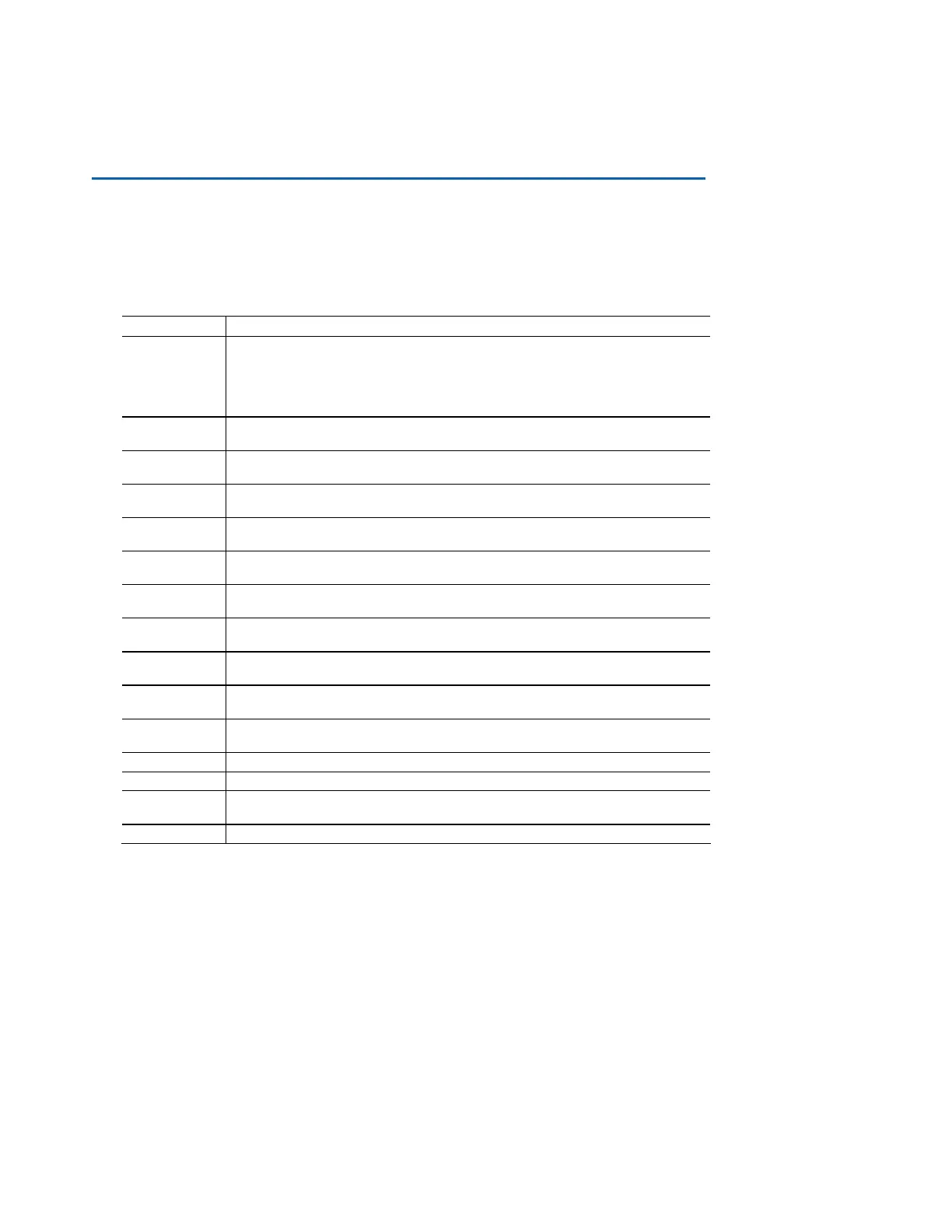

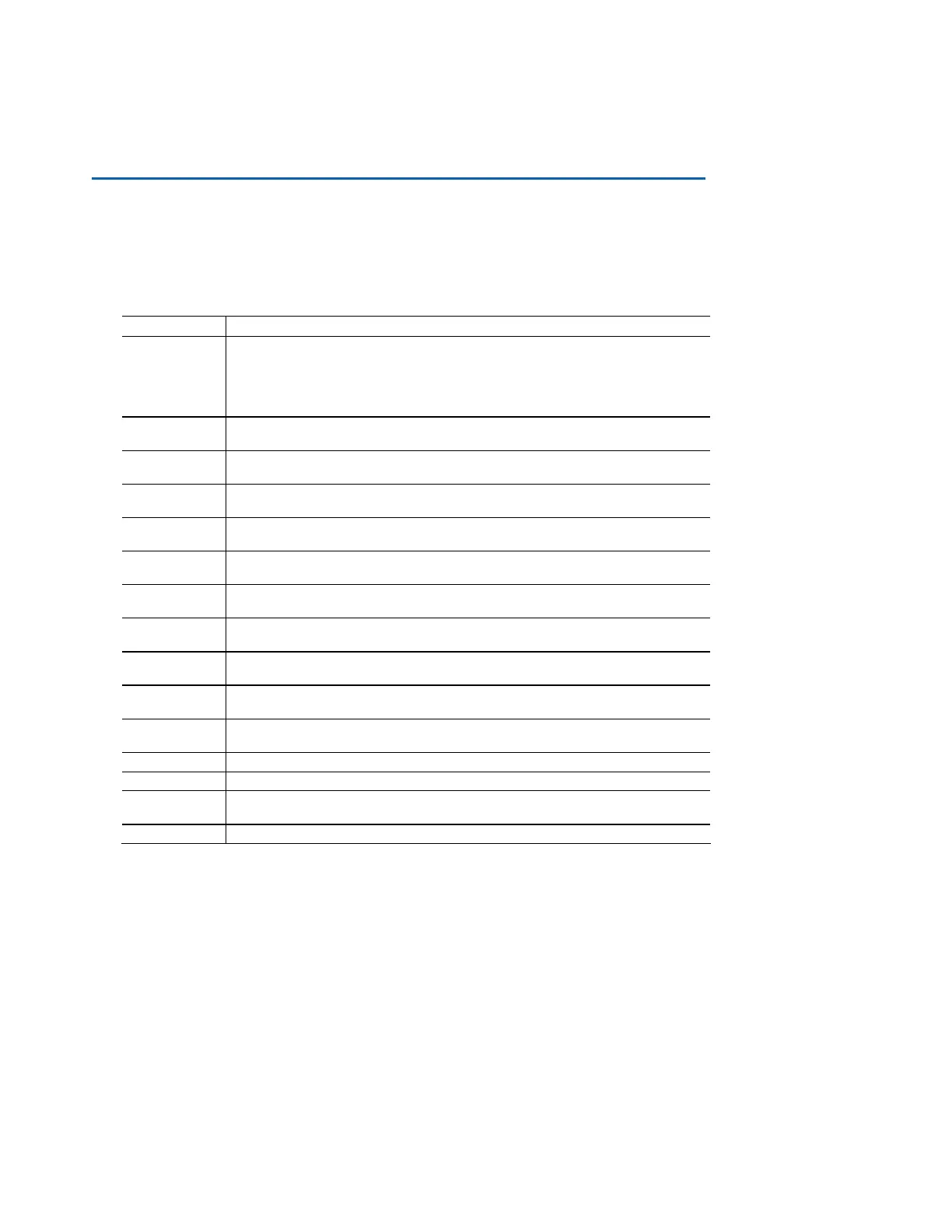

Table B-1. Memory Performance Settings

Setup Option Description

Performance

Memory Profiles

Automatic setting uses specification compliant values provided by the memory module.

If the memory module supports XMP there will be additional selections for each profile

stored in the module. Selecting a profile will populate all the settings with values

recommended by the DIMM manufacturer. Selecting Manual Mode after XMP allows the

user to change each of the settings.

Memory

Multiplier

Allows selection of memory speed from a list of choices.

tCL Column address strobe (CAS) Latency: The amount of time in cycles between sending a

read command and the time to act on it.

tRCD Row address strobe (RAS) to CAS Delay: The amount of time in cycles for issuing an

active command and the read/write commands.

tRP RAS Precharge Time: This is the minimum time between active commands and the

read/writes of the next bank on the memory module.

tRASmin Minimum RAS Active Time: The amount of time between a row being activated by

precharge and deactivated.

tRFC RAS Refresh Cycle Timing: This determines the amount of cycles to refresh a row on a

memory bank.

tRRD RAS to RAS Delay: The amount of cycles that it takes to activate the next bank of

memory.

tWR Write Recover Time: The amount of cycles that are required after a valid write operation

and precharge.

tWTR Write to Read Delay: The amount of cycles required between a valid write command and

the next read command.

tRTP Controls the number of clocks that are inserted between a row precharge command and

an activate command to the same rank.

Memory Voltage Changes the voltage applied to the memory.

Command Rate The amount of time that commands can be issued.

tRC Determines the minimum number of clock cycles used complete row activation to

precharging of the active row.

tFAW Specifies the time window where four activates are allowed in the same rank.

Loading...

Loading...