System Event Log Troubleshooting Guide for EPSD

Platforms Based on Intel

®

Xeon

®

Processor E5 4600/2600/2400/1600/1400 Product Families

Cooling Subsystem

Revision 1.1 Intel order number G90620-002 57

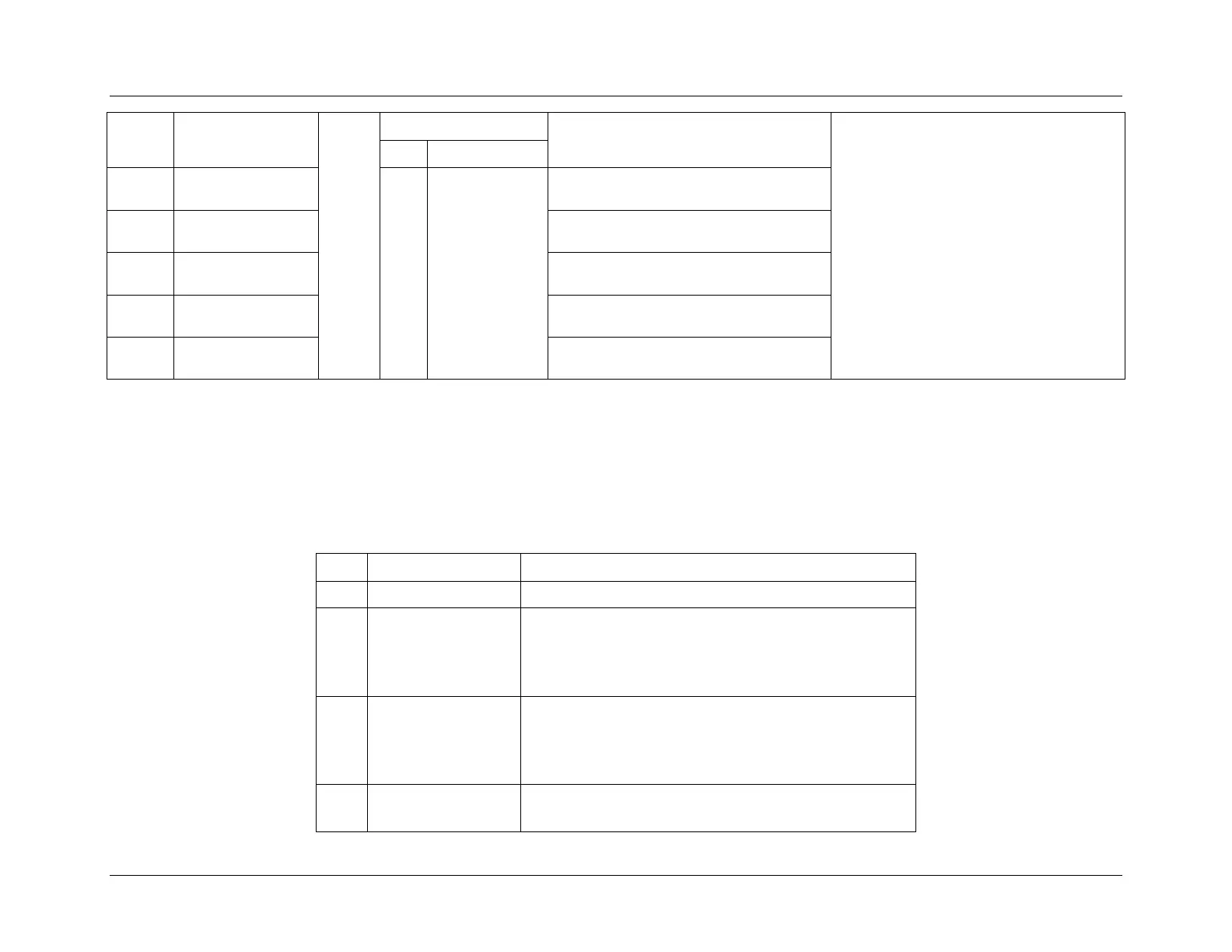

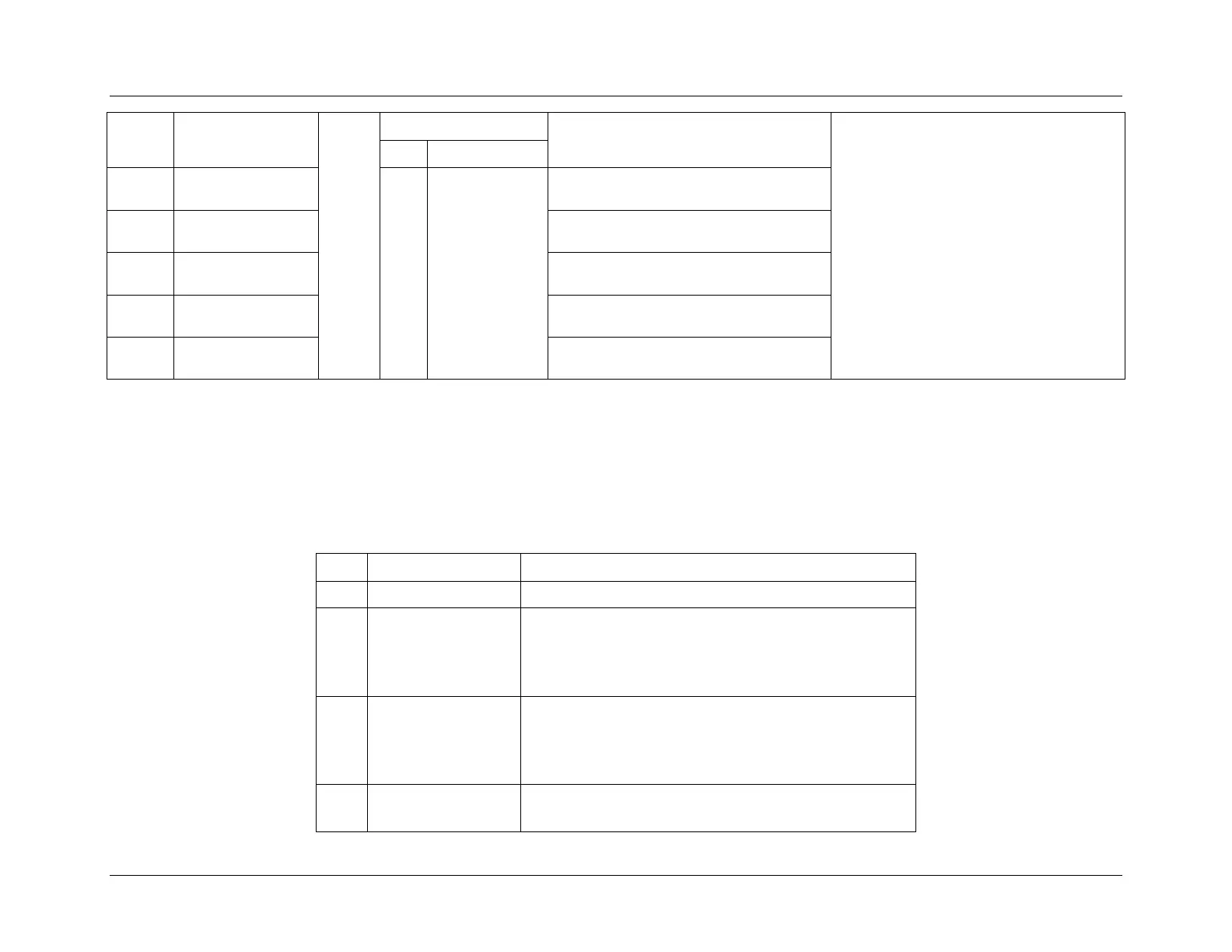

Processor 2 Memory 2/3 voltage regulator

overheated

Processor 3 Memory 0/1 voltage regulator

overheated

Processor 3 Memory 2/3 voltage regulator

overheated

Processor 4 Memory 0/1 voltage regulator

overheated

Processor 4 Memory 2/3 voltage regulator

overheated

5.2.6 DIMM Thermal Trip Sensors

The BMC supports DIMM Thermal Trip monitoring that is instantiated as one aggregate IPMI discrete sensor per CPU. When a

DIMM Thermal Trip occurs, the system hardware will automatically power down the server and the BMC will assert the sensor offset

and log an event.

Table 46: DIMM Thermal Trip Typical Characteristics

C0h = Processor 1 DIMM Thermal Trip

C1h = Processor 2 DIMM Thermal Trip

C2h = Processor 3 DIMM Thermal Trip

C3h = Processor 4 DIMM Thermal Trip

Event Direction and

Event Type

[7] Event direction

0b = Assertion Event

1b = Deassertion Event

[6:0] Event Type = 6Fh (Sensor Specific)

[7:6] – 00b = Unspecified Event Data 2

[5:4] – 00b = Unspecified Event Data 3

Loading...

Loading...