Intel® Xeon™ Processor with 512 KB L2 Cache System Compatibility Guidelines

10

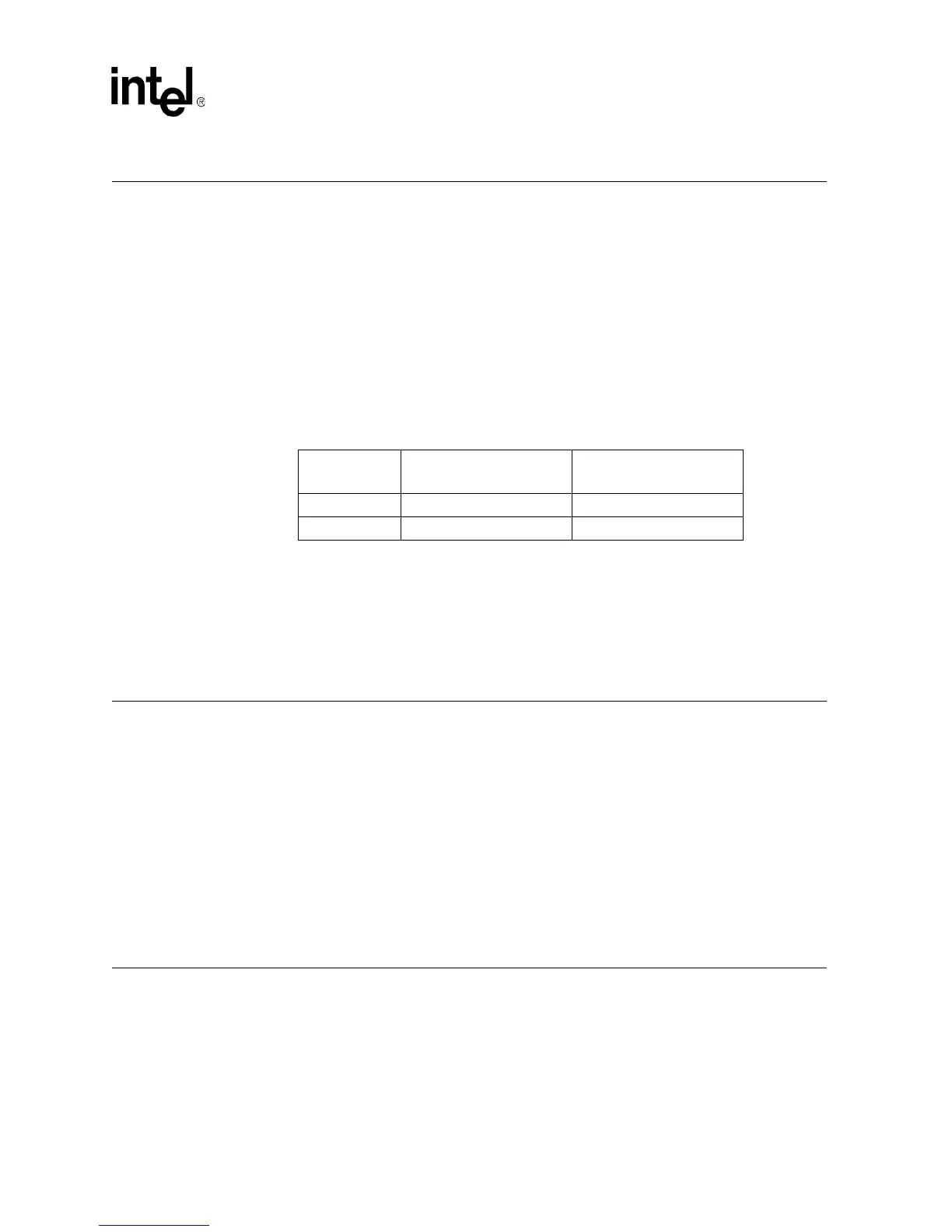

7.0 Power and Signal Levels

The VID for the Intel® Xeon™ processor with 512 KB L2 cache is 1.500 volts compared to

a VID level of 1.700 volts for the Intel Xeon processor. The Intel Xeon processor with 512

KB L2 cache still uses a single core voltage supply (V

CC

) to supply the termination voltage

(V

TT

). Table 2 outlines changes to the way AGTL+ signal level specifications are defined

for the Intel Xeon processor with 512 KB L2 cache. The Intel Xeon processor with 512 KB

L2 cache defines the V

IH

and V

IL

specifications based on a percentage of the GTLREF

level instead of a fixed voltage offset level. In Table 2, use a value of GTLREF = 2/3*V

CC

for both processors. It is important to simulate the system bus to ensure that these levels

are met. Other bus electrical characteristics are expected to be compatible with the Intel®

Xeon™ processor specifications. Refer to the processor datasheets given in Section 2.2

for complete details regarding all processor specifications referenced in this section.

NOTE: These values are for reference only. The latest processor datasheet contains the actual specifications

for the processor. If the specifications in this table conflict with the specifications found in the datasheet,

the datasheet supersedes.

8.0 VRM 9.0 and VRM 9.1

Voltage regulator designs for Intel® Xeon™ processor-based platforms were initially

basedonIntel’sVRM 9.0 DC-DC Converter Design Guidelines. However, to provide

additional VRM high current capability for new platforms, Intel created an updated voltage

regulator design guide entitled VRM 9.1 DC-DC Converter Design Guidelines. Intel Xeon

processor platforms intending to support the Intel Xeon processor with 512 KB L2 cache

are not required to upgrade to VRM 9.1 and may continue to use VRM 9.0 voltage

regulator solutions. However, new platforms should consider implementing VRM 9.1 since

it provides the most recent voltage regulator design guidelines for the Intel Xeon

processor with 512 KB L2 cache.

9.0 Core Frequency to System Bus Ratio Determination

The core frequency to system bus ratio for the Intel® Xeon™ processor is configured by

driving the ratio select signals (LINT[1]/NMI, A20M#, IGNNE#, and LINT[0]/INTR) with

appropriate ratio encoding values during processor power-on reset. The Intel Xeon

processor with 512 KB L2 cache implements a new method for setting the core frequency

to system bus ratio and will ignore the ratio select signals at power-on reset. The Intel

Table 2. AGTL+ Signal Changes

Symbol Intel® Xeon™ Processor

Intel® Xeon™ Processor

with 512 KB L2 Cache

V

IL

Max GTLREF - 0.100 0.90*GTLREF

V

IH

Min GTLREF + 0.100 1.10*GTLREF

Loading...

Loading...