9

Intel® Xeon™ Processor with 512 KB L2 Cache System Compatibility Guidelines

PWRGOOD input to the processor. PWR_OK will be deasserted when any output of an

ATX12V-compliant or SSI-compliant power supply falls below regulation limits. It is

important to maintain SM_VCC at any time the output of the VRM is enabled. Driving the

VRM’s OUTEN with the PWR_OK signal will ensure correct sequencing at both power up

and power down.

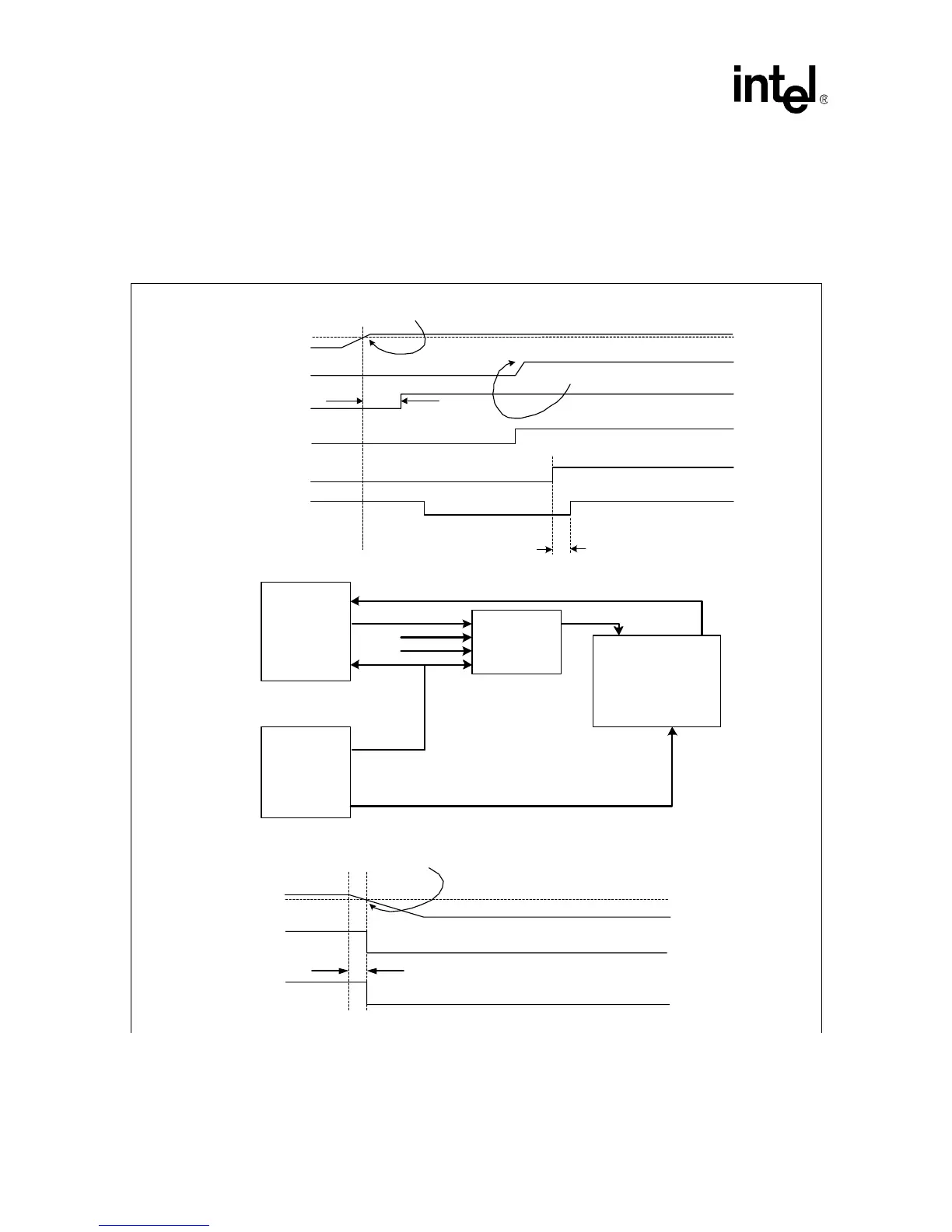

Figure 1. Voltage Sequence Timing Requirements

VRM

Power

Supply

Processor

VID[4:0]

3.3 VDC

PWR_OK

OUTEN

PWRGD

PWRGOOD

SM_VCC

3.3 VDC/SM_VCC

PWROK

OUTEN

Power Down

3.3 VDC/SM_VCC

PWR_OK /

VID_OUT

OUTEN

VRM

PWRGD

Processor

PWRGOOD

Processor

RESET

T

0

= 95% 3.3 volt level

Power Up

SM_VCC out of

regulation

T

0

+10mS

> valid p/s voltages + 100 ms

Power Down Warning > 1ms

1ms < T

36

<10ms

System

PWRGD

Logic

...

...

VID

VID

Loading...

Loading...