5

4

3

2

1

A

BC

DE

F

G

2-11 2-12

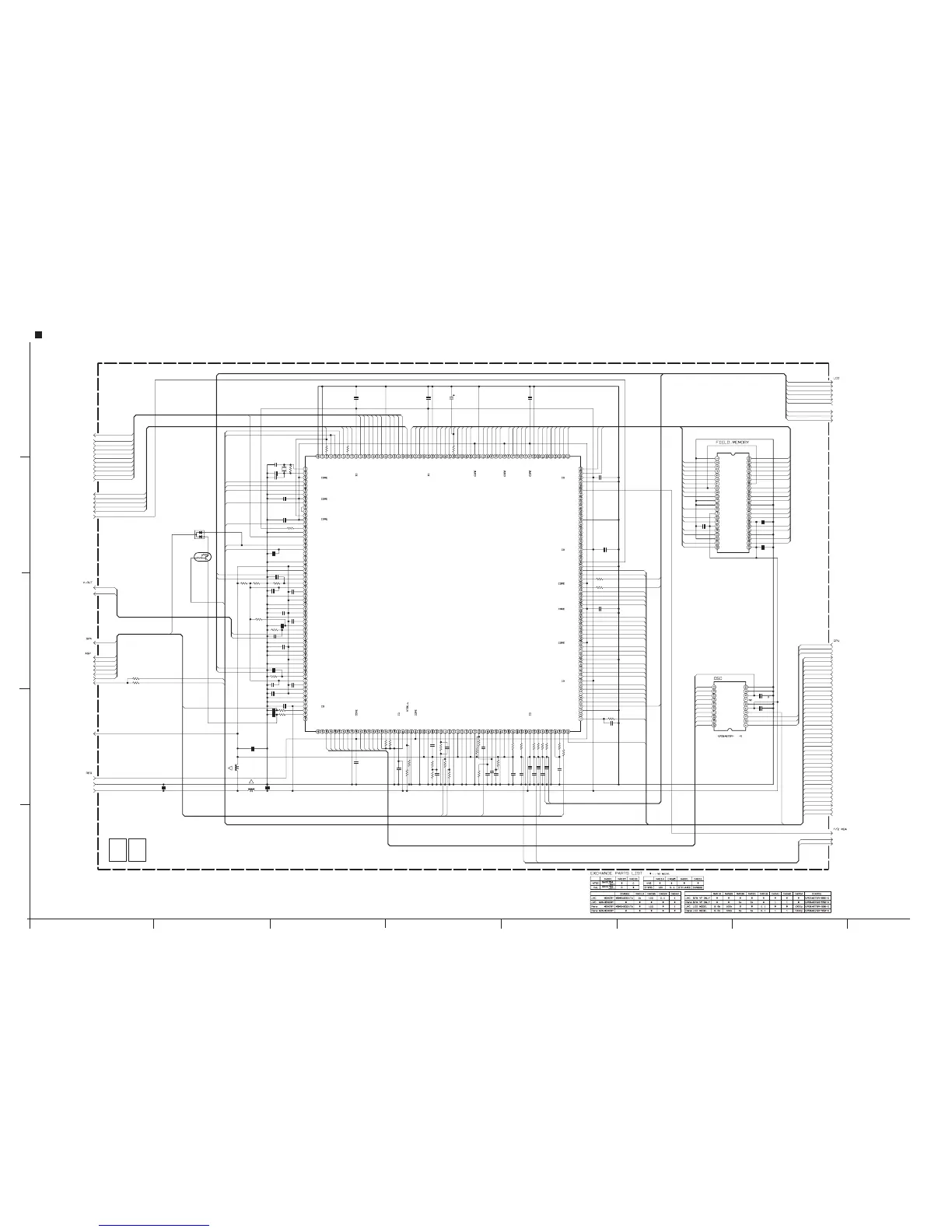

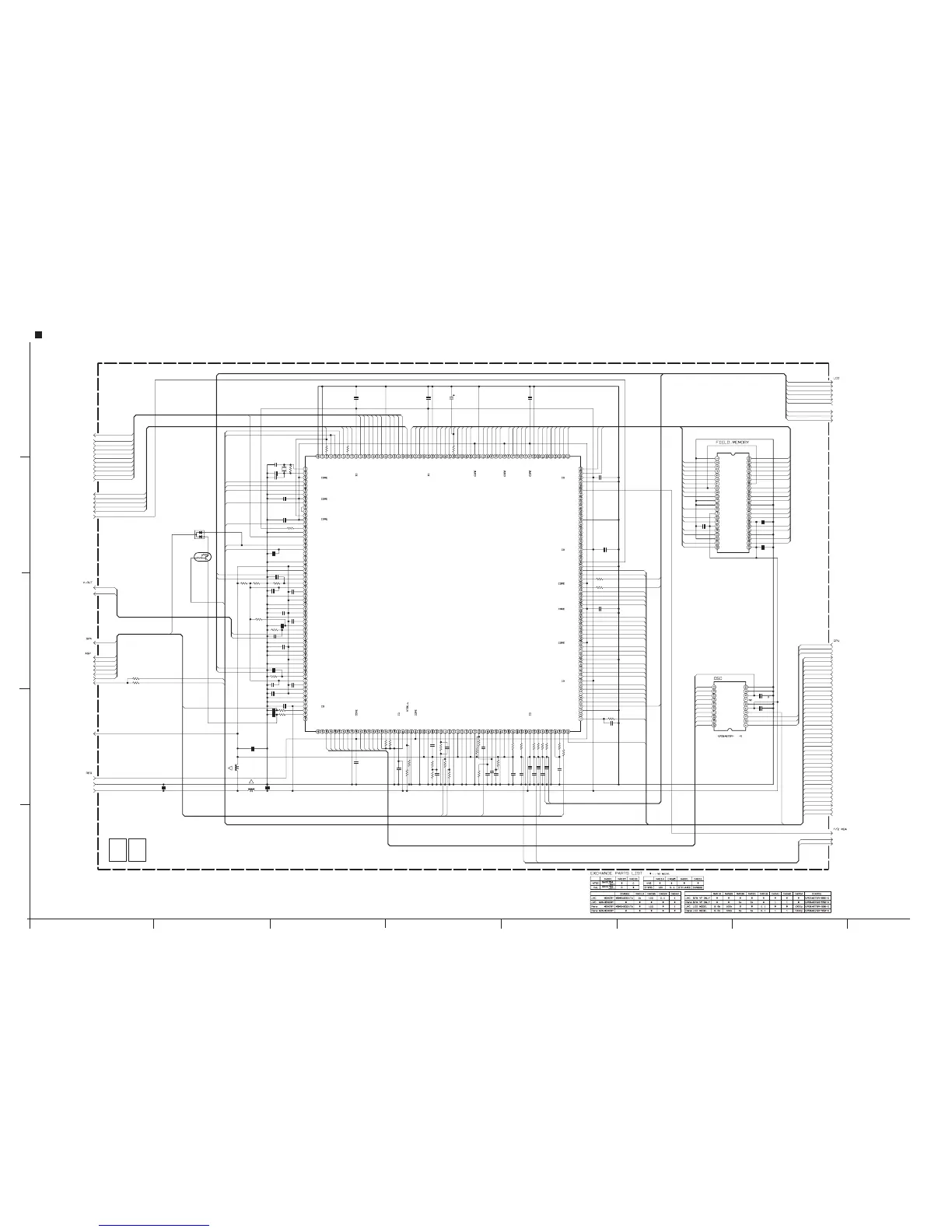

MAIN(DSP)

SCHEMATIC DIAGRAM

IC4001

VDDSC

C4047

C4002

C4003

C4004

C4046

V_FF

C4008

X4001

PBLK

R4003

C4012

C4020

C4015

C4011

C4021

C4023

R4038

C4031

AD_9

AD_8

AD_7

AD_6

AD_5

AD_4

AD_3

AD_2

AD_1

GND

REG_3.2V

AD_0

C4045

LHFO

C4044

HDTG

VDTG

ID

VD_H

FI

DSP_REST

TG_CLK

C4009

C4010

R4002

GOUT

CDS_CLK

OMT

R4041

C4014

C4016

R4004

R4009

ROUT

C4018

C4019

R4010

R4039

C4013

C4017

CAM_Y

CAM_C

CLKCPU

C4026

BOUT

R4042

R4013

R4014

C4025

Q4001

D4001

V_OVL

S_DET+

V_REC_C

V_REC_F

2FSC

V_PB_F

R4035

R4034

SH_SIG

SPK_VOL

BWYOUT

BWBLEVEL

BWYGAIN

V_DSP_CS

V_PULSE

REG_2V

V_PLS_ON

V_OVL_A

V_OVL_B

S_DET_L

SDET_CTL

H_OFFSET

H_GAIN

R4001

C4001

AD15

AD14

C4024

R4045

C4052

DAC_3.2V AD13

AD12

AD11

AD10

AD9

AD8

AD7

AD6

AD5

AD4

AD3

AD2

AD1

AD0

ASTB

R/W_L

DSTB_L

HD_H

CFM

WAIT_L

VDVHS

SCK3

SO3

L4002

HRP1

VDCVF

OSD_DATA

OSD_CLK

OSD_CS

HDCVF

IC4003

C4049

C4051

C4050

IC4002

C4053

C4054

R4026

R4036

C4043

C4034

C4005

C4007

R4037

C4006

C4027

C4028

C4036

C4038

C4048

R4040

R4017

R4018

L4001

R4020

R4019

R4021

R4032

C4029

C4030

C4032

C4033

C4035

R4016

R4015

R4022

R4025

R4033

R4027

R4028

R4029

R4030

R4031

C4037

C4039

C4040

C4041

C4042

R4044

R4043

C4055

R4023

R4024

COUT

IRSETC

VREFC

SCLEARI

VREFBWY

DSTB

HRP2

GND1

HRP1

RW

ASTB

BUS[0]

BUS[2]

BUS[1]

VDD1

BUS[3]

BUS[4]

BUS[5]

BUS[6]

BUS[7]

BUS[8]

BUS[9]

GND2

VDD2

BUS[10]

BUS[11]

BUS[12]

BUS[13]

BUS[14]

BUS[15]

GND3

VDD3

HDCPU

VDCPU

FLDCPU

FRP

HDCVF

VDD4

VDCVF

OMT

BUSY

GND4

PBLK

DSY[0]

DSY[1]

VDD5

DSY[2]

DSY[3]

DSY[4]

DSY[5]

DSY[6]

DSY[7]

GND5

DSC[0]

DSC[1]

DSC[2]

DSC[3]

FMY[1]XIN

XOUT

VDD12

SDCK

SLD

STD

GND12

VDD13

SW30

DOCK

DCKI

VDD14

GND13

YOUT

CLKI

CLKCPU

AD1_CK

CAMADCK

SVHSOUT

CSYNC

AD2_CK

BWYO

NC

IRSETBWY

BYOUT

Y2OUT

RYOUT

IRSETRY

VREFRY

VDD16

KOUT

CLKDSC

FLDDSC

VDDSC

HDDSC

GND6

VDD6

FMY[0]

CLR

TMS

ASEL

AVDD

AVSS

AVDD

AVDD

AVSS

AVBB

AVDD

AVDD

NC

AVSS

AVDD

AVSS

TVTR1

NC

NC

AVSS

NC

NC

GND

NC

NC

JCY0184

CH

#

CH

#

#

#

#

#

#

#

#

#

CLK

CS

DATA

PCL

VDD

CKOUT

OSOUT

OSCIN

TEST

GND

HSYNC

VSYNC

VB

VG

VR

VBLK

VC2

BLK2

VC1

BLK1

#

VSS

DIN5

DIN4

DIN3

DIN2

DIN1

DIN0

RCLK

RXAD

RADE/RX

RR

RXINC

RE

OE

DO0

DO1

VCC

DO2

DO3

VSS

DO4

DO5 VCC

DO6

DO7

VSS

DO8

DO9

VCC

DO10

DO11

WE

IE

WXINC

WR/TR

WADE/RX

WXAD

WCLK

DIN11

DIN10

DIN9

DIN8

DIN7

DIN6

#

TMC[1]

TMC[2]

TMC[3]

MCLK

FMWR

RAD

WAD

IE

GND9

VDD10

FMRE

FMWE

ADIN[9]

ADIN[8]

ADIN[7]

ADIN[6]

GND10

ADIN[5]

ADIN[4]

ADIN[3]

ADIN[2]

ADIN[1]

ADIN[0]

VDD11

ID

HDTG

VDTG

VG

VB

BLK1

BLK2

VBLK

RECCOUT

SCBLKO

IRSETFMY

VREFFMY

FMY[2]

FMY[3]

FMY[4]

FMY[5]

FMY[6]

FMY[7]

FMC[0]

FMC[1]

GND7

VDD7

FMC[2]

FMC[3]

TMY[0]

TMY[1]

TMY[2]

VDD8

TMY[3]

TMY[4]

TMY[5]

TMY[6]

TMY[7]

GND8

VDD9

TMC[0]

RAE

WAE

LHFO

SDPRD

HDMASK

ADDV

CAMCK

GND11TRST

VDOSD

HDOSD

CLKOSD

VC1

VC2

VR

FMOUT

AVDD

REFTOPI

REFBOTI

STB

PD

NC

PWMOUT1

GND17

VDD20

PWMOUT2

PWMOUT3

PWMOUT4

PWMOUT5

GND18

DICK

DCKO

FSC2OUT

VREFO

TCK

TDI

TDO

TVSELO

VIN

GND11B

GND14

VDD17

GND15

VDD18

GND16

VDD19

AVSS

AVDD

AVDD

NC

AVSS

AVSS

AVSS

AVDD

NC

NC

NC

TVTR2

VPD

NC

#

CH

CH CHCH

#

#

#

#

#

#

#

0.1

0.1

0.1

0.1

220

0.1

56k

0.1

0.1

0.1

0.1

470

1

1

10p

10p

1M

2.2k 6.8k

2.7k

0.1

470

0.1

0.1

10

1.2k

3.3k

3.3k

1k

0

1000p

22

µ

0.1

1000p

1000p

0.1

0.1

1k

0.1

0.1

0.1

0.1

120

22

µ

220

2.7k

100

0

0.1

0.1

0.1

0.1

1.5k

1.5k

3.9k

100k

100k

0.1

0.1

0.1

2.2k

1.2k

1000p

0

FMY_0

TMY_0

SCK3

FRP

FMY_1

OMT

FMY_2

FMY_3

TMY_6

TMY_7

TMC_0

TMC_1

TMC_2

TMC_3

WAD

WAE

FMWR

FMWE

TMY_1

TMY_5

TMY_4

TMY_3

TMY_2

FMC_0

FMC_1

FMRE

RAE

RAD

FCLK

FMY_4

FMY_5

WAIT

FMY_6

FLDCPU

VDCPU

HDCPU

AD15

AD14

AD13

AD12

AD11

AD10

AD9

AD8

AD7

AD6

AD5

AD4

AD3

AD2

AD1

AD0

VDVHS

STB

RE

DSTB

VDCVF

BW_Y

HDCVF

HRP1

FMY_7

FMC_2

FMC_3

IE

DA_G

DA_R

DA_B

SPK_VOL

SH_SIG

CAM_Y

CAM_C

SH_SIG

S_DET+

HDOSD

LHFO

HDTG

VDTG

ID

TG_CLK

V_REC_C

V_REC_F

2FSC

V_PB_F

VFF

AD_9

AD_8

AD_7

AD_6

AD_5

AD_4

AD_3

AD_2

AD_1

AD_0

DSP_REST

HDCVF

CDS_CLK

VDCVF

DA_B

DA_G

DA_R

VFF

CAM_Y

CAM_C

OSD_DATA

OSD_CS

SO3

V_DSP_CS

HRP1

OSD_CLK

VDVHS

CLKCPU

V_PLS_ON

S_DET_L

SO3

V_DSP_CS

SCK3

V_PULS

V_OVL_A

V_OVL_B

BW_Y

DAC4

DAC5

V_PULS

V_PLS_ON

V_OVL_A

V_OVL_B

S_DET_L

SDET_CTL

SDET_CTL

H_GAIN

H_OFFSET

CLKCPU

DSTB

RE

STB

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

AD10

AD11

AD12

AD13

AD14

AD15

OMT

FRP

HDCPU

VDCPU

FLDCPU

DSP_REST

WAIT

CLKOSD

OSD_DATA

OSD_CS

OSD_CLK

VC_1

VDOSD

VBLK

BLK_2

BLK_1

VB

VG

VR

VC_2

IE

WAD

RAD

FCLK

TMC_3

TMC_2

TMC_1

TMC_0

TMY_7

TMY_6

TMY_5

TMY_4

TMY_3

TMY_2

TMY_1

TMY_0

FMC_3

FMC_2

FMC_1

FMC_0

FMY_7

FMY_6

FMY_5

FMY_4

FMY_3

FMY_2

FMY_1

AD_9

FMY_0

WAE

FMWR

AD_8

AD_7

AD_6

AD_5

AD_4

AD_3

AD_2

AD_1

AD_0

TG_CLK

VDTG

HDTG

ID

LHFO

FMRE

FMWE

RAE

V_PB_F

CDS_CLK

VBLK

BLK_2

BLK_1

VB

VG

VR

VC_2

VC_1

CLKOSD

HDOSD

DSP_REST

VDOSD

V_REC_C

V_REC_F

2FSC

SPK_VOL

DAC5

DAC4

S_DET+

H_OFFSET

H_GAIN

0 1

MAIN(DSP)

556

y10411001a_rev0.1

NOTES : 1. The parts with marked() is not used.

2. For DSP waveforms,please refer to page 2-43.

NOTES : ٨For the destination of each signal and further line connections that are cut off from this diagram,

refer to "BOARD INTERCONNECTIONS".

٨When ordering parts, be sure to order according to the Part Number indicated in the Parts List.

!

!

Loading...

Loading...