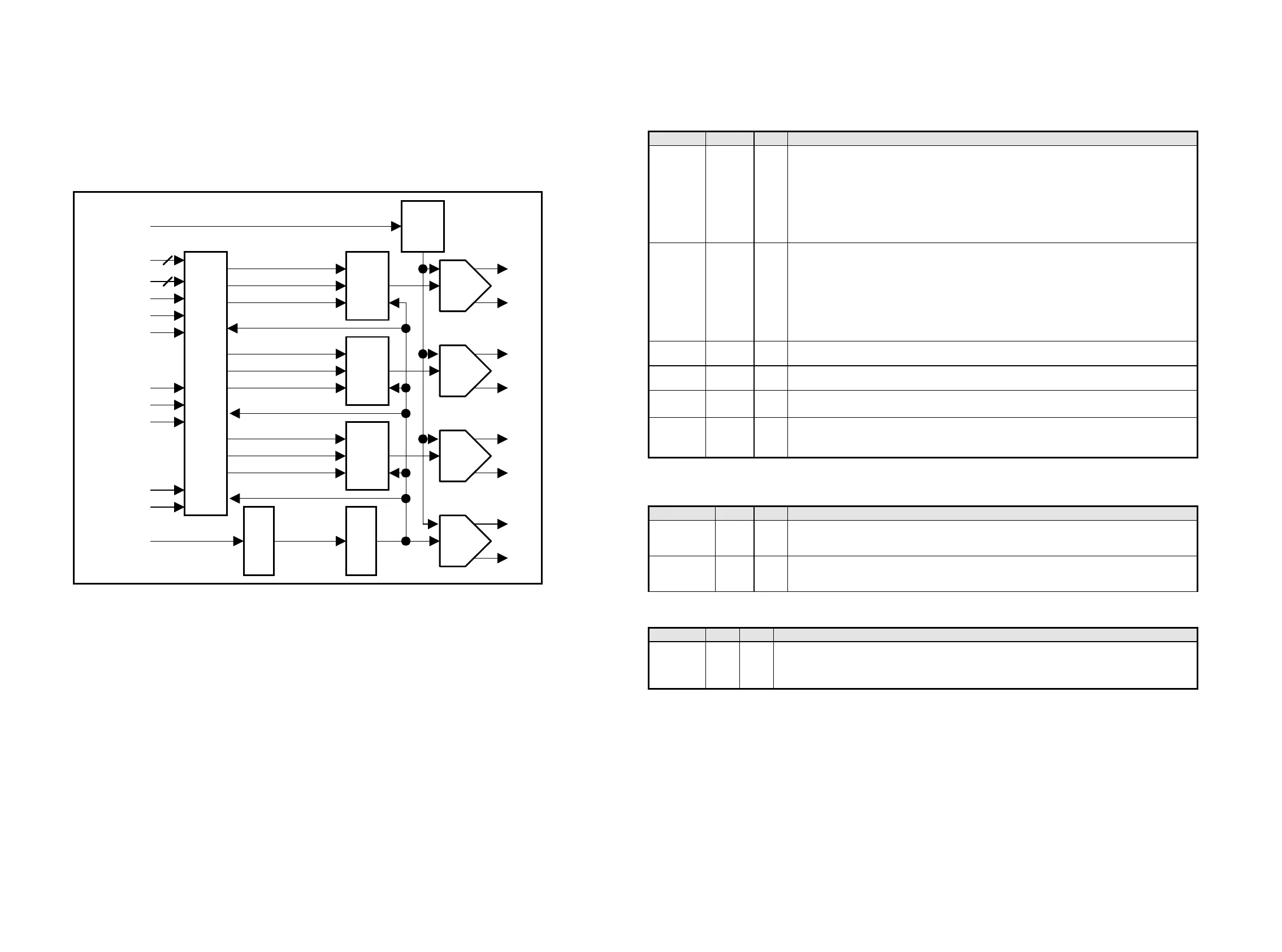

Figure 2. Functional Block Diagram

11. IC DATA

Pin Descriptions

Input Pins

Pin Name Pin # Type Description

DIE23-

DIE0

See

SiI 160

Pin

Diagram

In Input Even Data[23:0] corresponds to 24-bit pixel data for 1-pixel/clock input mode and to the

first 24-bit pixel data for 2-pixels/clock mode.

Input data is synchronized with Input data clock (IDCK).

Data can be latched on the rising of the falling edge of IDCK depending on whether EDGE is

high or low, respectively.

Refer to TFT Panel Data Mapping in this document and DSTN Panel Data Mapping

application note (SiI-AN-0007-A), which tabulates the relationship between the input data to

the transmitter and output data from the Receiver

DIO23-

DIO0

See

SiI 160

Pin

Diagram

In Input Odd Data[23:0] corresponds to the second 24-bit pixel data for 2-pixels/clock mode. Tie

all pins to low when not in use.

Input data is synchronized with Input data clock (IDCK).

Data can be latched on the rising of the falling edge of IDCK depending on whether EDGE is

high or low, respectively

Dual Link is not supported. Refer to TFT Panel Data Mapping in this document and DSTN

Panel Data Mapping application note (SiI-AN-0007-A), which tabulates the relationship

between the input data to the transmitter and output data from the Receiver

IDCK 80 In Input Data Clock. Input data and control signals can be valid either on the falling or the rising

edge of IDCK as selected by the EDGE pin.

DE 78 Out Input Data Enable. This signal qualifies the active data area. DE is always required by the

transmitter and must be high during active display time and low during blanking time.

HSYNC

VSYNC

76

77

In

In

Horizontal Sync input control signal.

Vertical Sync input control signal.

CTL1

CTL2

CTL3

84

83

82

In

In

In

General Input control signal 1.

General Input control signal 2.

General Input control signal 3.

Configuration Pins

Pin Name Pin # Type Description

EDGE 24 In Data/Control Latching Edge. A LOW level indicates that all input signals(DIE/DIO[23:0],

HSYNC, VSYNC, DE and CTL[3:1] are latched on the falling edge of IDCK, while a HIGH

level(3.3V) indicates that all input signals are latched on the rising edge of IDCK.

PIXS 25 In Pixel Select. A LOW level indicates one pixel (up to 24-bits) per clock mode using DIE[23:0].

A HIGH level (3.3V) indicates two pixels (up to 48-bits) per clock mode using DIE[23:0] for

the first pixel and DIO[23:0] for the second pixel.

Power Management Pins

Pin Name Pin # Type Description

PD 26 In Power Down (active LOW). A HIGH level indicates normal operation. A LOW level indicates

power down mode. During power down mode, all data (DIE/DIO[23:0]), data enable (DE), clock

(IDCK) and control signals (HSYNC, VSYNC, CTL[3:1]), input buffers are disabled, all output

buffers are tri-stated and all internal circuitry is powered down.

Loading...

Loading...