dsPIC33/PIC24 Family Reference Manual

DS30009740B-page 4 2010-2013 Microchip Technology Inc.

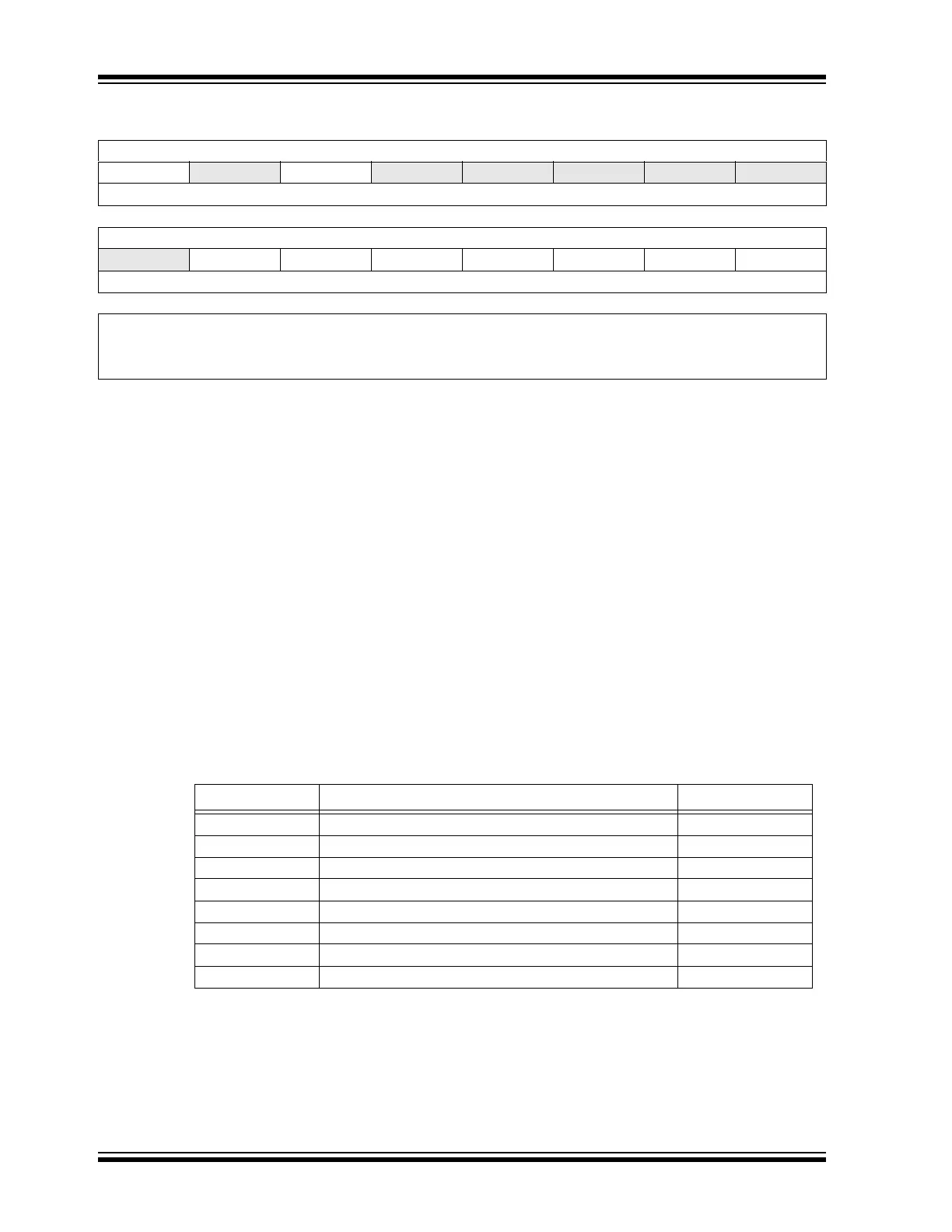

Register 2-1: LCDCON: LCD Control Register

R/W-0 U-0 R/W-0 U-0 U-0 U-0 U-0 U-0

LCDEN

— LCDSIDL — — — — —

bit 15 bit 8

U-0 R/W-0 R/C-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

— SLPEN WERR CS1 CS0 LMUX2 LMUX1 LMUX0

bit 7 bit 0

Legend: C = Clearable bit

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

-n = Value at POR ‘1’ = Bit is set ‘0’ = Bit is cleared x = Bit is unknown

bit 15 LCDEN: LCD Driver Enable bit

1 = LCD driver module is enabled

0 = LCD driver module is disabled

bit 14 Unimplemented: Read as ‘0’

bit 13 LCDSIDL: LCD Stop in CPU Idle Mode Control bit

1 = LCD driver halts in CPU Idle mode

0 = LCD driver continues to operate in CPU Idle mode

bit 12-7 Unimplemented: Read as ‘0’

bit 6 SLPEN: LCD Driver Enable in Sleep Mode bit

1 = LCD driver module is disabled in Sleep mode

0 = LCD driver module is enabled in Sleep mode

bit 5 WERR: LCD Write Failed Error bit

1 = LCDDATAx register is written while WA (LCDPS<4>) = 0 (must be cleared in software)

0 = No LCD write error

bit 4-3 CS<1:0>: Clock Source Select bits

00 =FRC

01 =LPRC

1x =SOSC

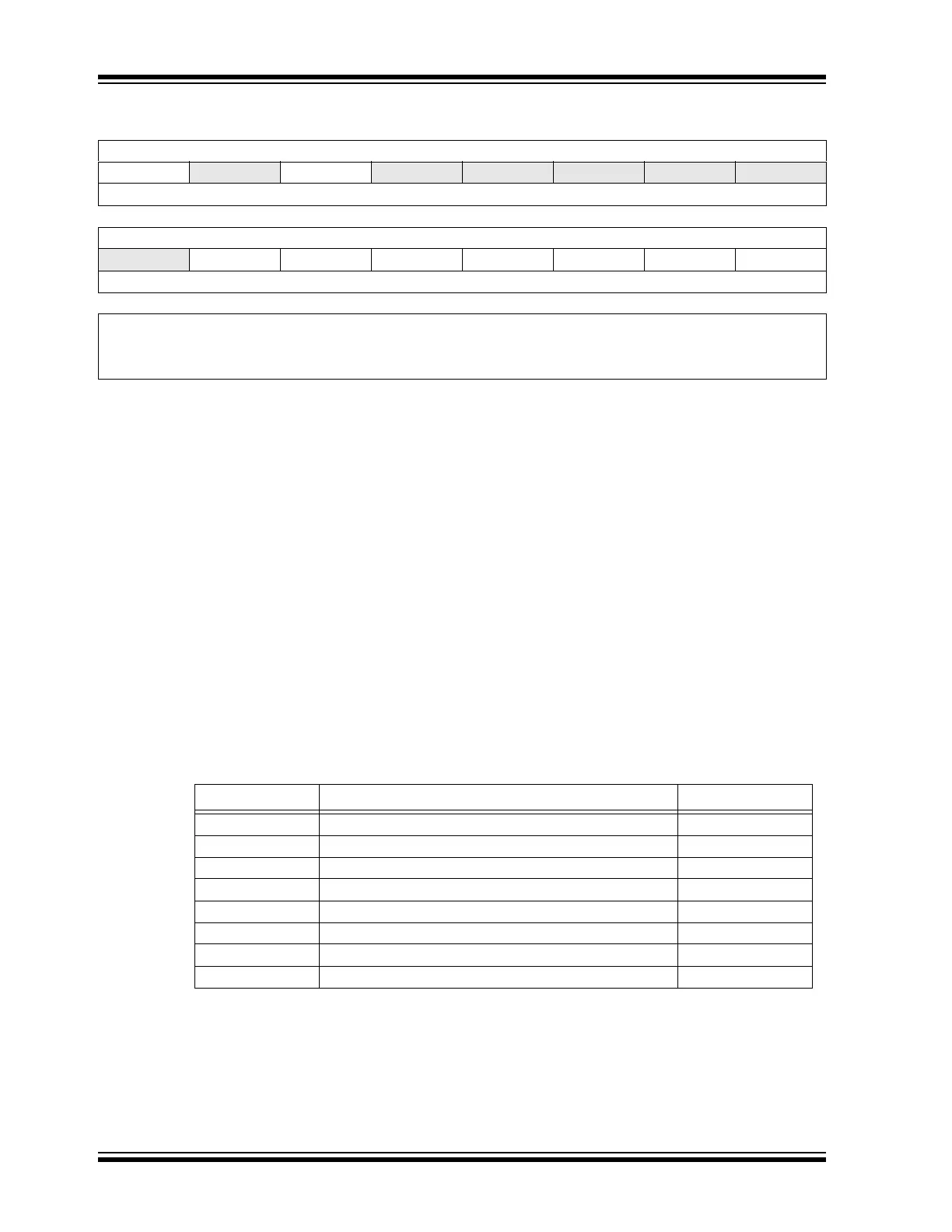

bit 2-0 LMUX<2:0>: LCD Commons Select bits

LMUX<2:0> Multiplex Bias

111 1/8 MUX (COM<7:0>) 1/3

110 1/7 MUX (COM<6:0>) 1/3

101 1/6 MUX (COM<5:0>) 1/3

100 1/5 MUX (COM<4:0>) 1/3

011 1/4 MUX (COM<3:0>) 1/3

010 1/3 MUX (COM<2:0>) 1/2 or 1/3

001 1/2 MUX (COM<1:0>) 1/2 or 1/3

000 Static (COM0) Static

Loading...

Loading...