B-42 | ni.com

Appendix B Timing Diagrams

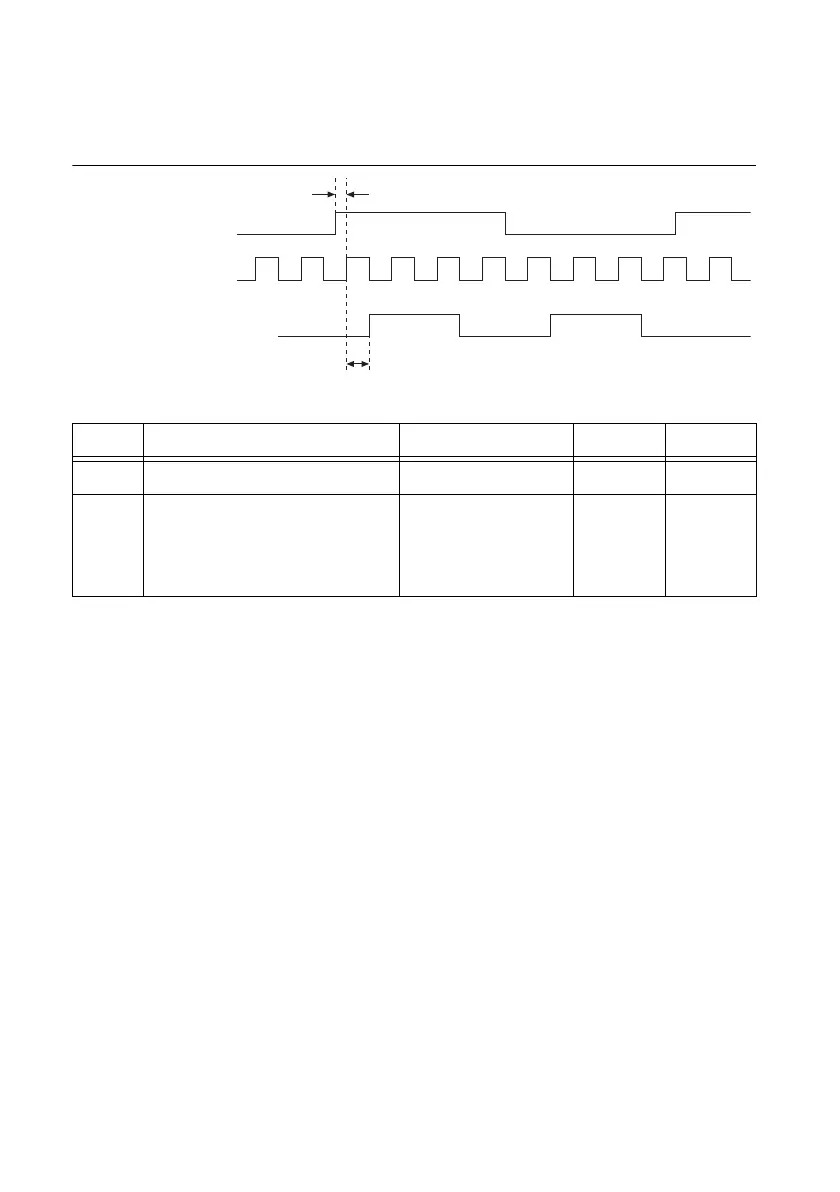

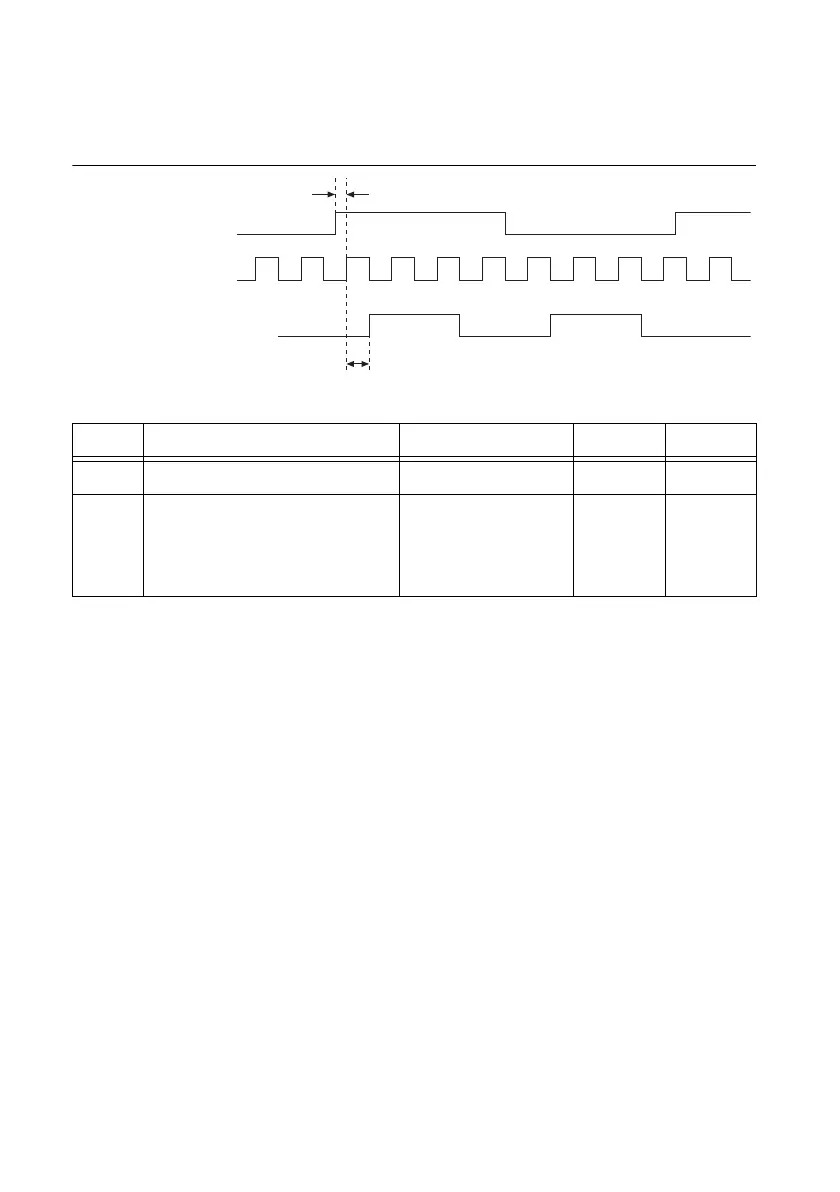

Table B-37 shows delays for generating different clocks using an External Reference Clock and

the PLL.

Figure B-53. Generating Different Clocks Using an External Reference Clock and the PLL

Table B-37. Generating Different Clocks Using an External Reference Clock and the PLL

Time From To Min (ns) Max (ns)

t

4

80 MHz Timebase 20 MHz Timebase 1.5 5.0

t

5

The source of the external

reference clock

(RTSI <0..7>, STAR_TRIG, PX

I_CLK10)

80 MHz Timebase

(through PLL_OUT)

1.0 5.5

RTSI <0..7>

STAR_TRIG

PXI_CLK10

(Reference Clock)

80 MHz Timebase (PLL)

20 MHz Timebase (PLL)

t

4

t

5

Loading...

Loading...