Appendix B Timing Diagrams

M Series User Manual B-8 ni.com

Convert Clock

Convert Clock is the signal that determines when an analog to digital

conversion is started. The signal going to the ADC is called p_AI_Convert.

Convert Clock also can be routed to several external I/O terminals for

external use. Convert Clock is always generated from the Convert Clock

Timebase signal, either directly or indirectly (by dividing it down using the

SI2 counter). If the SI2 counter is used, it is assumed that a reliable

free-running clock is being used. Refer to the AI Timing Clocks section for

the timing relationship between Convert Clock Timebase and Sync Convert

Clock Timebase. If the SI2 counter is not being used (external convert

case), the Convert Clock Timebase is assumed to be not free-running and

the relationship between the Convert Clock Timebase and the Sync Convert

Clock Timebase is an asynchronous delay.

Whether the SI2 counter is used or not, the timing parameters in the

generation of Convert Clock are the same starting at the Convert Clock

Timebase signal.

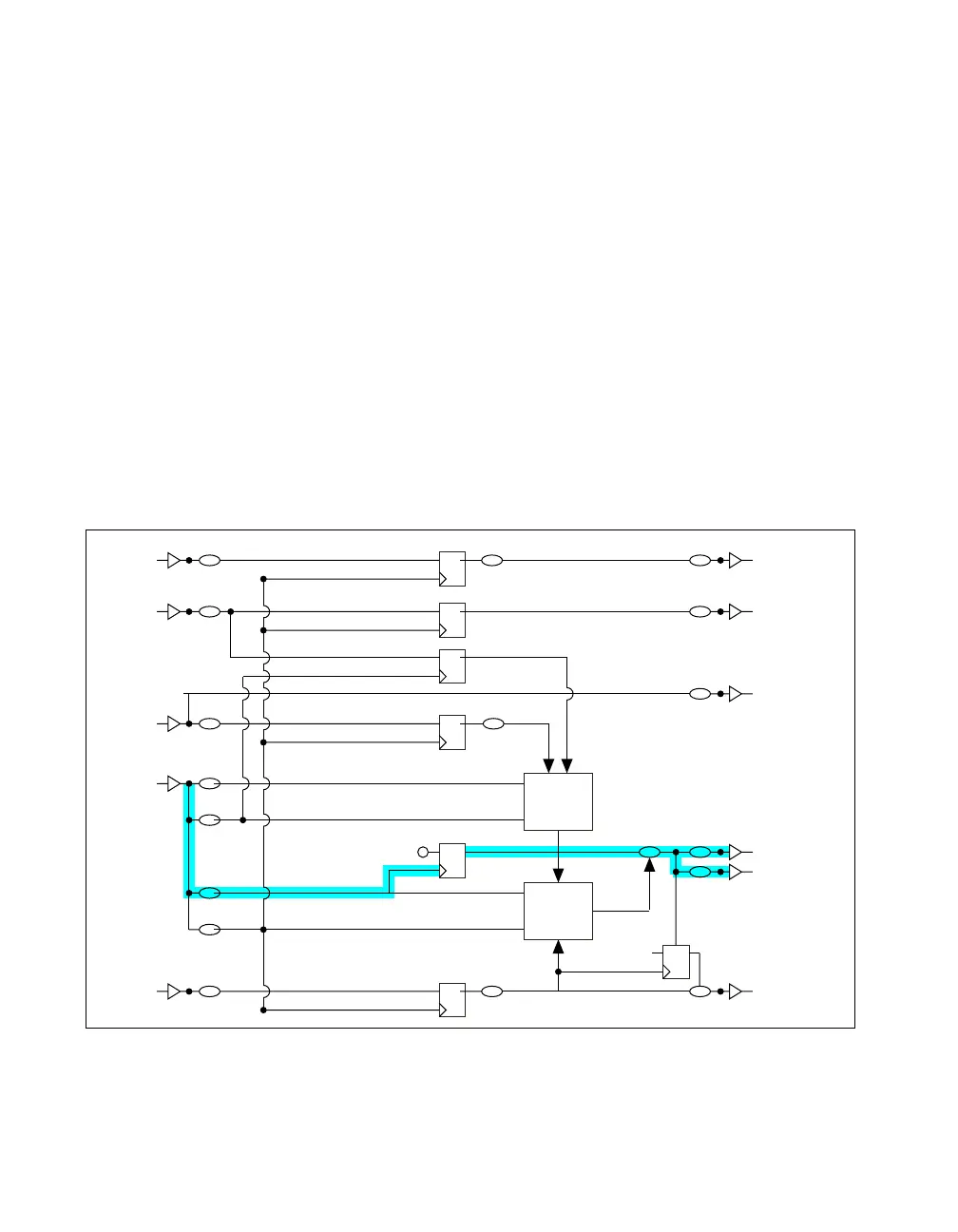

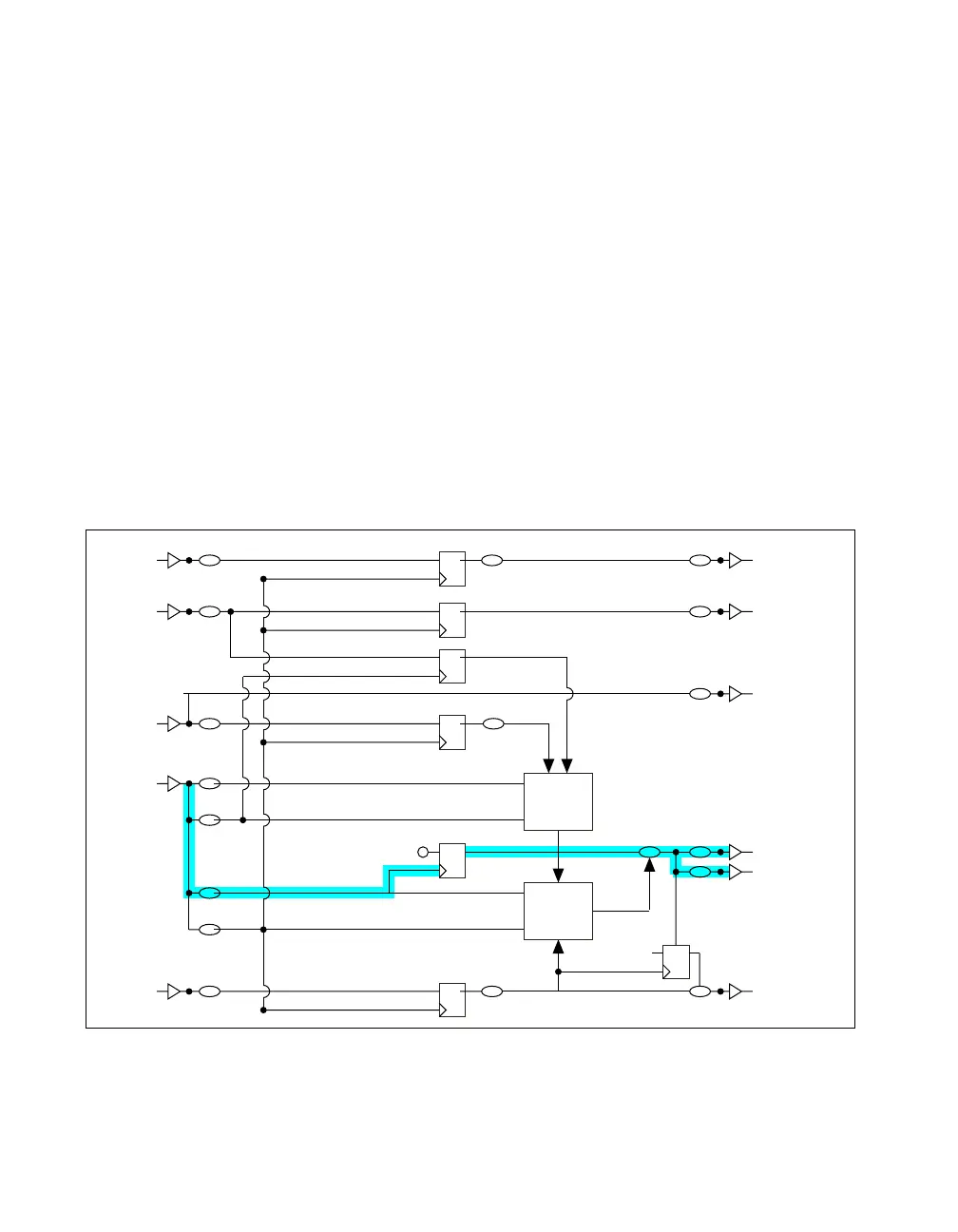

Figure B-6. Convert Clock and the Analog Input Timing Engine

Start

Terminal

Selected Reference Trigger

Reference Trigger

Te r m in al

Terminal

Selected Sample Clock

Te r m in al

Terminal

Te r m in al

Selected Start

RTSI

Te r m in al

Terminal

Terminal

Selected Pause Trigger

SI

Counter

Block

SI2

Counter

Block

SI_TC

Sample Clock Timebase

Sync Sample Clock Timebase

Convert Clock Timebase

Sync Convert Clock Timebase

SI Start

Pause Trigger

p_AI_Convert

Start

1

SI2_TC

Loading...

Loading...