12 | ni.com | NI Digital System Development Board User Manual

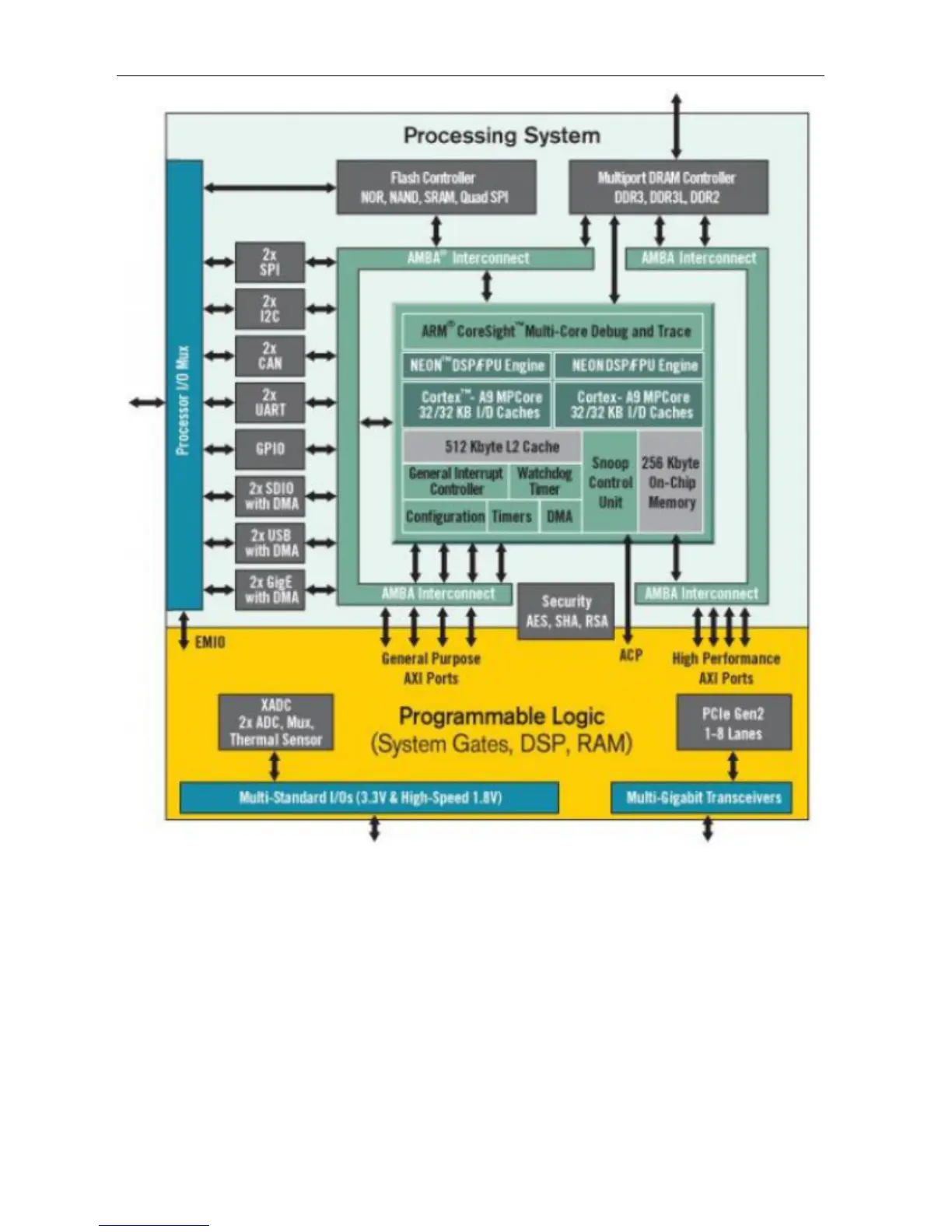

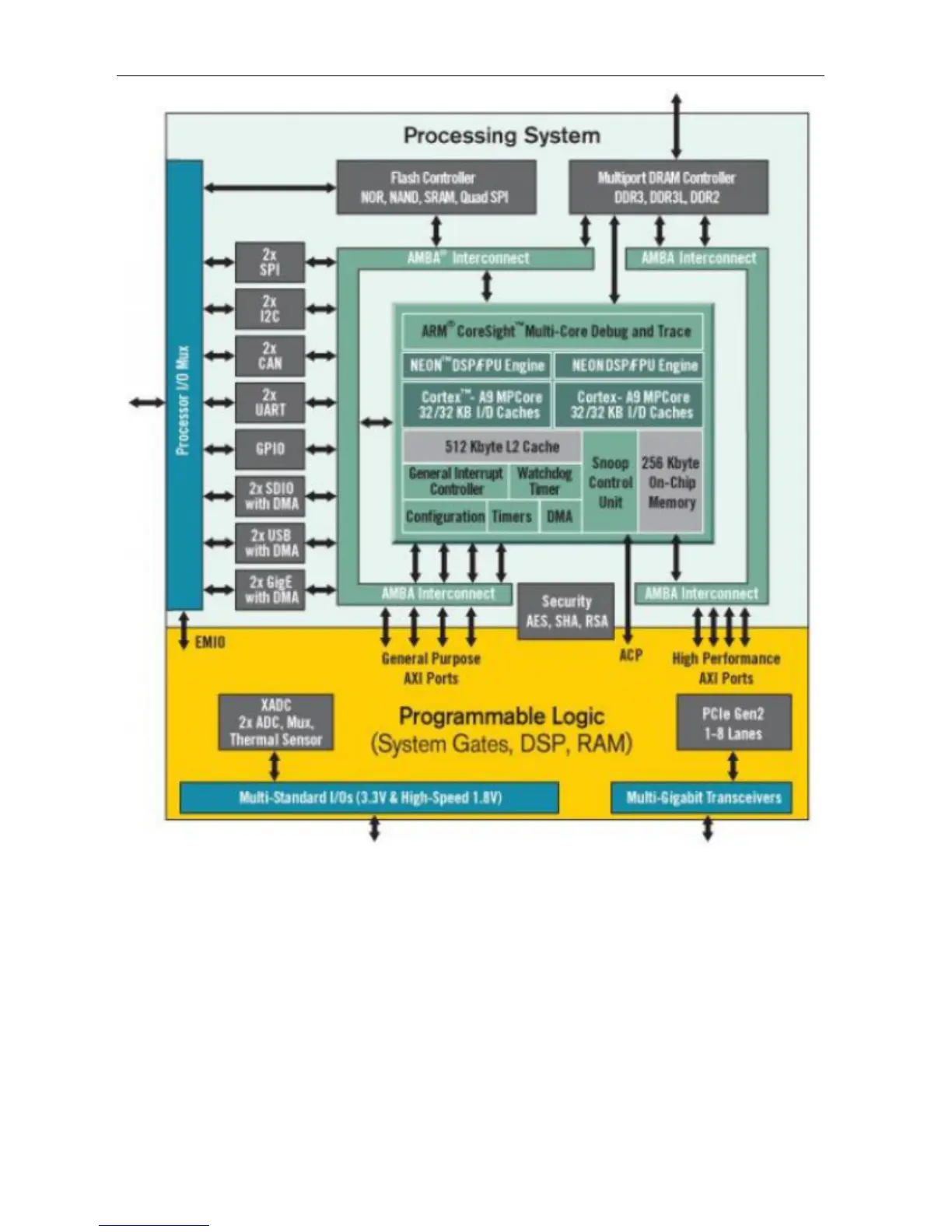

Figure 4. Zynq AP SoC Architecture

The PL is nearly identical to a Xilinx 7-series Artix FPGA, except that it contains several

dedicated ports and buses that tightly couple it to the PS. The PL also does not contain the same

configuration hardware as a typical 7-series FPGA, and it must be configured either directly by

the processor or via the JTAG port.

The PS consists of many components, including the Application Processing Unit (APU, which

includes 2 Cortex-A9 processors), Advanced Microcontroller Bus Architecture (AMBA)

Interconnect, DDR3 Memory controller, and various peripheral controllers with their inputs and

outputs multiplexed to 54 dedicated pins (called Multiplexed I/O, or MIO pins). Peripheral

controllers that do not have their inputs and outputs connected to MIO pins can instead route

their I/O through the PL, via the Extended-MIO (EMIO) interface. The peripheral controllers are

Loading...

Loading...