1 2 3 4 5 6 7 8

A

B

C

D

87654321

D

C

B

A

Excem

12, chemin des Hauts de Clairefontaine

78580 MAULE FRANCE

http://www.excem.fr mailto:info@excem.fr

tel: 01 34 75 13 65 fax: 01 34 75 13 66

tel int: +33134751365 fax int: +33134751366

Client :

Fichier :

Auteur :

Numéro de dessin :

Date :

Feuille : /3 19

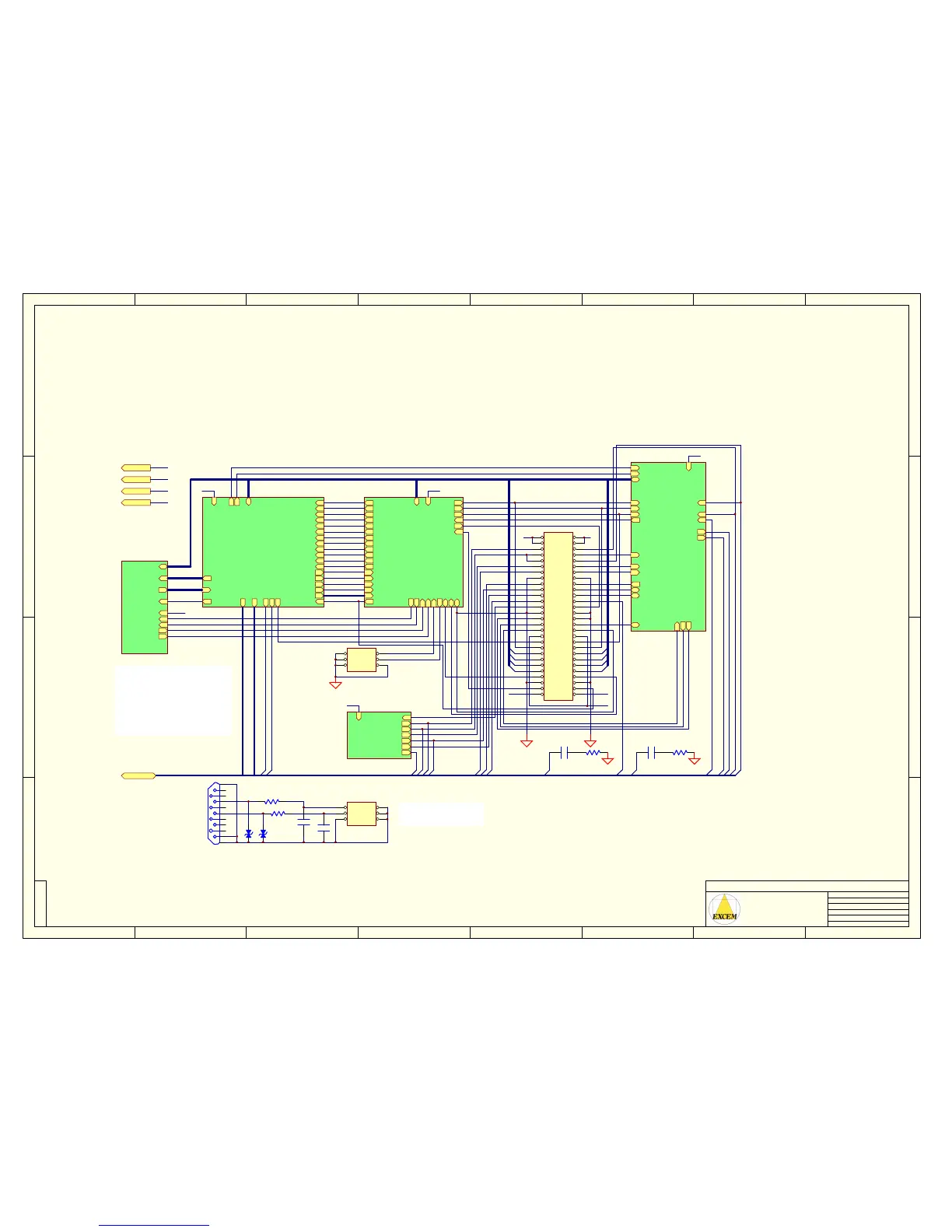

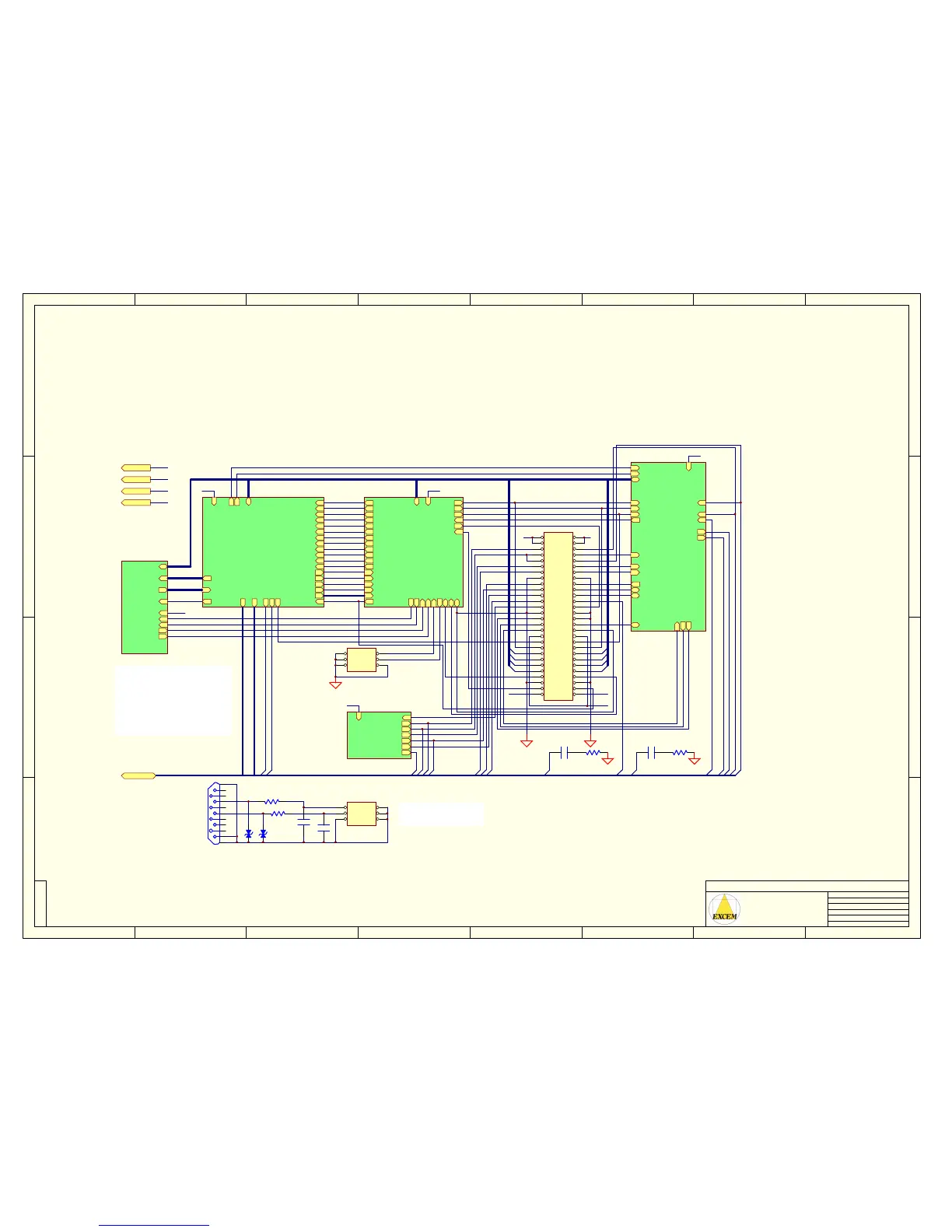

NEXO

NX242rev2_0-S50.Sch

0409230103

6-Oct-2004

Page :

Frédéric Broydé

NX242 TDcontroller (revision 1)

+5VD

AD[0..7]

A12

A13

A14

A15

/RD

/WR

/PSEN

PAGEA0

PAGEA1

PAGEA2

PAGEA3

/CE U5104

/OE U5104

/OE U5105

/CE U5105

ENC1

ENC2

RXD

TXD

MIO1

MIO2

MIO3

HREQ1

HREQ2

MPUCLK

/POWRST

/MRD

/MWR

ALE/P

MuxA[15..18]

LCD_R/W

LCD_D/C

A11

Main CPU

NX242rev2_0-S51.sch

+5VD

AD[0..7]

A12

A13

A14

A15

/RD

/WR

/PSEN

PAGEA0

PAGEA1

PAGEA2

PAGEA3

/CE U5104

/OE U5104

/CE U5105

/OE U5105

LCD_/CS

MuxA[15..18]

/POWRST

/DSP_CS

/EXP_CS

DSP/RST

MUTE

GainI[1..6]

GainO[20..31]

LED[1..18]

SWI[1..7]

A11

CONV/RST

Latches and Chip Select

NX242rev2_0-S52.sch

AD[0..7]

1 2

3 4

5 6

CN5002

1 2

3 4

5 6

7 8

9 10

11 12

13 14

15 16

17 18

19 20

21 22

23 24

25 26

27 28

29 30

31 32

33 34

35 36

37 38

39 40

41 42

43 44

45 46

47 48

49

51

53

55

50

52

54

56

CN5001

H[0..7]

ESSI1_FS

ESSI1_CLK

ESSI1_RD

ESSI1_TD0

ESSI1_SC0

ESSI1_SC1

/MCS

/RST

/MRD

/MWR

ALE/P

HREQ

ESSI0_CLK

ESSI0_FS

ESSI0_RD

ESSI0_TD0

ESSI0_TD1

SCI_TXD

SCI_CLK

SCI_RXD

+3.3V

ESSI0_SC1

DSP Circuits

NX242rev2_0-S53.sch

+5VD

MCLK

SenseSYNC

SCLKx2

SCLK

LRCKx2

LRCK

CLK_MAIN

Converter Clocks

NX242rev2_0-S54.sch

MuxA[15..18]

+5VD+5VD

+3.3V+3.3V

+18V-18V

AD[0..7]

SWI[1..7]

LED[1..18]

LCD_/CS

LCD_D/C

LCD_R/W

+5VD

ENC1

ENC2

Front panel

NX242rev2_0-S55.sch

+3.3V

LED[1..18]

SWI[1..7]

+5VD

DigIO[1..32]

DigIO[1..32]

DigIO[1..6]

DigIO11

DigIO13

DigIO7

DigIO17

+5VD

AD0

AD2

AD4

AD6

AD1

AD3

AD5

AD7

DigIO7

DigIO14

DigIO15

+5VD

DigIO8

DigIO9

DigIO10

DigIO12

DigIO[20..31]

DigIO16

DigIO18

DigIO19

1

6

2

7

3

8

4

9

5

M1

M2

CN5004

SUBD9

C5001

220P

C5002

220P

12

34

56

CN5003

PCB CONNECTOR (3X2)

Auxiliary PCB: the connector CN5003 is

connected by a ribbon cable to the

connector CN5002 of the main PCB.

D5002

SMP100LC-25

D5001

SMP100LC-25

R5001

100

R5002

100

+5VD

+3.3V

+5VD

+3.3V

+18V

+18V

-18V

-18V

C5004

100P

R5004

470

C5003

100P

R5003

470

DigIO7

DigIO13

Note: When the expansion board is not present in CN5001,

fit jumpers between:

- 5 and 6 in order to route LRCK clock to DACs,

- 7 and 8 in order to route sense bit clock to main DSP,

- 9 and 10 in order to route SCLK clock to DACs,

- 11 and 12 in order to route sense word clock to the main

DSP,

- 13 and 14 in order to route sense data to main DSP,

- 23 and 24 in order to hold DigIO32 low,

- 25 and 26 in order to route MPUCLK (of the main CPU)

to CLK_MAIN.

DigIO32

Loading...

Loading...