User Manual For CYCLONE FX Programmers 12

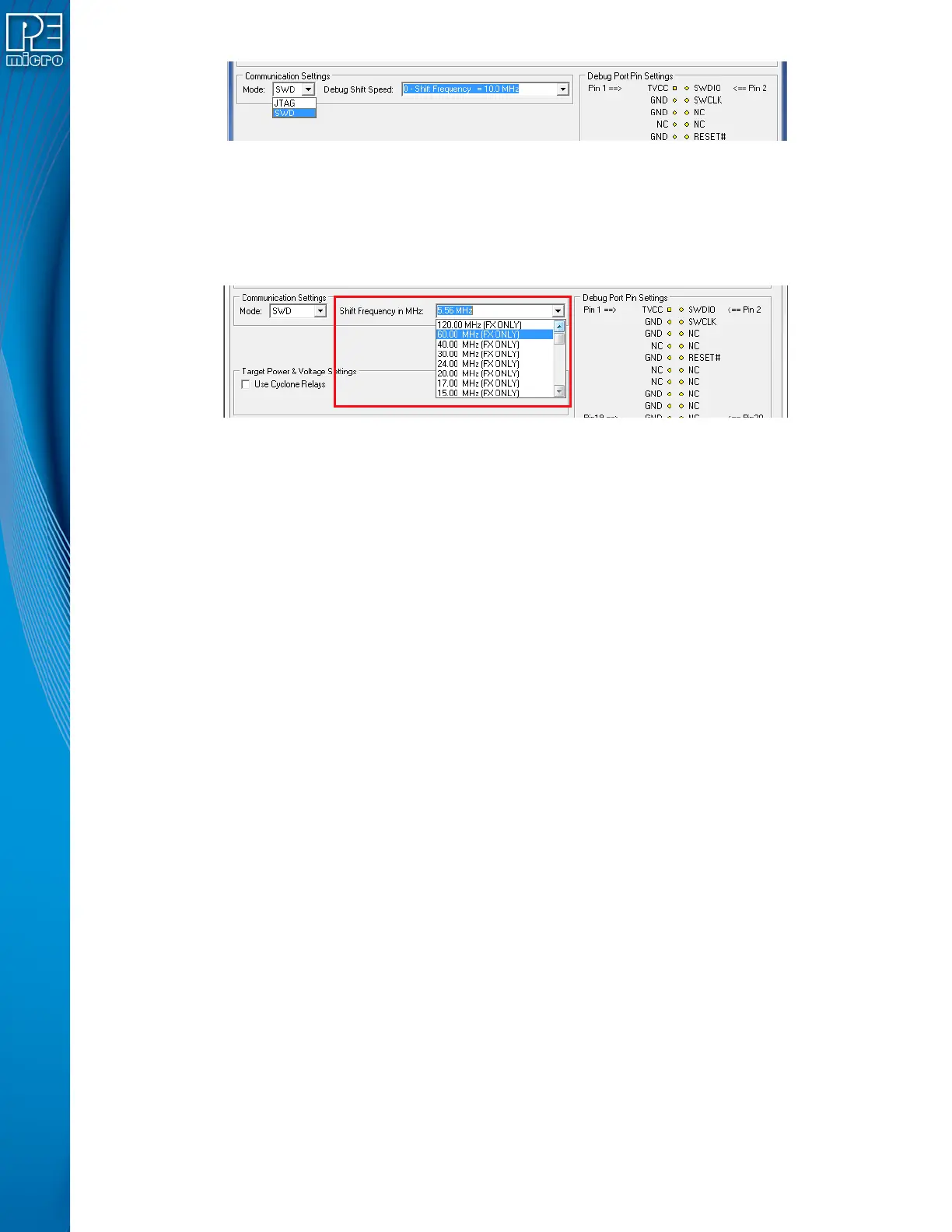

Figure 3-10: Communications Mode Selection

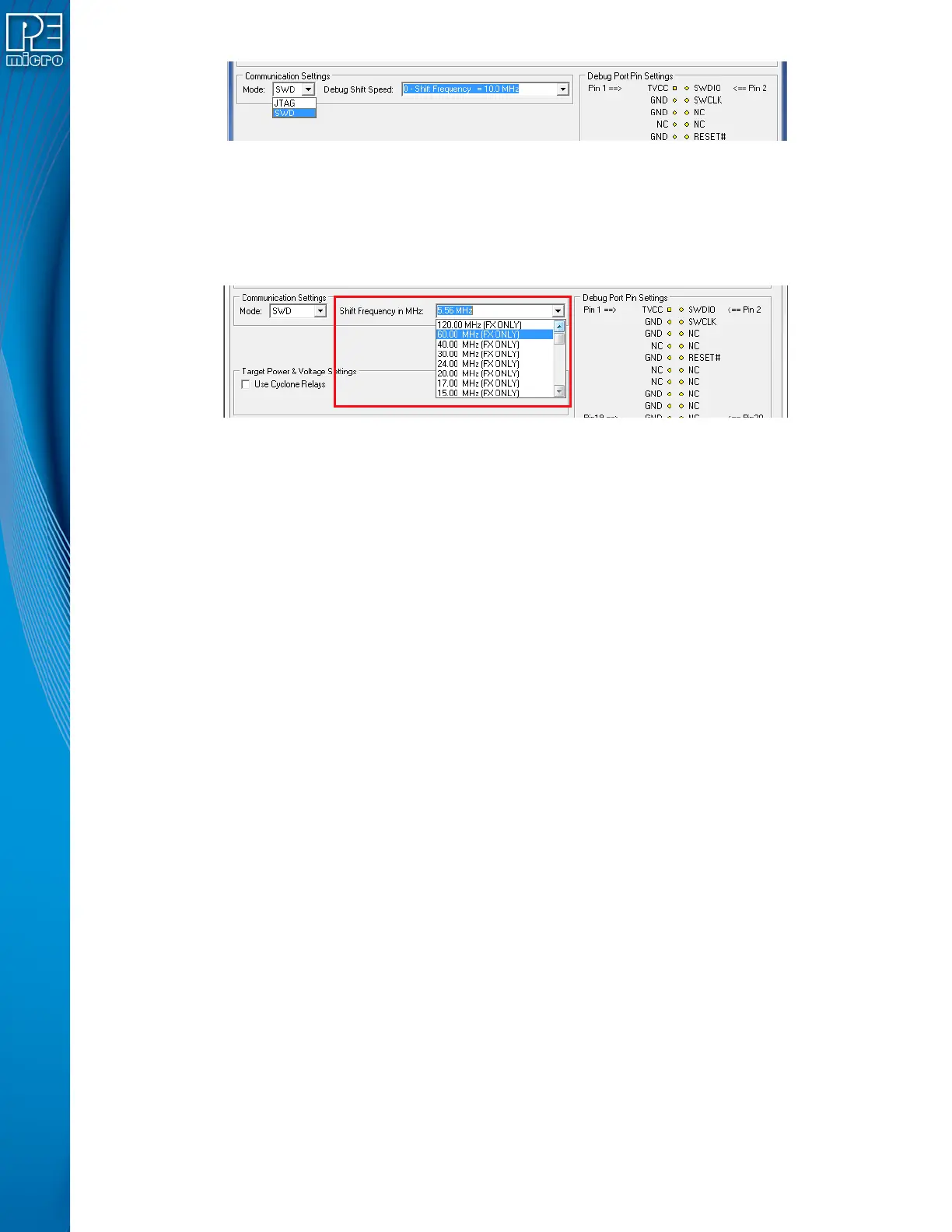

3.18.2.2.1 High-Performance Communications

If high-performance options are available for the selected device they will appear in the “Shift

Frequency in M Hz” drop-down. CYCLONE FX programmers are capable of high-performance

communications when using certain ARM Cortex targets in SWD mode.

Figure 3-11: High-Performance Options

3.18.3 PORT C: 20-Pin Debug Connector (Kinetis, S32 (ARM), other PEmicro-Supported ARM

devices)

3.18.3.1 JTAG Mode Pin Assignments

The Cyclone provides a 20-pin 0.100-inch pitch double row connector for ARM targets. The

location of the this header is indicated as PORT C under Part# CYCLONE_ACP_FX in Figure 3-5.

The 20-pin standard connector pin definitions for JTAG mode are as follows:

20-Pin Standard Connector JTAG Mode Pin Assignments

PIN 1 - TVCC NC* - PIN 2

PIN 3 - TRST or NC GND - PIN 4

PIN 5 - TDI GND - PIN 6

PIN 7 - TMS GND - PIN 8

PIN 9 - TCK GND - PIN 10

PIN 11 - NC* GND - PIN 12

PIN 13 - TDO GND - PIN 14

PIN 15 - RESET GND - PIN 16

PIN 17 - NC* GND - PIN 18

PIN 19 - NC* GND - PIN 20

Note: *The pin is reserved for internal use within the PEmicro interface.

3.18.3.2 SWD Mode Pin Assignments

CYCLONE FX programmers also support SWD Mode. This replaces the JTAG connection with a

clock and single bi-directional data pin.

20-Pin Standard Connector SWD Mode Pin Assignments

PIN 1 - TVCC NC* - PIN 2

PIN 3 - TRST or NC* GND - PIN 4

PIN 5 - NC* GND - PIN 6

PIN 7 - TMS/SWDIO GND - PIN 8

PIN 9 - TCK/SWCLK GND - PIN 10

PIN 11 - NC* GND - PIN 12

PIN 13 - NC* GND - PIN 14

PIN 15 - RESET GND - PIN 16

Loading...

Loading...