RL78/G13 Handshake-based SPI Master Transmission/Reception

R01AN6883EJ0100 Rev.1.00 Page 29 of 38

June.15.23

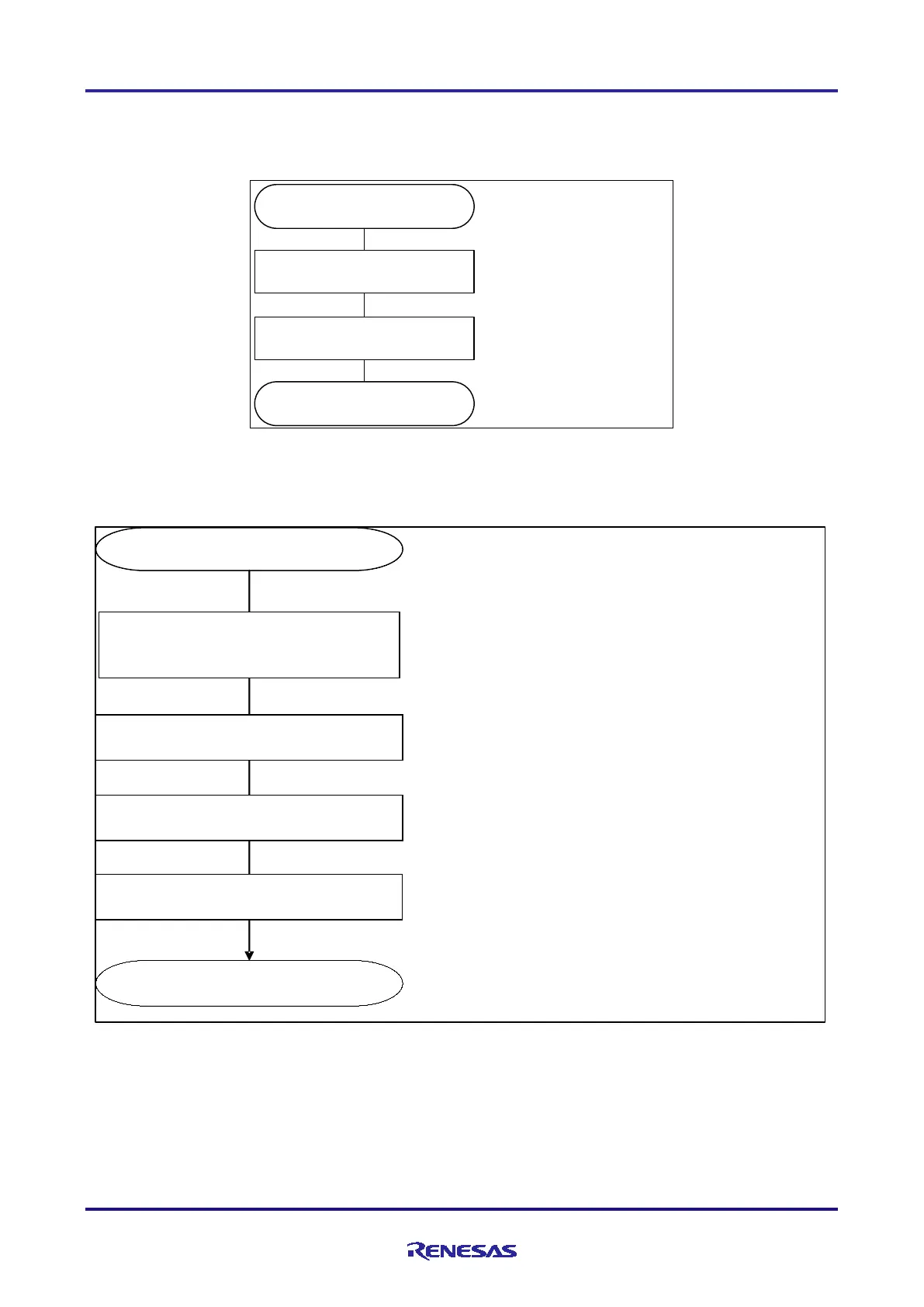

5.6.10 TAU0 channel 3 upper 8 bits start operation

Figure 5-11 shows the flow of TAU0 channel 3 upper 8 bits start operation.

Figure 5-11 TAU0 channel 3 upper 8 bits start operation

R_TAU0_Channel3_Higher8bits_Start

INTTM03H Interrupt permission

TMIF03H bit← 0

TMMK03H bit← 0

return

TAU0 channel 3 upper 8 bits start

TS0 register ←0800H

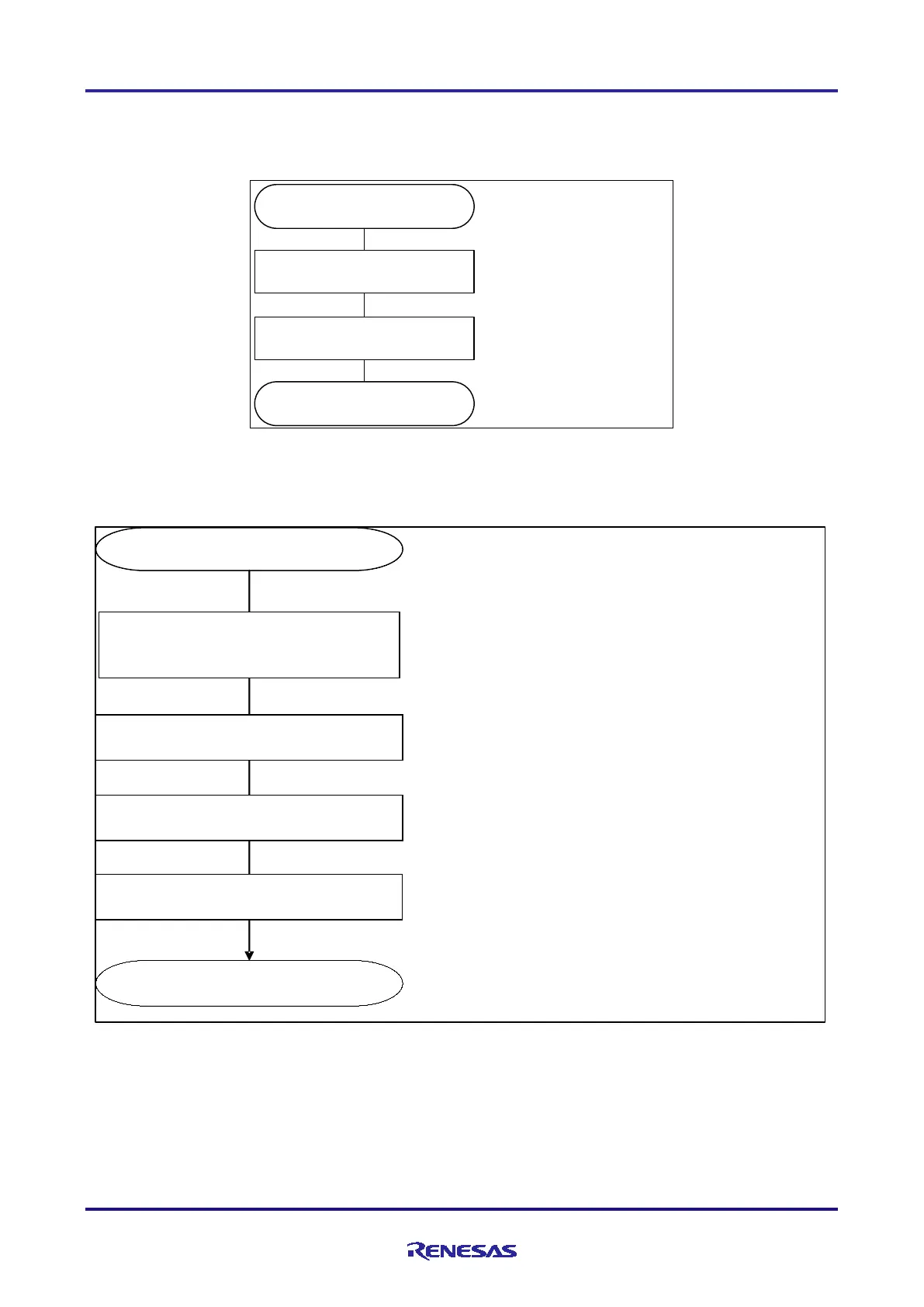

5.6.11 CSI00 start operation

Figure 5-12 shows the flow of CSI00 start operation.

Figure 5-12 CSI00 start operation

CSIIF00 bit ← 0: Clears interrupt request flag.

CSIMK00 bit

← 0: Enables CSI00 interrupt processing.

Initial value of SCK00 pin: High level

Initial value of SO00 pin: Low level

Loading...

Loading...