Chapter 1 Programming Overview RIGOL

DL3000 Programming Guide 1-7

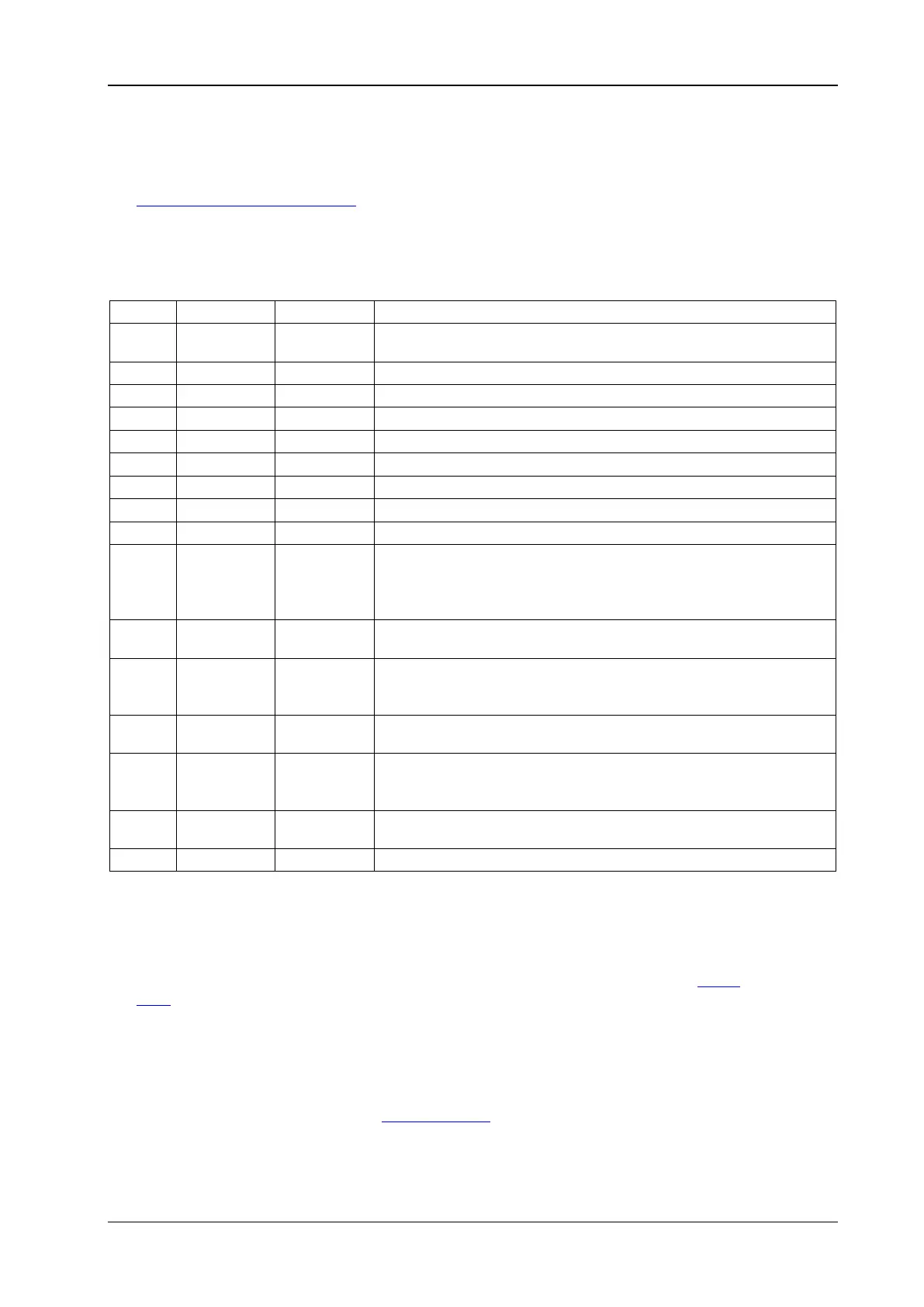

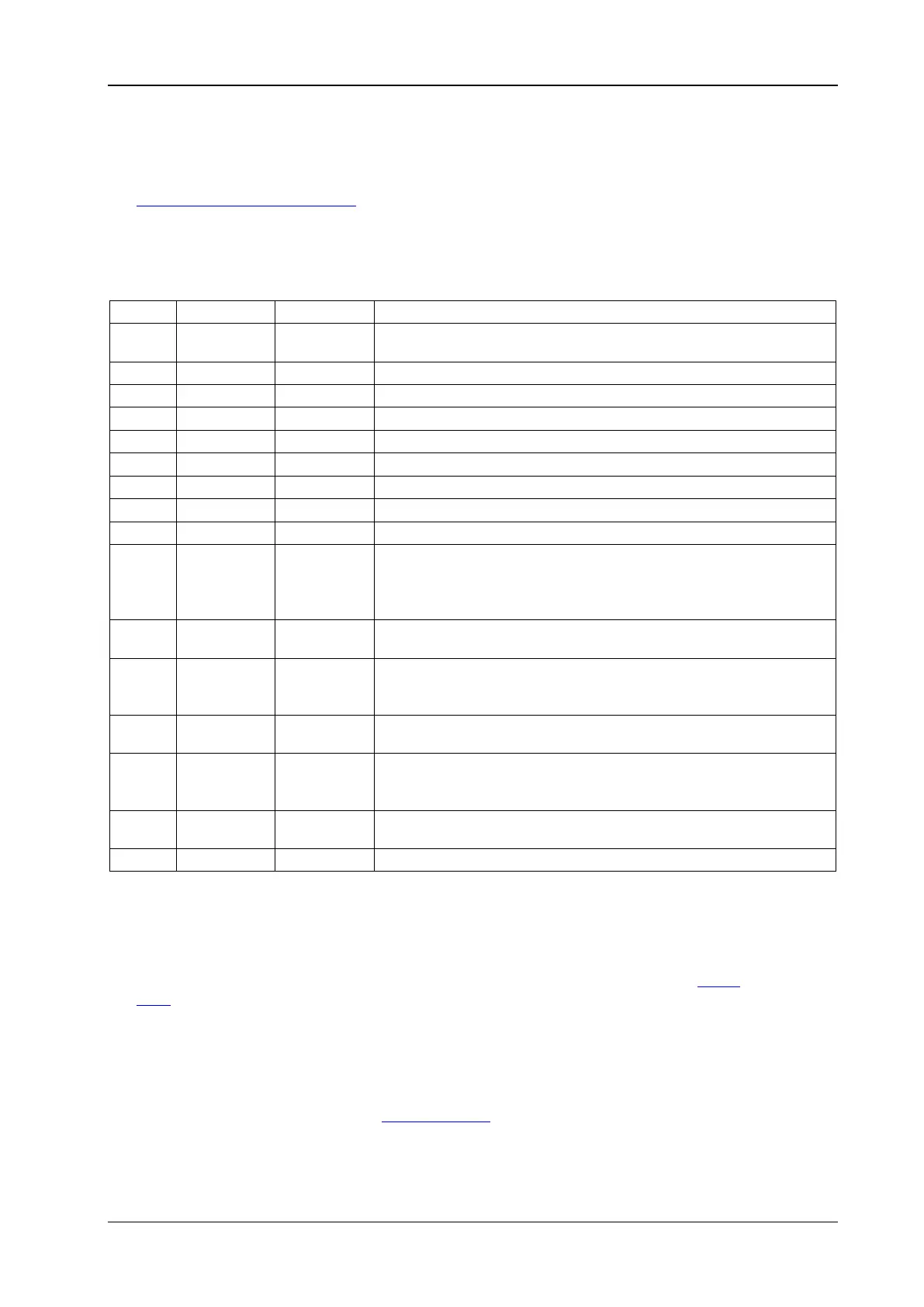

Questionable Status Register

The SCPI status system of the DL3000 is shown in Figure 1-2. The questionable status register monitors the

overall instrument condition, such as voltage/current control, OTP, OVP, OCP, and fan failure. You can send

the

:STATus:QUEStionable[:EVENt]? command to read the register. The definitions for the bits in the

questionable status register and the decimal value that corresponds to the binary-weighted value are

shown in Table 1-1.

Table 1-1 Definitions for the bits in the questionable status register and the decimal value that corresponds

to the binary-weighted value

0 1 VF

Voltage fault. Overvoltage and reverse voltage occurred; the OV

or the RV condition is removed.

Remote Sense terminal connection

3 8 OP Overpower occurred.

4 Not used Not used This bit is always set to 0.

This bit is always set to 0.

6 Not used Not used This bit is always set to 0.

7 128 RUN Runs in List mode

This bit is always set to 0.

9 512 RRV

Remote Reverse Voltage. When reverse voltage occurs to the

remote terminals, the bit and VF bit are set. When the reverse

voltage is removed, the RRV bit is cleared, but the VF bit will not

10 1024 UNR

Unregulated. The input is unregulated. When the input has been

regulated, the bit is cleared.

11 2048 LRV

Local Reverse Voltage. When reverse voltage occurs to the input

terminals, the bit and VF bit are set. When the reverse voltage is

removed, the LRV bit is cleared, but the VF bit will not be cleared.

12 4096 OV

Overvoltage. When OV occurs, the OV bit and VF bit are set, and

the load is turned off.

13 8192 PS

Protection Shutdown. When overcurrent, overpower, or

overtemperature occurred, the load's input is turned off

(protection shutdown).

14 16384 VON

Voltage of sink current on. When the input voltage exceeds the

set Von value, the load starts to sink the current.

This bit is always set to 0.

Event Register

The event register latches events from the condition register. Once the bit in the event register is set to 1,

the subsequent event changes are ignored. The event register is read-only. Once the bit is set to 1, it will

remain set and will not be cleared until cleared by running a query command (e.g. the

*ESR? command) or

the

*CLS command. When you send a query command to query the event register, a decimal value

(equivalent to the binary-weighted sum of all bits enabled in the register) will be returned.

Enable Register

The enable register is both readable and writable. It defines whether to report the events in the event

register to the status byte register. The

:STATus:PRESet command will clear all bits in the enable register,

and the *PSC 1 command will make all bits in the enabled register cleared once the instrument is powered

on. To enable the events in the event register to be reported to the status byte register, write a decimal

value (equivalent to the binary-weighted sum of all bits enabled in the register) into the enable register.

Loading...

Loading...