SYSTEM CONTROLLER S3C2416X RISC MICROPROCESSOR

2-34

8.5 CONTROL OF RETENTION PAD(I/O) WHEN NORMAL MODE AND WAKE-UP FROM SLEEP MODE.

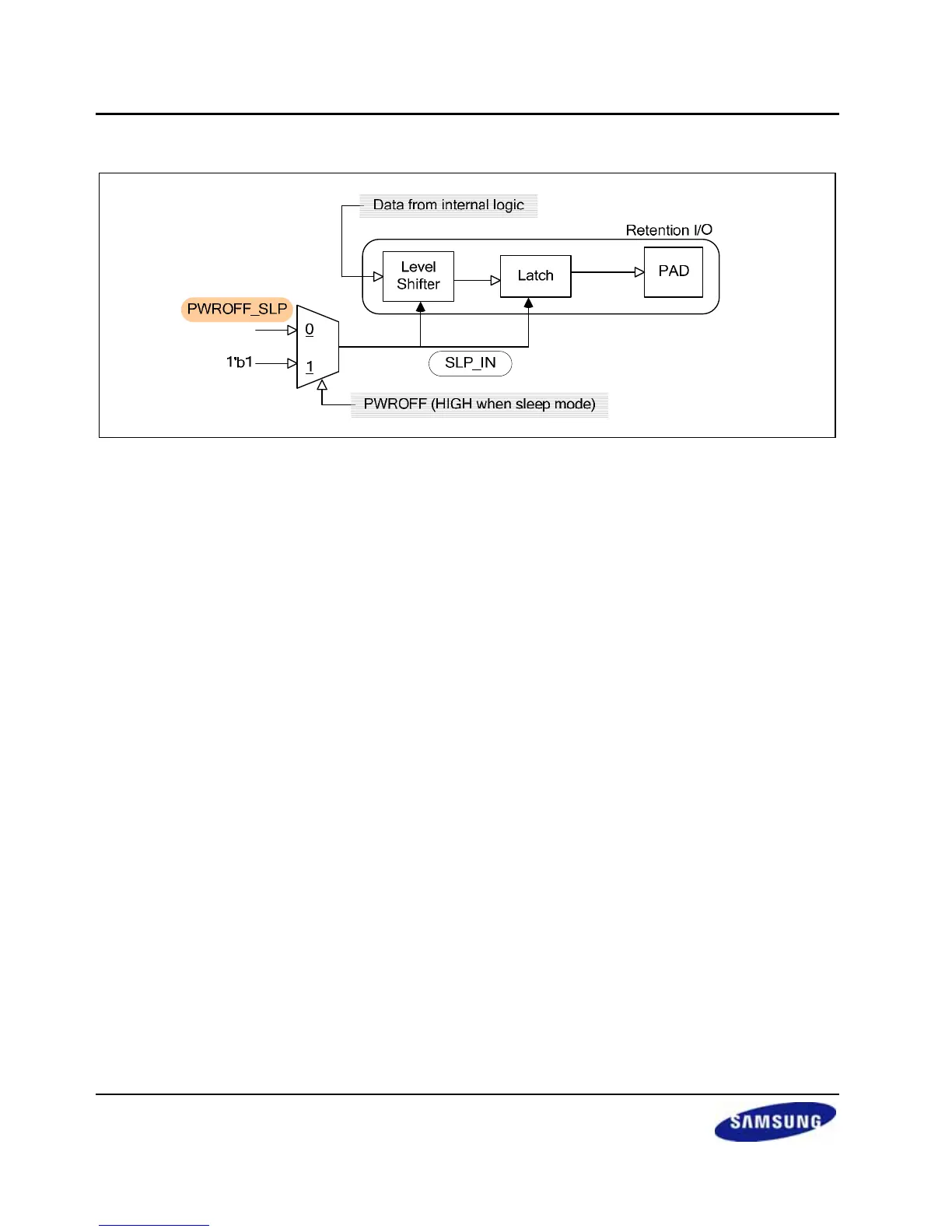

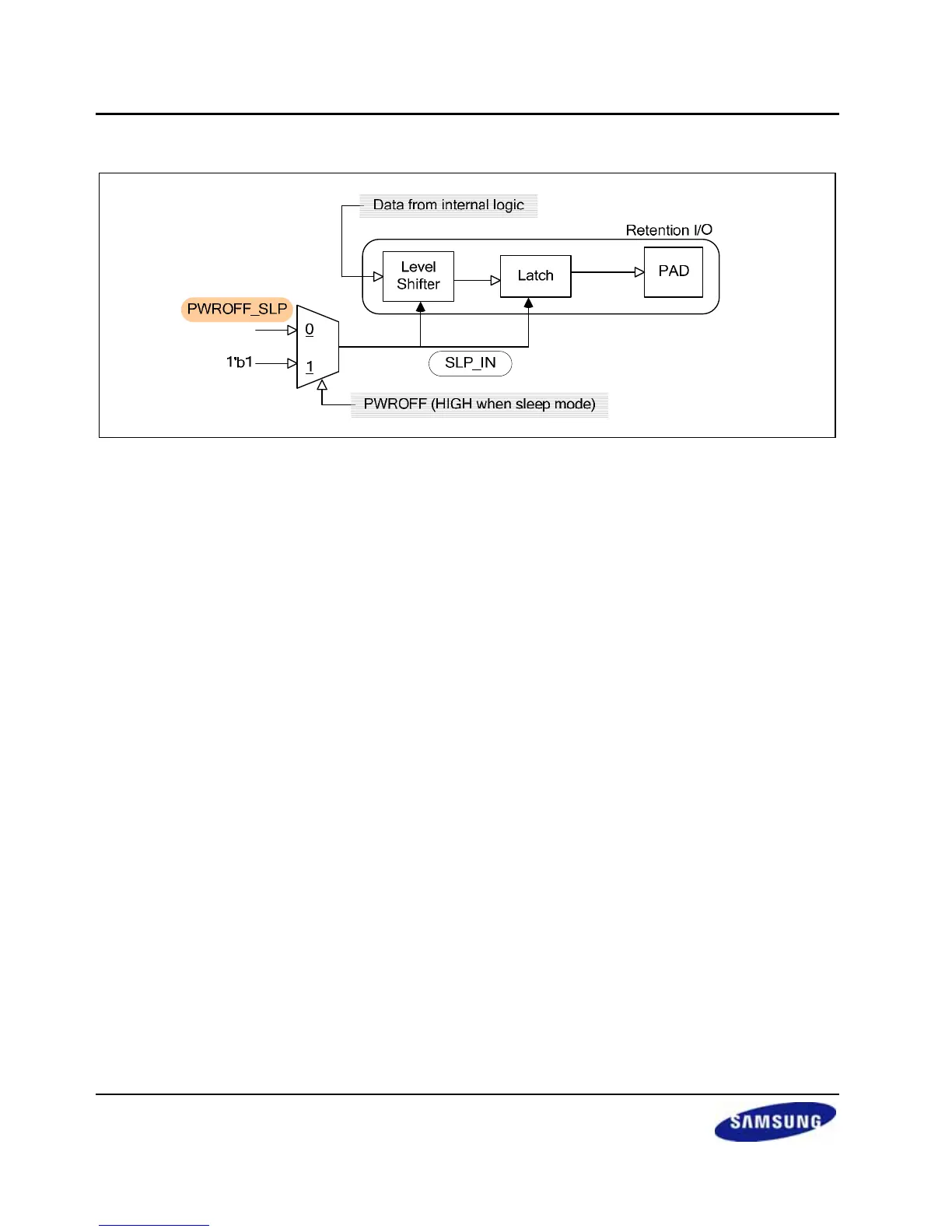

Figure 2-13. Usage of PWROFF_SLP

S3C2416 has a lot of retention PADs. Retention pad’s ability is remaining data when internal logic power is off. In

normal mode, PWROFF_SLP signal which from RSTCON register can control about PAD output. If SLP_IN signal

has LOW value, data assigned to specific PAD go out through level shifter and latch. Otherwise If SLP_IN signal

has HIGH value, output of level shifter cannot pass therefore retention PAD produces latched data only.

When the system enters into a sleep mode, SLP_IN value has HIGH value as a result of PWROFF’s HIGH state.

Futhermore, PWROFF_SLP register bit is automatically set to 1’b1.

When the system wakeup from sleep mode, SLP_IN still remains HIGH state until user configure PWROFF_SLP

bit as 1’b0. Therfore, user has to configure PWROFF_SLP bit to produce internal logic data through PAD after

waking up from sleep mode.

Pin lists that are not affected by PWROFF_SLP

OM[4:0], EINT[15:0], AIN[9:0],

Vref, DM_UDEV, DP_UDEV, REXT, X0_UDEV, X1_UDEV,

nTRST, TMS, TCK, TDI, TDO,

XTOpll, XTIpll, EPLLCAP,

XTRrtc, XTOrtc, nRESET, nRSTOUT, PWREN, BATT_FLT, EXTCLK,

GPF, GPG[7:0]

Loading...

Loading...