HT-DV40H

8 – 18

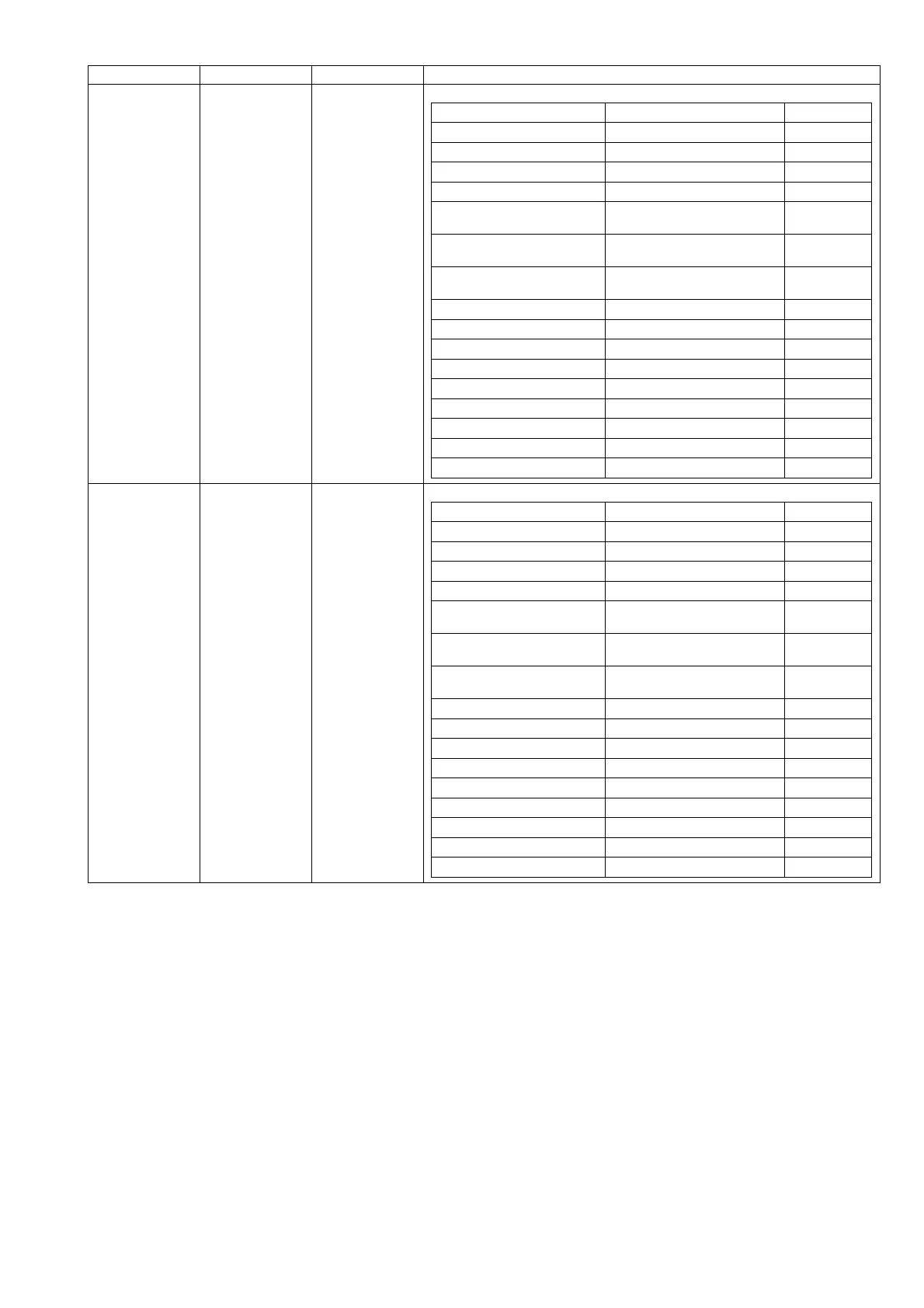

GPIO/M_DD[20] 167 Input/Output GPIO[43] or SDRAM data bus bit 20

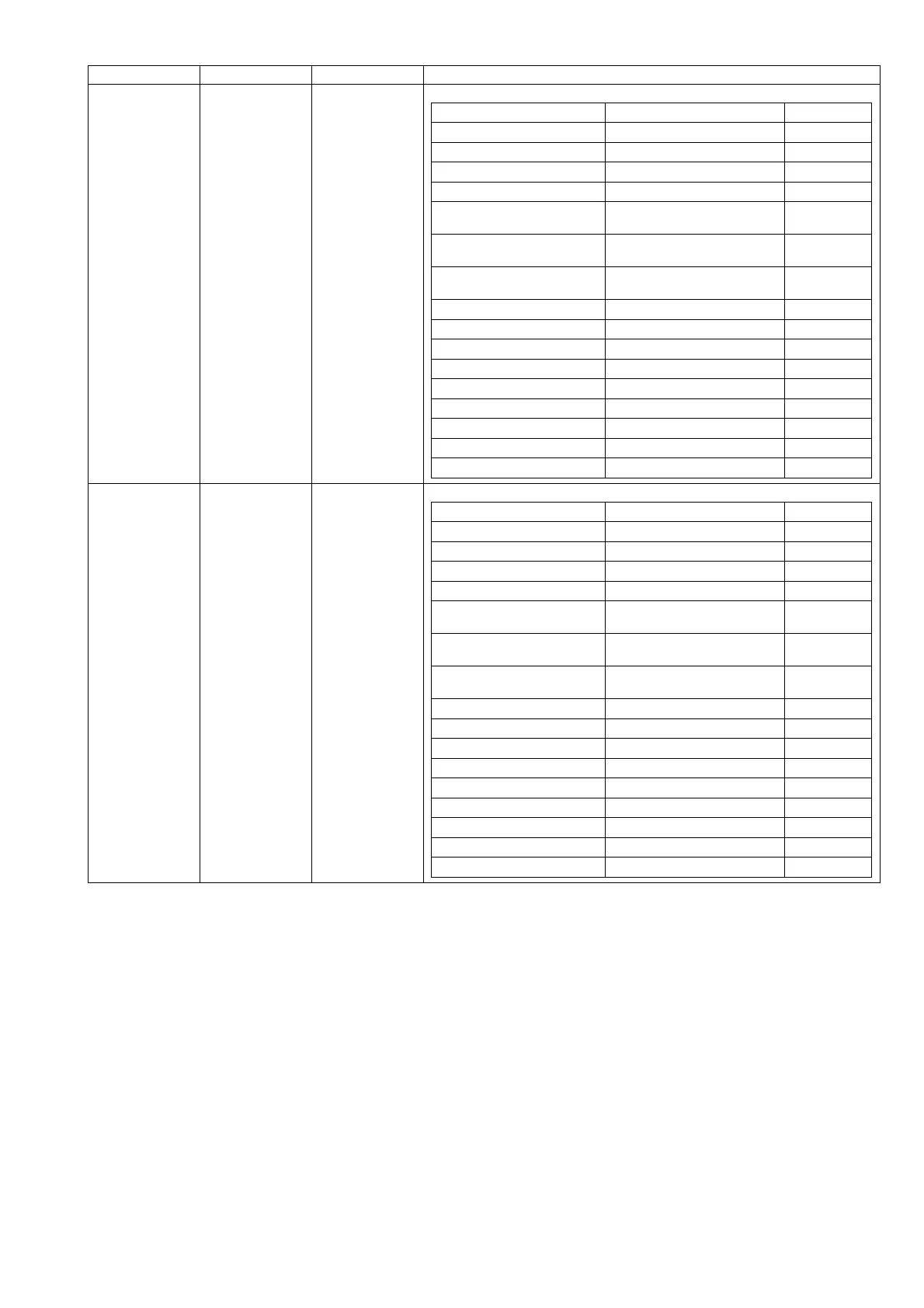

GPIO/M_DD[19] 168 Input/Output GPIO[44] or SDRAM data bus bit 19

Symbol Pin # Input/Output Description

Priority selection Function Dir

hw_cfg_chg[5]=1’b1 SDRAM data bus [20] Input/Output

gpio_first[2][11] = 1 GPIO[43] Input/Output

sft_cfg13[14:12] = 3'b001 AT_D[5] Input/Output

sft_cfg13[14:12] = 3'b100 AT_D[5] Input/Output

{sft_cfg20[0],sft_cfg7[5:4]} =

3'b001

656_DATA[3] Output

{sft_cfg20[1],sft_cfg19[5:4]} =

3'b001

HD_DATA[3] Output

{sft_cfg20[2],sft_cfg14[7:6]} =

3'b001

SRGB_DATA[3] Output

sft_cfg11[5:3] = 3'b100 EXT_TS_CLK Input

sft_cfg0[13:12] = 1 TV_LCD_B[1] Output

sfg_cfg15[11:9] = 3'b100 FM_GPIOB[6] Input/Output

sfg_cfg16[15:12] = 4'b0001 FM_GPIOB[14] Input/Output

sfg_cfg16[15:12] = 4'b0101

FM_GPIOB[15] Input/Output

sfg_cfg17[3:0] = 4'b0110 FM_GPIOB[17] Input/Output

sfg_cfg18[3:0] = 4'b1000 FM_GPIOB[39] Input/Output

sfg_cfg18[3:0] = 4'b1001 FM_GPIOB[37] Input/Output

(other) GPIO[43] (default) Input/Output

Priority selection Function Dir

hw_cfg_chg[5]=1’b1 SDRAM data bus [19] Input/Output

gpio_first[2][12] = 1 GPIO[44] Input/Output

sft_cfg13[14:12] = 3'b001 AT_D[9] Input/Output

sft_cfg13[14:12] = 3'b100 AT_D[10] Input/Output

{sft_cfg20[0],sft_cfg7[5:4]} =

3'b001

656_DATA[4] Output

{sft_cfg20[1],sft_cfg19[5:4]} =

3'b001

HD_DATA[4] Output

{sft_cfg20[2],sft_cfg14[7:6]}=

3'b001

SRGB_DATA[4] Output

sft_cfg11[5:3] = 3'b100 TS_DATA[0] Input/Output

sft_cfg0[13:12] = 1 TV_LCD_B[2] Output

sfg_cfg16[7:4] = 4'b0100 FM_GPIOB[9] Input/Output

sfg_cfg16[15:12] = 4'b0001 FM_GPIOB[13] Input/Output

sfg_cfg16[15:12] = 4'b0101 FM_GPIOB[16] Input/Output

sfg_cfg16[15:12] = 4'b0110 FM_GPIOB[16] Input/Output

sfg_cfg18[3:0] = 4'b1000 FM_GPIOB[38] Input/Output

sfg_cfg18[3:0] = 4'b1001 FM_GPIOB[38] Input/Output

(other) GPIO[44] (default) Input/Output

Loading...

Loading...