HT-DV40H

8 – 37

IC10 VHINJU26220FN : DOLBY VIRTUAL SPEAKER / HEADPHONE DECODER ( NJU26220FN ) ( 3/3 )

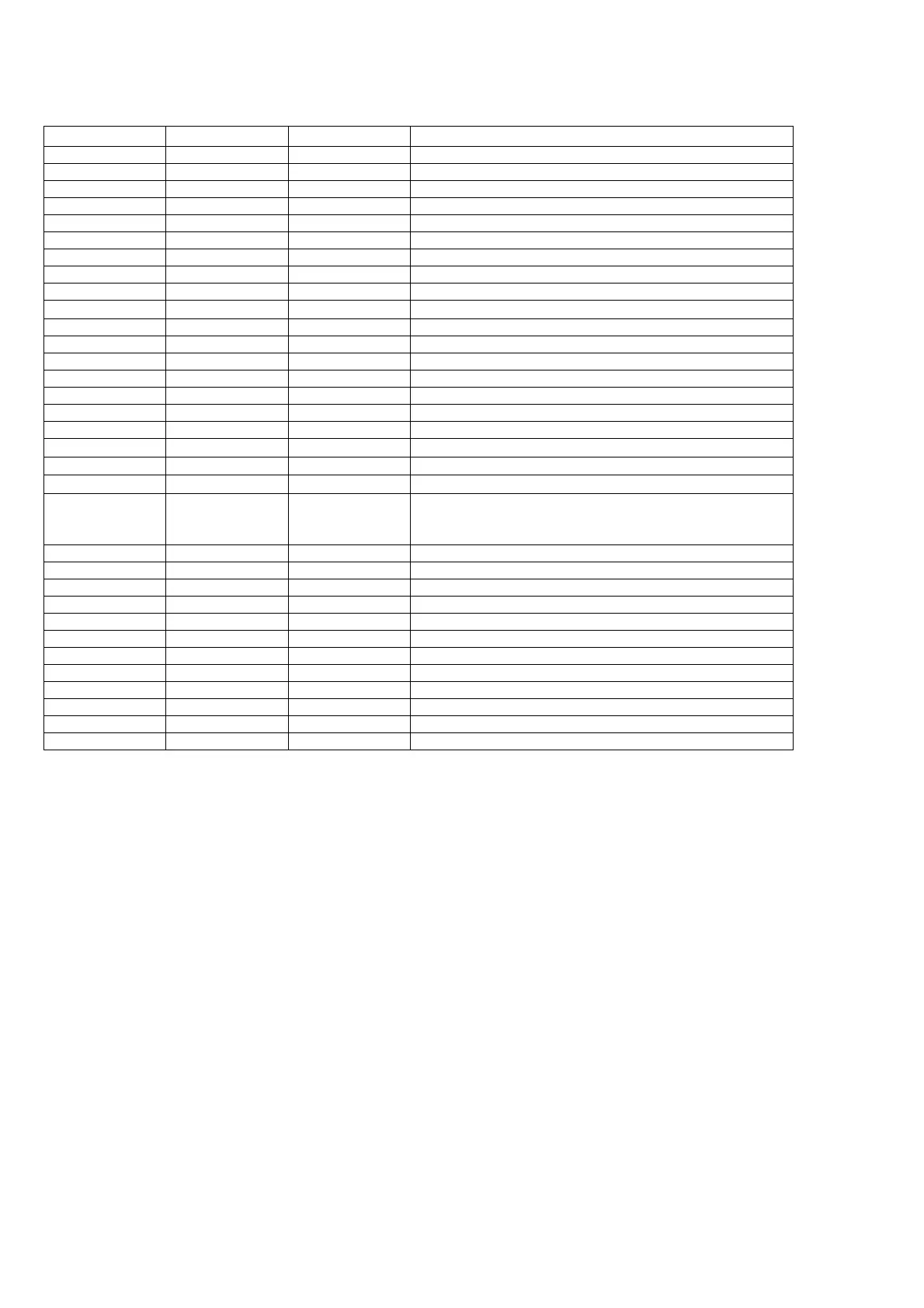

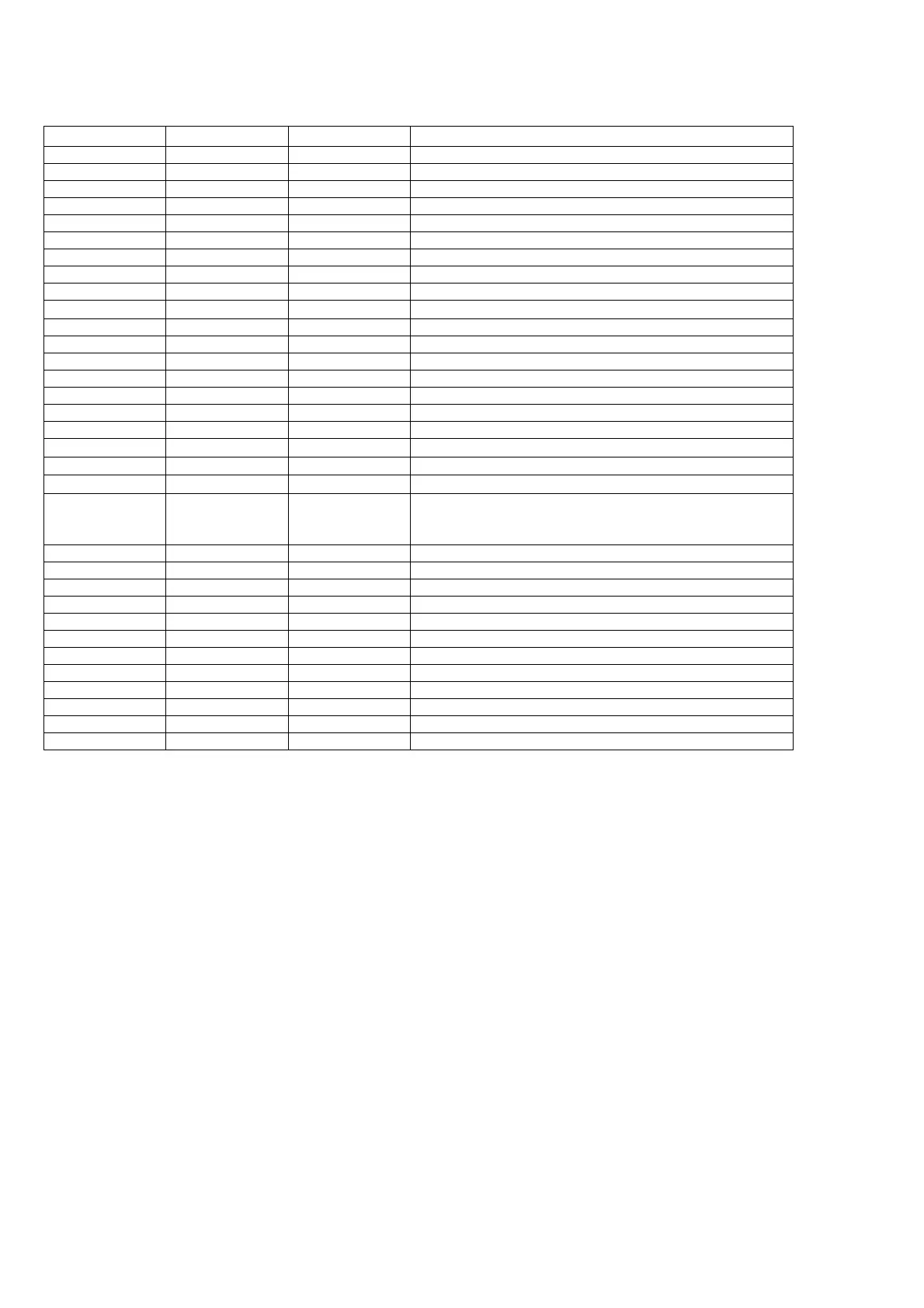

PIN DESCRIPTION

Pin No. Symbol Input/Output Function

1,11,20,32,40 VDDIO - I/O Power Supply +3.3V

2BCKI Input Bit Clock Input

3,10,19,31,41 VSSIO - I/O GND

4,15,30,42 VSS - Core GND

5,16,29,43 VDD - Core Power Supply +1.8V

6 TEST Input for test (connected to VSSIO through 3.3kΩ resistance.)

7MUTEb* Input Master Volume level, After reset DSP (“1” : 0dB, “0” : Mute)

8 WDC* OD Clock for Watch Dog Timer (Open Drain Output)

9 PROC* Input After Reset DSP. (“1” : Normal, “0” : Wait from Command)

12 SEL Input

Select I

2

C or Serial Bus (“1” : Serial, “0” : I

2

C-Bus)

13 VDDPLL - PLL Analog Power Supply +1.8V

14 VSSPLL - PLL Analog GND

17 CLKOUT Output OSC Output

18 CLK Input X’tal CLock Input (12.288MHz)

21 RESETb Input Reset (RESETb=’0’ : DSP Reset)

22 TEST Input for TEST (Connect to VDDIO)

23,24 TEST Input for TEST (Connect to VSSIO)

25 AD1/SDIN Input

I

2

C Address / Serial Input

26 AD2/SSb Input

I

2

C Address / Serial Enable

27 SCI/SCK Input

I

2

C Clock / Serial Clock

28 SDA/SDOUT Input/Output

I

2

C I/O (Open Drain output) / Serial Output (CMOS output)

I

2

C Bus mode : SDA pin requires a pull-up resistance

4-wire Serial mode : SDOUT does not require a pull-up resistance.

33 MCK Output Master Clock Output (CLK Terminal=27 pin Buffer Out)

34 BCKO Output Bit Clock Output

35 LRO Output LR Clock Output

36 SDO3 Output Audio Data Output 3 (SL/SR)

37 SDO2 Output Audio Data Output 2 (C/SW)

38 SDO1 Output Audio Data Output 1 (L/R)

39 SDO0 Output Audio Data Output 0 (Monitor output)

44 SDI3 Input Audio Data Input 3

45 SDI2 Input Audio Data Input 2

46 SDI1 Input Audio Data Input 1

47 SDI0 Input Audio Data Input 0

48 LRI Input LR Clock Input

Loading...

Loading...