HT-DV40H

8 – 3

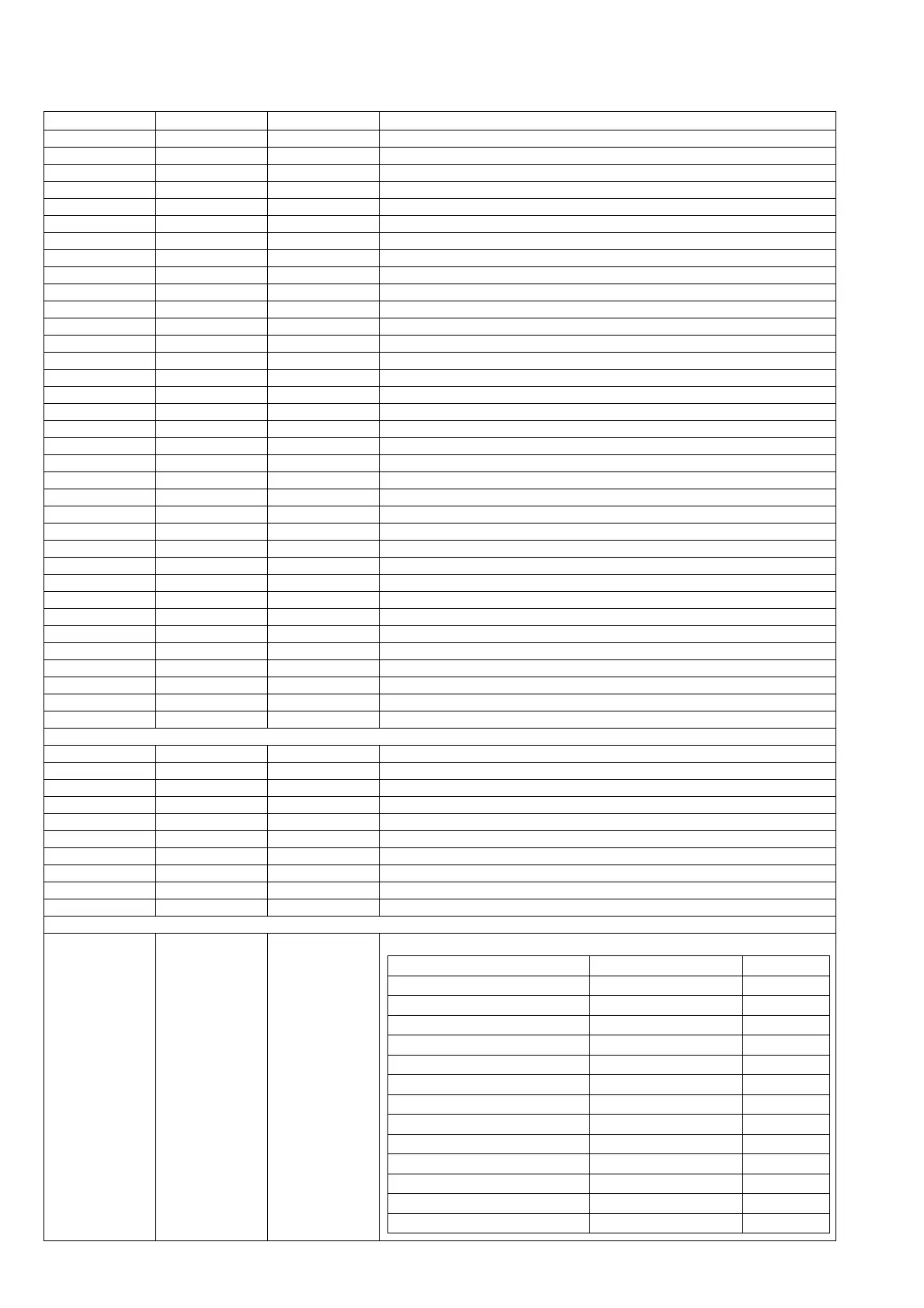

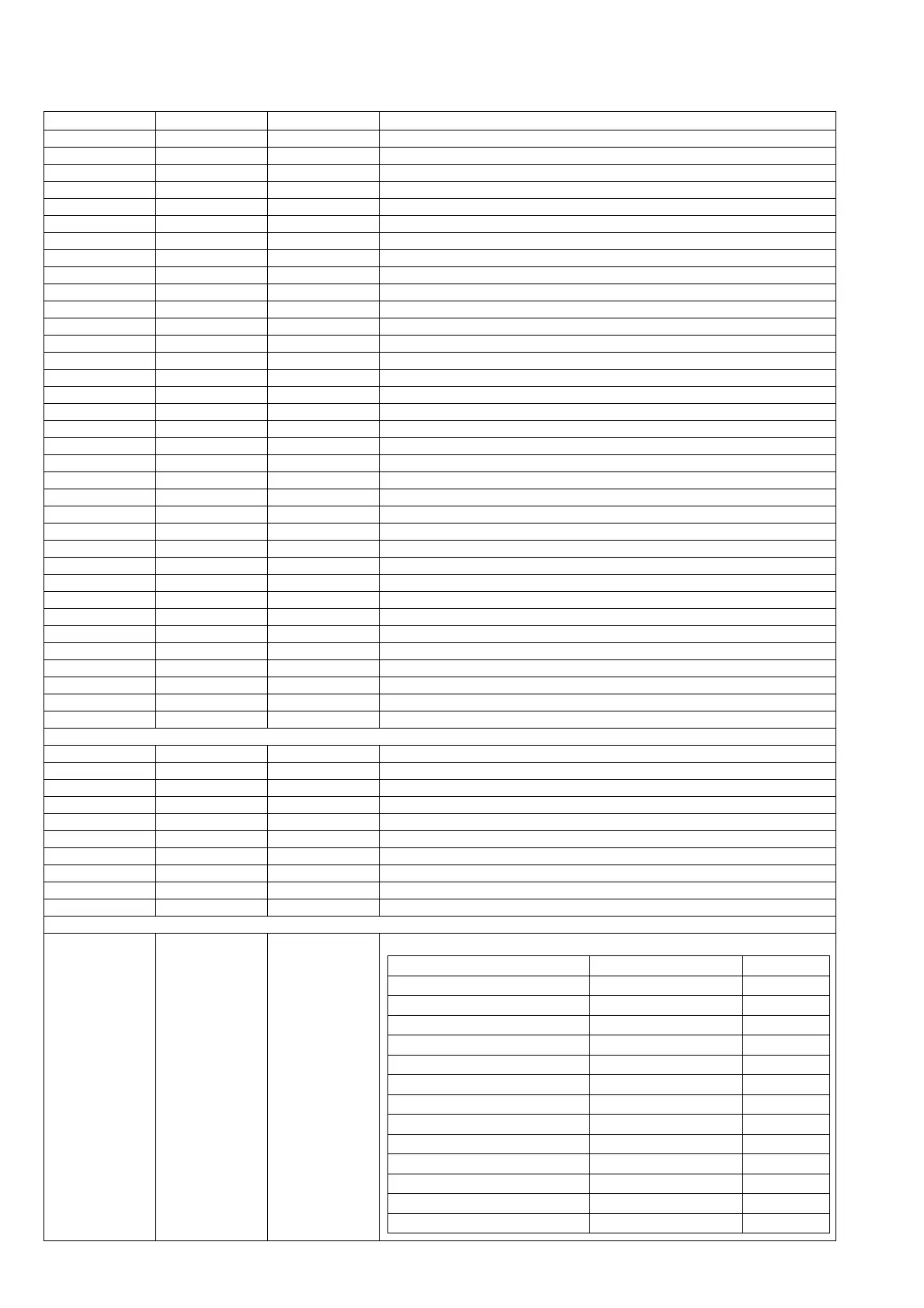

IC1 VHiSP8281AWU5 : DVD DECODER (SP8281) (3/3)

PIN DESCRIPTION

Symbol Pin # Input/Output Description

VSS_O0/VSS_K0 53 S Chip kernel logic and output shared ground pin #0

VSS_O1/VSS_K1 70 S (#1)

VSS_O2/VSS_K2 119 S (#2)

VSS_O2/VSS_K3 134 S (#3)

VSS_O2/VSS_K4 148 S (#4)

VSS_O2/VSS_K5 170 S (#5)

VSS_O2/VSS_K6 202 S (#6)

VSS_O2/VSS_K7 224 S (#7)

VDD_K0 66 S Kernel logic power supply pins for chip kernel logic and input pre-driver #0

VDD_K1 90 S (#1)

VDD_K2 125 S (#2)

VDD_K3 141 S (#3)

VDD_K4 163 S (#4)

VDD_K5 182 S (#5)

NC 45 S NC

VDD_O1 74 S Input/Output power supply pins #1

VDD_O2 96 S (#2)

VDD_O3 112 S (#3)

VDD_O4 132 S (#4)

VDD_O5 156 S (#5)

VDD_O6 177 S (#6)

VDD_O7 197 S (#7)

VDD_O8 234 S (#8)

USB_GND 99 S Ground pin for USB PLL

USB_VDD 100 S 3.3V power for USB PLL and USB transceiver

VSS_PLLA 103 S Ground pin for USB transceiver and audio PLL

VDD_PLLA 104 S 3.3V power supply pin for audio PLL

VSS_PLLV 105 S Ground pin for system PLL and audio PLL

VDD_PLLV 106 S 1.8V power supply pin for system PLL

VDD_TVA0 212 S 3.3V power supply pin for TV DAC

VDD_TVA1 216 S (#1)

VDD_TVA2 220 S (#2)

VSS_TVA0 213 S Ground pin for TV DAC

VSS_TVA1 217 S (#1)

VSS_TVA2 222 S (#2)

R_D7 46 Input/Output ROM / SRAM / flash data bus bit [7]

R_D6 47 Input/Output ROM / SRAM / flash data bus bit [6]

R_D5 48 Input/Output ROM / SRAM / flash data bus bit [5]

R_D4 49 Input/Output ROM / SRAM / flash data bus bit [4]

R_D3 50 Input/Output ROM / SRAM / flash data bus bit [3]

R_D2 51 Input/Output ROM / SRAM / flash data bus bit [2]

R_D1 52 Input/Output ROM / SRAM / flash data bus bit [1]

R_D0 54 Input/Output ROM / SRAM / flash data bus bit [0]

R_WE_B 55 Input/Output ROM / SRAM / flash write strobe

R_OE_B 56 Input/Output ROM / SRAM / flash output enable

SPDC_OUT/

GPIO

n/a Input/Output

Servo SPDC_OUT

Priority selection Function Dir

gpio_first[0][0] = 1

GPIO[0]

Input/Output

sft_cfg13[11:9] = 3'b010

AT_IORDY_B

Input

sft_cfg13[11:9] = 3'b011

AT_ADR[0]

Output

sft_cfg13[11:9] = 3'b101

AT_ADR[0]

Output

sft_cfg13[11:9] = 3'b110

AT_ADR[0]

Output

sft_cfg13[11:9] = 3'b111

AT_DIOW_B

Output

sft_cfg4[0] = 1

SPDC_OUT (default)

Input/Output

sft_cfg11[5:3] = 3'b001

EXT_TS_CLK

Input

sfg_cfg15[2:0] = 3'b010

FM_GPIOB[2]

Input/Output

sfg_cfg16[15:12] = 4'b0011

FM_GPIOB[16]

Input/Output

sfg_cfg18[3:0] = 4'b0101

FM_GPIOB[36]

Input/Output

sfg_cfg18[3:0] = 4'b0110

FM_GPIOB[36]

Input/Output

(other)

GPIO[0]

Input/Output

Loading...

Loading...