HT-DV40H

8 – 12

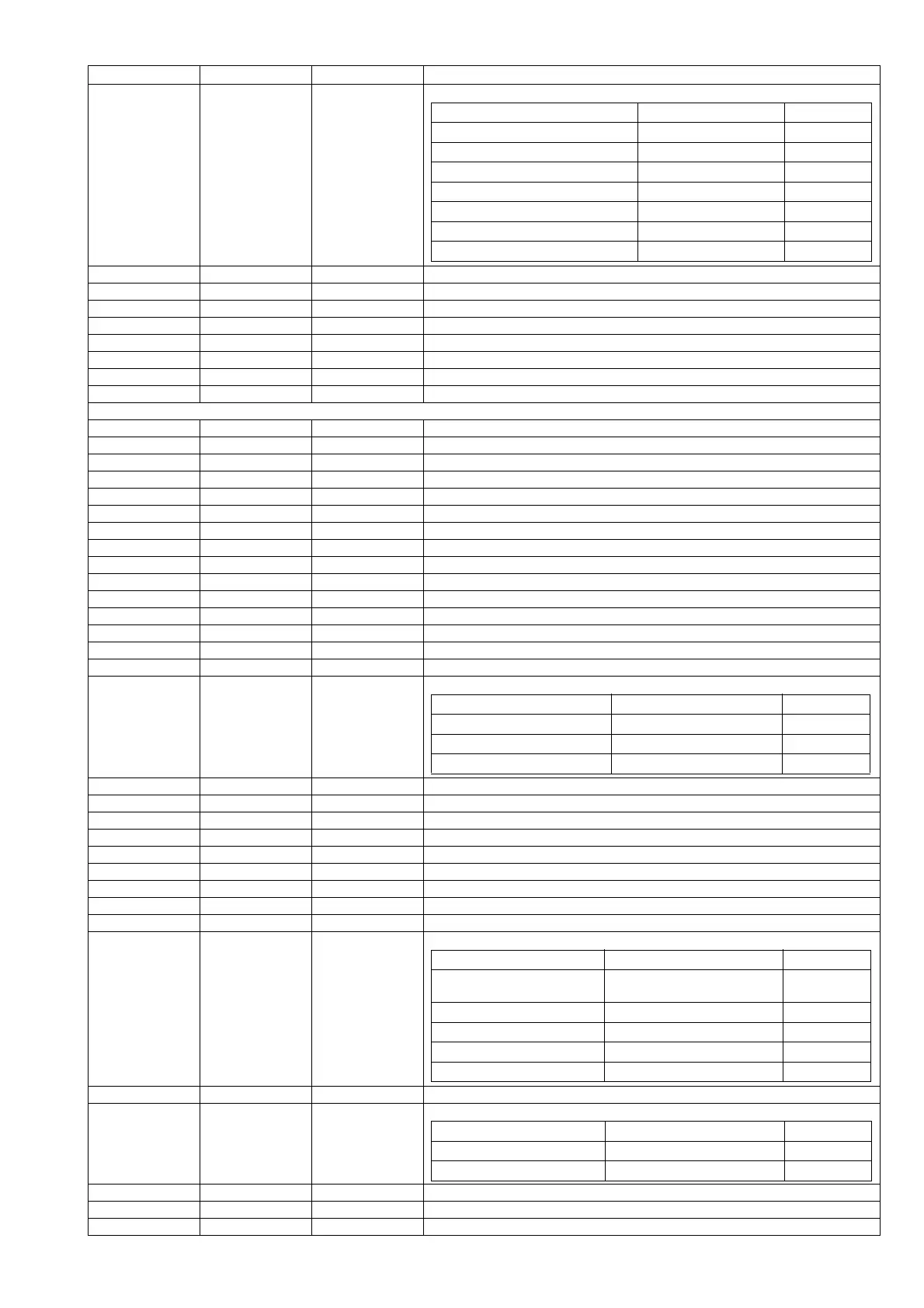

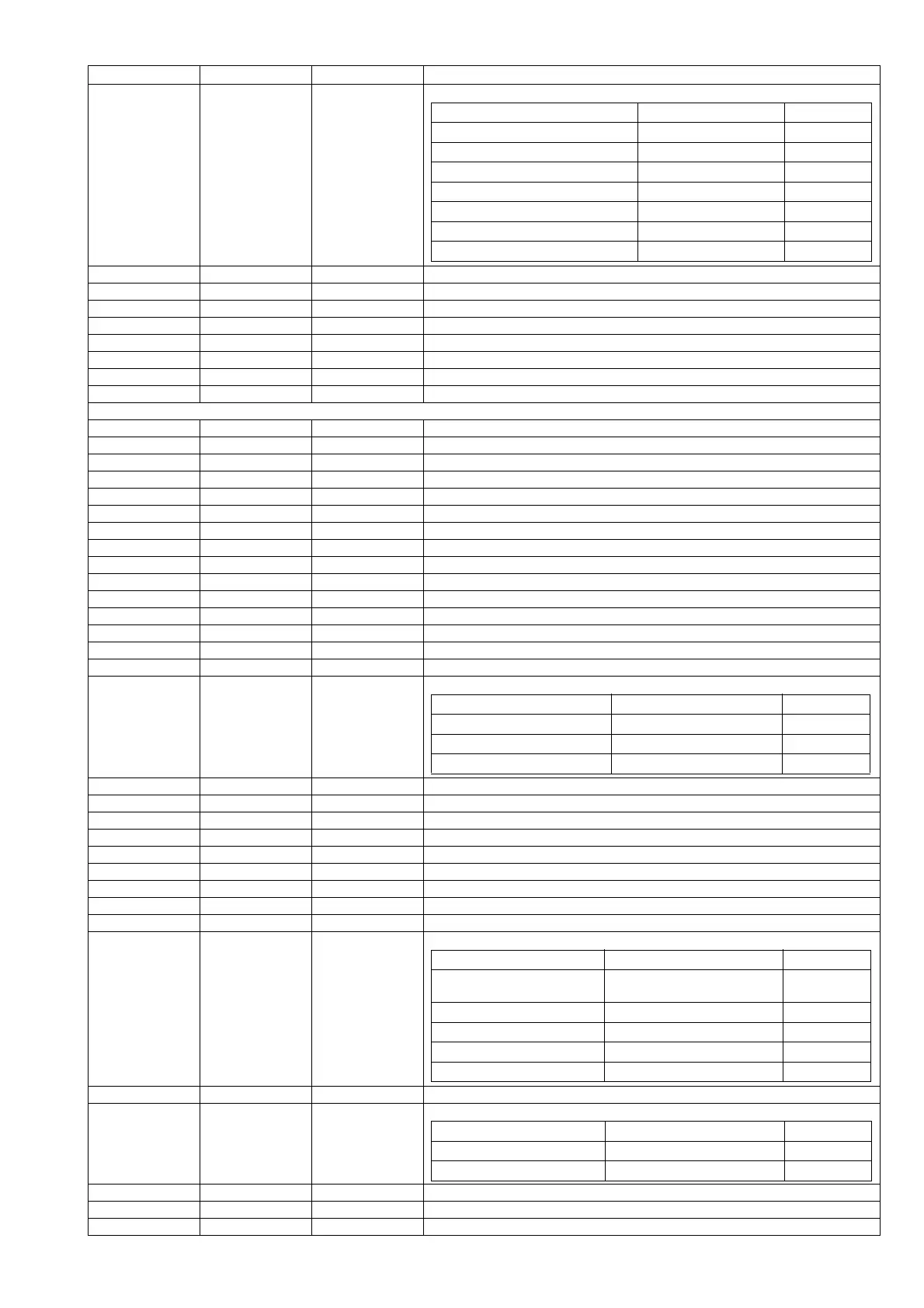

R_A19 86 Input/Output ROM / SRAM / flash address bus bit [19]

R_A18 87 Input/Output ROM / SRAM / flash address bus bit [18]

R_A17 88 Input/Output ROM / SRAM / flash address bus bit [17]

R_A16 89 Input/Output ROM / SRAM / flash address bus bit [16]

R_A15 91 Input/Output ROM / SRAM / flash address bus bit [15]

R_A14 92 Input/Output ROM / SRAM / flash address bus bit [14]

R_A13 93 Input/Output ROM / SRAM / flash address bus bit [13]

R_A12 94 Input/Output ROM / SRAM / flash address bus bit [12]

R_A11 95 Input/Output ROM / SRAM / flash address bus bit [11]

R_A11 97 Input Clock input / crystal in (XTALI)

R_A11 98 Output Clock output / crystal out (XTALO)

R_A11 101 Input/Output USB bus D+ (only for USB versions)

R_A11 102 Input/Output USB bus D- (only for USB versions)

R_A11 107 Input/Output SDRAM data bus [7]

R_A11 108 Input/Output SDRAM data bus [6]

R_A11 109 Input/Output SDRAM data bus [5]

R_A11 110 Input/Output SDRAM data bus [4]

R_A11 111 Input/Output SDRAM data bus [3]

R_A11 113 Input/Output SDRAM data bus [2]

R_A11 114 Input/Output SDRAM data bus [1]

R_A11 115 Input/Output SDRAM data bus [0]

R_A11 116 Input/Output SDRAM write enable / row precharge

R_A11 117 Input/Output SDRAM column address strobe

R_A11 118 Input/Output SDRAM row address strobe / precharge

M_CS0_B/GPIO 120 Input/Output SDRAM chip select 0, or GPIO[24]

M_BA0 121 Input/Output SDRAM bank select address [0]

M_DD[15] 122 Input/Output SDRAM data bus [15]

M_DD[14] 123 Input/Output SDRAM data bus [14]

M_DD[13] 124 Input/Output SDRAM data bus [13]

M_DD[12] 126 Input/Output SDRAM data bus [12]

M_DD[11] 127 Input/Output SDRAM data bus [11]

M_DD[10] 128 Input/Output SDRAM data bus [10]

M_DD[9] 129 Input/Output SDRAM data bus [9]

M_DD[8] 130 Input/Output SDRAM data bus [8]

M_A[11]/ GPIO 131 Input/Output SDRAM address bus [11] or GPIO[25]

M_CLKO 133 Output SDRAM clock output

M_CKE/GPIO 135 Input/Output SDRAM clock enable, or GPIO[26]

M_A[9] 136 Input/Output SDRAM address bus [9]

M_A[8] 137 Input/Output SDRAM address bus [8]

M_A[7] 138 Input/Output SDRAM address bus [7]

Symbol Pin # Input/Output Description

Priority selection Function Dir

gpio_first[4][9] = 1 GPIO[73]

Input/Output

PINMUX_control[0][0] = 1 ROM_ADDR[19](default)

Input/Output

sft_cfg1[11:9] = 3'b110 NT1_11

Input

sfg_cfg16[15:12] = 4'b1000 FM_GPIOB[15]

Input/Output

sfg_cfg18[3:0] = 4'b0001 FM_GPIOB[32]

Input/Output

sfg_cfg18[3:0] = 4'b0010 FM_GPIOB[32]

Input/Output

(other) GPIO[73]

Input/Output

Priority selection Function Dir

sft_cfg0[0]=1íb1 SDRAM chip select (default)

Output

gpio_first[1][8] = 1 GPIO[24]

Input/Output

(other) GPIO[24]

Input/Output

Priority selection Function Dir

sft_cfg1[4]=1íb1

SDRAM address bus M_A[11]

(default)

Output

gpio_first[1][9] = 1

I

GPIO[25]

Input/Output

sft_cfg13[3:0] = 4'b1001 IEC_RX

Input

sft_cfg13[8:4] = 5'b01010 ADC_DATA

Input

(other) GPIO[25]

Input/Output

Priority selection Function Dir

sft_cfg0[1]=1íb1 DRAM clock enable (default)

Output

(other) GPIO[26]

Input/Output

Loading...

Loading...